Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

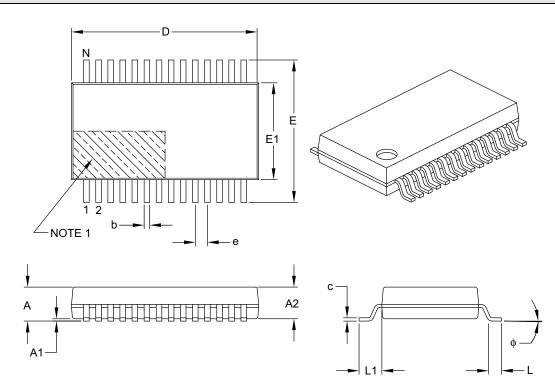

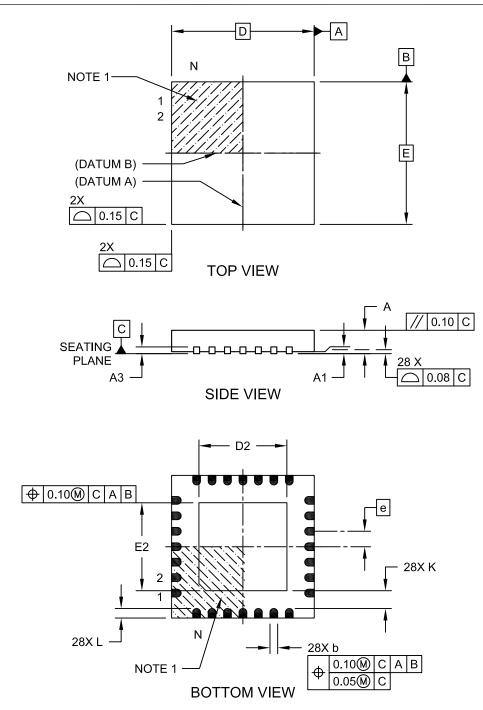

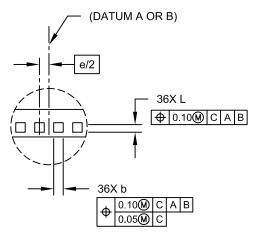

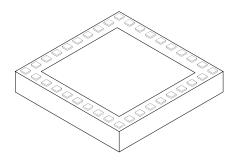

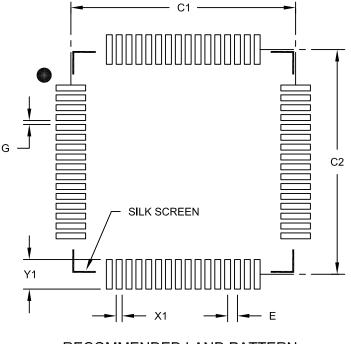

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202-e-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

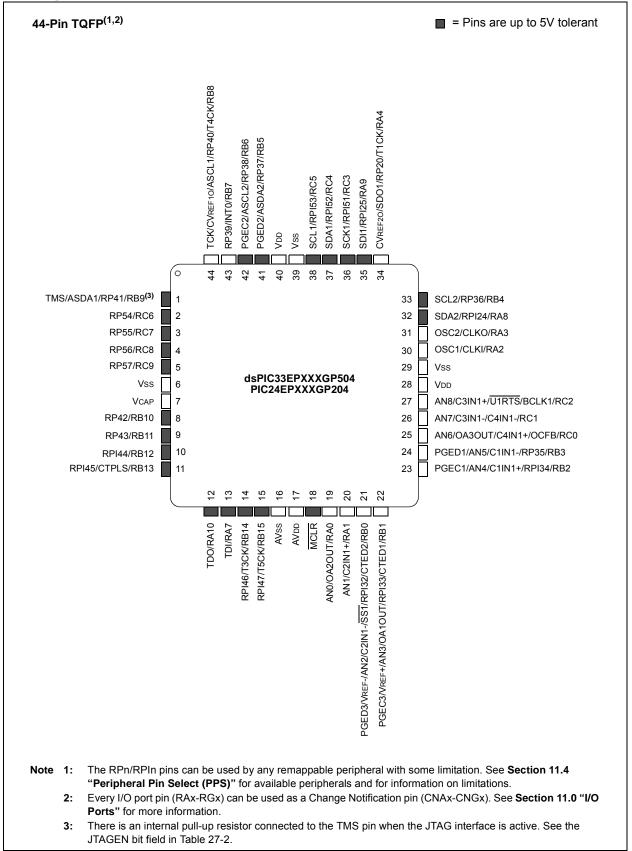

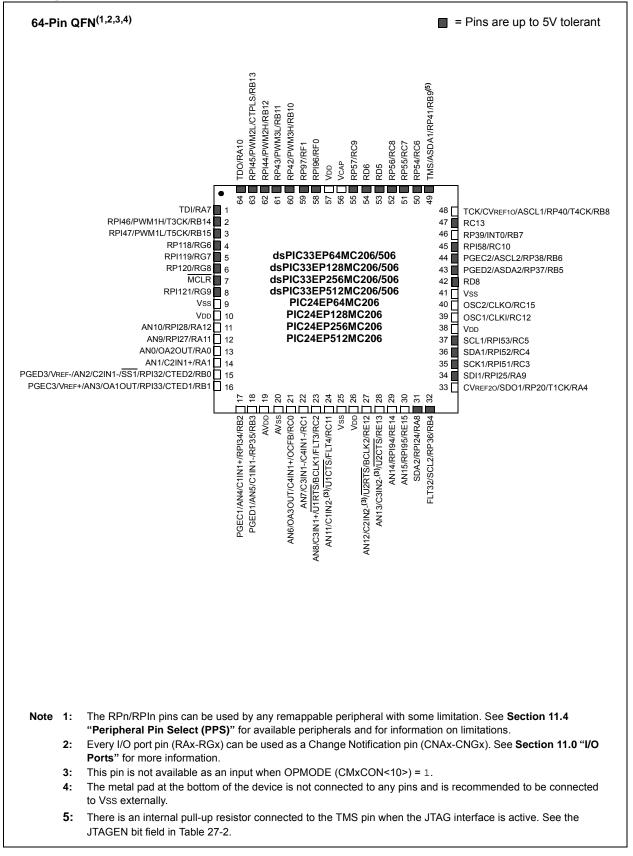

# **Pin Diagrams (Continued)**

# Pin Diagrams (Continued)

# 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: CI                                          | PU STATUS I                            | REGISTER                    |                          |                    |                   |               |

|------------------------|------------------------------------------------------|----------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|

| R/W-0                  | R/W-0                                                | R/W-0                                  | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                    | SA <sup>(1,4)</sup>                    | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |

| bit 15                 |                                                      |                                        |                             |                          |                    |                   | bit 8         |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                               | R/W-0 <sup>(2,3)</sup>                 | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |

| IPL2                   | IPL1                                                 | IPL0                                   | RA                          | N                        | OV                 | Z                 | С             |

| bit 7                  | ·                                                    | •                                      |                             | •                        |                    |                   | bit (         |

| Legend:                |                                                      | C = Clearable                          | e bit                       |                          |                    |                   |               |

| R = Readab             | le bit                                               | W = Writable                           | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |

| -n = Value a           | t POR                                                | '1'= Bit is set                        |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |

|                        |                                                      |                                        |                             |                          |                    |                   |               |

| bit 15                 | OA: Accumul                                          | ator A Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator A has over                        | flowed                      |                          |                    |                   |               |

|                        | 0 = Accumula                                         | ator A has not o                       | verflowed                   |                          |                    |                   |               |

| bit 14                 | OB: Accumul                                          | ator B Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator B has over                        | flowed                      |                          |                    |                   |               |

|                        |                                                      | ator B has not c                       |                             |                          |                    |                   |               |

| bit 13                 | SA: Accumul                                          | ator A Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        |                                                      | ator A is saturat<br>ator A is not sat |                             | en saturated at          | some time          |                   |               |

| bit 12                 | SB: Accumul                                          | ator B Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        | 1 = Accumula                                         | ator B is saturat<br>ator B is not sat | ted or has bee              |                          | some time          |                   |               |

| bit 11                 |                                                      | B Combined A                           |                             | vorflow Status           | ы#(1)              |                   |               |

|                        |                                                      | ators A or B have                      |                             | vernow Status            | DIL                |                   |               |

|                        |                                                      | ccumulators A                          |                             | erflowed                 |                    |                   |               |

| bit 10                 |                                                      | B Combined Ad                          |                             |                          | (1)                |                   |               |

|                        |                                                      |                                        |                             |                          | urated at some     | time              |               |

|                        | 0 = Neither A                                        | ccumulators A                          | or B are satur              | ated                     |                    |                   |               |

| bit 9                  | DA: DO Loop                                          | Active bit <sup>(1)</sup>              |                             |                          |                    |                   |               |

|                        | 1 = DO <b>loop is</b>                                | s in progress                          |                             |                          |                    |                   |               |

|                        | 0 = DO <b>loop</b> is                                | s not in progres                       | S                           |                          |                    |                   |               |

| bit 8                  | DC: MCU AL                                           | U Half Carry/Bo                        | orrow bit                   |                          |                    |                   |               |

|                        |                                                      | out from the 4th sult occurred         | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |

|                        | 0 = No carry                                         |                                        |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |

|                        | his bit is available                                 |                                        |                             |                          |                    |                   | -             |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1. |                                        |                             |                          |                    |                   |               |

### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

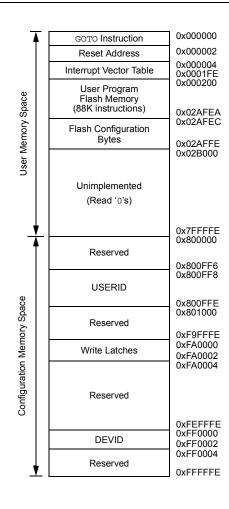

## FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

# TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      | -          | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name  | Addr          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7      | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|--------|--------|--------|--------|--------|--------|------------|------------|----------|--------|-------|-------|-------|--------|--------|---------------|

|            | 0400-<br>041E |        |        |        |        |        |        |        | See defini | ion when W | 'IN = x  |        |       |       |       |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BF   | P<3:0> |        |        | F2BI   | ><3:0> |            |            | F1BP     | <3:0>  |       |       | F0BP  | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BF   | ><3:0> |        |        | F6BI   | ><3:0> |            |            | F5BP     | <3:0>  |       |       | F4BP  | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11B   | P<3:0> |        |        | F10B   | P<3:0> |            |            | F9BP     | <3:0>  |       |       | F8BP  | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B   | P<3:0> |        |        | F14B   | P<3:0> |            |            | F13B     | D<3:0> |       |       | F12BF | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | MIDE  | _     | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXM1SID  | 0434          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | MIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXM2SID  | 0438          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | MIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF0SID  | 0440          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       | -      |        | xxxx          |

| C1RXF1SID  | 0444          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF2SID  | 0448          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF3SID  | 044C          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF4SID  | 0450          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF5SID  | 0454          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF6SID  | 0458          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF8SID  | 0460          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |        |        |        |        | :15:8> |        |        |            |            |          |        | EID<  | -     |       |        |        | xxxx          |

| C1RXF9SID  | 0464          |        |        |        |        | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |        |        |        |        | :15:8> |        |        |            |            |          |        | EID<  |       |       |        |        | xxxx          |

| C1RXF10SID | 0468          |        |        |        |        | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |        |        |        |        | :15:8> |        |        |            |            |          |        | EID<  | -     |       |        |        | xxxx          |

| C1RXF11SID | 046C          |        |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | -     | EID<   | 17:16> | xxxx          |

# TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4-2  | 23: E | CAN1 I                                                                                     | REGIST | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|--------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15                                                                                     | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  |                                                                                            |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF12SID | 0470  | SID<10:3>         SID<2:0>         —         EXIDE         —         EID<17:16>         :: |        |        |        |        |        |               |           | xxxx     |          |        |        |        |        |       |       |               |

| C1RXF12EID | 0472  | EID<15:8> EID<7:0> xx                                                                      |        |        |        |        |        |               |           | xxxx     |          |        |        |        |        |       |       |               |

| C1RXF13SID | 0474  |                                                                                            |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476  |                                                                                            |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF14SID | 0478  |                                                                                            |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A  |                                                                                            |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF15SID | 047C  |                                                                                            |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF15EID | 047E  |                                                                                            |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

# 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

# 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

# TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                        | R-0                                                                                                                                                                                                                                                                                                                                                       | R-0              | U-0               | R/W-y                        | R/W-y                | R/W-y                |  |  |  |  |

|----------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------------------|----------------------|----------------------|--|--|--|--|

| _              | COSC2                                      | COSC1                                                                                                                                                                                                                                                                                                                                                     | COSC0            | —                 | NOSC2 <sup>(2)</sup>         | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |  |  |

| bit 15         |                                            |                                                                                                                                                                                                                                                                                                                                                           |                  |                   |                              |                      | bit 8                |  |  |  |  |

| R/W-0          | R/W-0                                      | R-0                                                                                                                                                                                                                                                                                                                                                       | U-0              | R/W-0             | U-0                          | U-0                  | R/W-0                |  |  |  |  |

| CLKLOC         | CK IOLOCK                                  | LOCK                                                                                                                                                                                                                                                                                                                                                      |                  | CF <sup>(3)</sup> |                              |                      | OSWEN                |  |  |  |  |

| bit 7          |                                            |                                                                                                                                                                                                                                                                                                                                                           |                  |                   |                              |                      | bit (                |  |  |  |  |

| Legend:        |                                            | y = Value set                                                                                                                                                                                                                                                                                                                                             | from Configur    | ation bits on F   | POR                          |                      |                      |  |  |  |  |

| R = Reada      | able bit                                   | W = Writable                                                                                                                                                                                                                                                                                                                                              | -                |                   | mented bit, read             | l as '0'             |                      |  |  |  |  |

| -n = Value     | at POR                                     | '1' = Bit is se                                                                                                                                                                                                                                                                                                                                           | t                | '0' = Bit is cle  | eared                        | x = Bit is unkr      | nown                 |  |  |  |  |

| hit 1 <i>5</i> | Unimplemen                                 | ted. Dood oo                                                                                                                                                                                                                                                                                                                                              | 0'               |                   |                              |                      |                      |  |  |  |  |

| bit 15         | -                                          | ted: Read as                                                                                                                                                                                                                                                                                                                                              |                  |                   |                              |                      |                      |  |  |  |  |

| bit 14-12      |                                            | Current Oscill                                                                                                                                                                                                                                                                                                                                            |                  |                   | ()                           |                      |                      |  |  |  |  |

|                |                                            | C Oscillator (F<br>C Oscillator (F                                                                                                                                                                                                                                                                                                                        |                  |                   |                              |                      |                      |  |  |  |  |

|                |                                            | ower RC Oscil                                                                                                                                                                                                                                                                                                                                             |                  |                   |                              |                      |                      |  |  |  |  |

|                | 100 = Reserv                               |                                                                                                                                                                                                                                                                                                                                                           | ()               |                   |                              |                      |                      |  |  |  |  |

|                |                                            | y Oscillator (X                                                                                                                                                                                                                                                                                                                                           |                  | h PLL             |                              |                      |                      |  |  |  |  |

|                |                                            | y Oscillator (X                                                                                                                                                                                                                                                                                                                                           |                  |                   |                              |                      |                      |  |  |  |  |

|                |                                            | C Oscillator (F<br>C Oscillator (F                                                                                                                                                                                                                                                                                                                        |                  | le-by-N and Pl    | LL (FRCPLL)                  |                      |                      |  |  |  |  |

| bit 11         |                                            | ted: Read as                                                                                                                                                                                                                                                                                                                                              | ,                |                   |                              |                      |                      |  |  |  |  |

| bit 10-8       | NOSC<2:0>:                                 | New Oscillato                                                                                                                                                                                                                                                                                                                                             | r Selection bits | <sub>S</sub> (2)  |                              |                      |                      |  |  |  |  |

|                | 111 = Fast R                               | C Oscillator (F                                                                                                                                                                                                                                                                                                                                           | RC) with Divid   | le-by-n           |                              |                      |                      |  |  |  |  |

|                |                                            | C Oscillator (F                                                                                                                                                                                                                                                                                                                                           |                  | le-by-16          |                              |                      |                      |  |  |  |  |

|                |                                            | ower RC Oscil                                                                                                                                                                                                                                                                                                                                             | ator (LPRC)      |                   |                              |                      |                      |  |  |  |  |

|                | 100 = Reserv                               | /ed<br>y Oscillator (X                                                                                                                                                                                                                                                                                                                                    |                  |                   |                              |                      |                      |  |  |  |  |

|                |                                            | y Oscillator (X                                                                                                                                                                                                                                                                                                                                           |                  | IFLL              |                              |                      |                      |  |  |  |  |

|                |                                            | C Oscillator (F                                                                                                                                                                                                                                                                                                                                           |                  | le-by-N and Pl    | LL (FRCPLL)                  |                      |                      |  |  |  |  |

|                |                                            | C Oscillator (F                                                                                                                                                                                                                                                                                                                                           |                  | ,                 | ,                            |                      |                      |  |  |  |  |

| bit 7          |                                            | Clock Lock Ena                                                                                                                                                                                                                                                                                                                                            |                  |                   |                              |                      |                      |  |  |  |  |

|                |                                            |                                                                                                                                                                                                                                                                                                                                                           |                  | configurations    | are locked; if (F            | =CKSM0 = 0), t       | then clock and       |  |  |  |  |

|                |                                            | figurations may<br>d PLL selectio                                                                                                                                                                                                                                                                                                                         |                  | ked, configurat   | ions may be mo               | odified              |                      |  |  |  |  |

| bit 6          |                                            | Lock Enable b                                                                                                                                                                                                                                                                                                                                             |                  | -                 | -                            |                      |                      |  |  |  |  |

|                | 1 = I/O lock is                            | s active                                                                                                                                                                                                                                                                                                                                                  |                  |                   |                              |                      |                      |  |  |  |  |

|                | 0 = I/O lock is                            | s not active                                                                                                                                                                                                                                                                                                                                              |                  |                   |                              |                      |                      |  |  |  |  |

| bit 5          | LOCK: PLL L                                | ock Status bit                                                                                                                                                                                                                                                                                                                                            | (read-only)      |                   |                              |                      |                      |  |  |  |  |

|                |                                            | s that PLL is in<br>s that PLL is ou                                                                                                                                                                                                                                                                                                                      |                  |                   | satisfied<br>progress or PLL | is disabled          |                      |  |  |  |  |

| Note 1:        | Writes to this regis                       |                                                                                                                                                                                                                                                                                                                                                           |                  |                   |                              |                      | ʻdsPIC33/            |  |  |  |  |

| 2:             | Direct clock switch<br>This applies to clo | 4 Family Reference Manual" (available from the Microchip web site) for details.<br>t clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.<br>applies to clock switches in either direction. In these instances, the application must switch to FRC<br>as a transitional clock source between the two PLL modes. |                  |                   |                              |                      |                      |  |  |  |  |

| 0              | This bit should only                       |                                                                                                                                                                                                                                                                                                                                                           |                  |                   |                              |                      |                      |  |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

# 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

# 14.2 Input Capture Registers

# REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable b  | bit                |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

| U-0                 | U-0                                                                                           | U-0             | R/W-0                                 | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------|-----------------|---------------------------------------|----------------------|-----------------------------------------|----------------------|----------------------|--|--|--|

| —                   | —                                                                                             | _               | DISSCK                                | DISSDO               | MODE16                                  | SMP                  | CKE <sup>(1)</sup>   |  |  |  |

| bit 15              |                                                                                               |                 |                                       |                      |                                         |                      | bit                  |  |  |  |

|                     |                                                                                               |                 |                                       |                      |                                         |                      |                      |  |  |  |

| R/W-0               | R/W-0                                                                                         | R/W-0           | R/W-0                                 | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                           | MSTEN           | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup>                    | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |

| bit 7               |                                                                                               |                 |                                       |                      |                                         |                      | bit                  |  |  |  |

| Legend:             |                                                                                               |                 |                                       |                      |                                         |                      |                      |  |  |  |

| R = Readabl         | e bit                                                                                         | W = Writable    | bit                                   | U = Unimpler         | mented bit, read                        | l as '0'             |                      |  |  |  |

| -n = Value at       | POR                                                                                           | '1' = Bit is se | t                                     | '0' = Bit is cle     | ared                                    | x = Bit is unkr      | nown                 |  |  |  |

|                     |                                                                                               |                 |                                       |                      |                                         |                      |                      |  |  |  |

| bit 15-13           | Unimplemen                                                                                    | ted: Read as    | ʻ0'                                   |                      |                                         |                      |                      |  |  |  |

| bit 12              | DISSCK: Disa                                                                                  | able SCKx Pin   | bit (SPIx Mas                         | ter modes only       | /)                                      |                      |                      |  |  |  |

|                     | 1 = Internal S                                                                                | Plx clock is di | sabled, pin fun                       | ctions as I/O        | -                                       |                      |                      |  |  |  |

|                     | 0 = Internal S                                                                                | PIx clock is er | nabled                                |                      |                                         |                      |                      |  |  |  |

| bit 11              | DISSDO: Dis                                                                                   | able SDOx Pir   | n bit                                 |                      |                                         |                      |                      |  |  |  |

|                     |                                                                                               |                 | y the module; p                       | oin functions as     | s I/O                                   |                      |                      |  |  |  |

|                     |                                                                                               | is controlled b | •                                     |                      |                                         |                      |                      |  |  |  |

| bit 10              | <b>MODE16:</b> Word/Byte Communication Select bit<br>1 = Communication is word-wide (16 bits) |                 |                                       |                      |                                         |                      |                      |  |  |  |

|                     | 1 = Communication is word-wide (16 bits)<br>0 = Communication is byte-wide (8 bits)           |                 |                                       |                      |                                         |                      |                      |  |  |  |

| bit 9               |                                                                                               | ata Input Sam   | . ,                                   |                      |                                         |                      |                      |  |  |  |

|                     | Master mode                                                                                   |                 | pie i nase bit                        |                      |                                         |                      |                      |  |  |  |

|                     |                                                                                               | -               | t end of data o                       | utput time           |                                         |                      |                      |  |  |  |

|                     |                                                                                               |                 | t middle of data                      |                      |                                         |                      |                      |  |  |  |

|                     | Slave mode:                                                                                   |                 |                                       |                      |                                         |                      |                      |  |  |  |

|                     |                                                                                               |                 | SPIx is used i                        | n Slave mode.        |                                         |                      |                      |  |  |  |

| bit 8               |                                                                                               | lock Edge Sele  |                                       |                      |                                         |                      |                      |  |  |  |

|                     |                                                                                               |                 |                                       |                      | clock state to lo<br>ock state to activ |                      |                      |  |  |  |

| bit 7               |                                                                                               |                 | bit (Slave mo                         |                      |                                         |                      |                      |  |  |  |

|                     |                                                                                               | s used for Slav |                                       |                      |                                         |                      |                      |  |  |  |

|                     |                                                                                               |                 |                                       | is controlled b      | by port function                        |                      |                      |  |  |  |

| bit 6               |                                                                                               | Polarity Select |                                       |                      |                                         |                      |                      |  |  |  |

|                     |                                                                                               |                 | nigh level; activ<br>ow level; active |                      |                                         |                      |                      |  |  |  |

| bit 5               |                                                                                               | ter Mode Enal   |                                       | C                    |                                         |                      |                      |  |  |  |

|                     | 1 = Master m                                                                                  | ode             |                                       |                      |                                         |                      |                      |  |  |  |

|                     | 0 = Slave mo                                                                                  | de              |                                       |                      |                                         |                      |                      |  |  |  |

| Note 1: T           | he CKE bit is not                                                                             | used in Frame   | d SPI modes I                         | Program this hi      | it to '0' for Fram                      | ed SPI modes (       | FRMEN = <sup>-</sup> |  |  |  |

|                     | his bit must be cl                                                                            |                 |                                       |                      |                                         |                      |                      |  |  |  |

| <u> </u>            |                                                                                               |                 |                                       |                      |                                         |                      |                      |  |  |  |

# REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|              | ( •                   | ,_, ., ., .,                     | -,-,-,                         |                  |                  |                 |                 |

|--------------|-----------------------|----------------------------------|--------------------------------|------------------|------------------|-----------------|-----------------|

| R/W-0        | R-0                   | R-0                              | R-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |

| TXENn        | TXABTn                | TXLARBn                          | TXERRn                         | TXREQn           | RTRENn           | TXnPRI1         | TXnPRI0         |

| bit 15       |                       |                                  |                                |                  |                  |                 | bit 8           |

| R/W-0        | R-0                   | R-0                              | R-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |

| TXENm        | TXABTm <sup>(1)</sup> | TXLARBm <sup>(1)</sup>           | TXERRm <sup>(1)</sup>          | TXREQm           | RTRENm           | TXmPRI1         | TXmPRI0         |

| bit 7        |                       |                                  | •                              |                  |                  |                 | bit 0           |

| Legend:      |                       |                                  |                                |                  |                  |                 |                 |

| R = Readab   | le bit                | W = Writable                     | bit                            | U = Unimpler     | mented bit, read | d as '0'        |                 |

| -n = Value a | t POR                 | '1' = Bit is set                 |                                | '0' = Bit is cle | ared             | x = Bit is unki | nown            |

| bit 15-8     | See Definitio         | n for bits<7:0>,                 | Controls Buffe                 | ar n             |                  |                 |                 |

| bit 7        |                       | RX Buffer Sele                   |                                | 51 11            |                  |                 |                 |

|              |                       | Ren is a transm                  |                                |                  |                  |                 |                 |

|              |                       | RBn is a receive                 |                                |                  |                  |                 |                 |

| bit 6        | TXABTm: M             | essage Aborteo                   | d bit <sup>(1)</sup>           |                  |                  |                 |                 |

|              | 1 = Message           |                                  |                                |                  |                  |                 |                 |

|              | 0 = Message           | completed tran                   | nsmission succ                 | cessfully        |                  |                 |                 |

| bit 5        | TXLARBm: N            | Message Lost A                   | Arbitration bit <sup>(1)</sup> | )                |                  |                 |                 |

|              |                       | lost arbitration did not lose ar |                                |                  |                  |                 |                 |