Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202-e-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

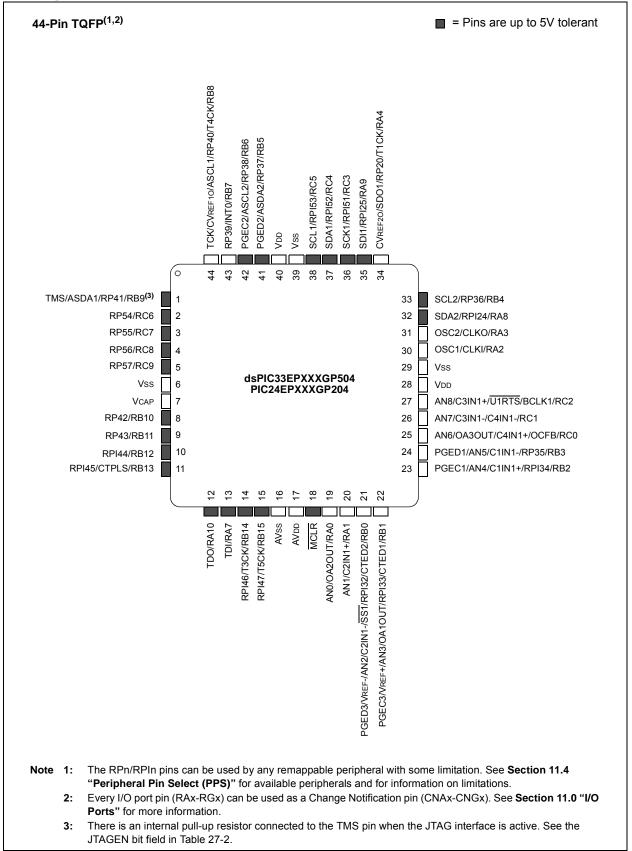

### **Pin Diagrams (Continued)**

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

# 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

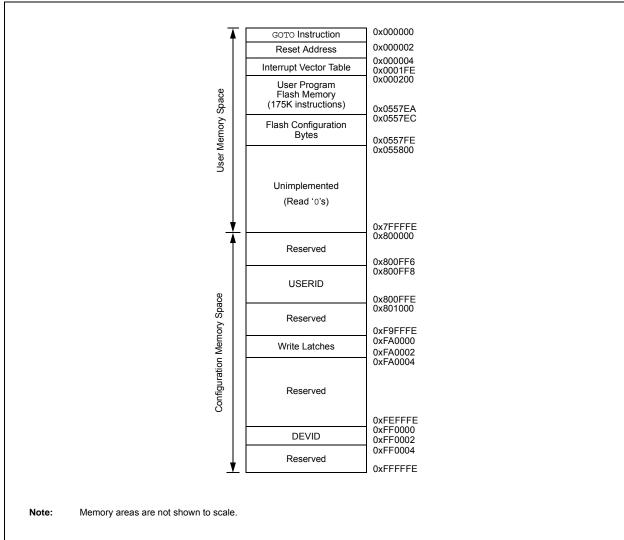

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

# TABLE 4-20: ADC1 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14               | Bit 13             | Bit 12             | Bit 11 | Bit 10     | Bit 9   | Bit 8        | Bit 7    | Bit 6    | Bit 5    | Bit 4     | Bit 3  | Bit 2    | Bit 1  | Bit 0   | All<br>Resets |

|-----------|-------|--------|----------------------|--------------------|--------------------|--------|------------|---------|--------------|----------|----------|----------|-----------|--------|----------|--------|---------|---------------|

| ADC1BUF0  | 0300  |        |                      |                    |                    |        |            |         | ADC1 Data B  | uffer 0  |          |          |           |        |          |        |         | xxxx          |

| ADC1BUF1  | 0302  |        |                      |                    |                    |        |            |         | ADC1 Data B  | uffer 1  |          |          |           |        |          |        |         | xxxx          |

| ADC1BUF2  | 0304  |        |                      |                    |                    |        |            |         | ADC1 Data B  | uffer 2  |          |          |           |        |          |        |         | xxxx          |

| ADC1BUF3  | 0306  |        |                      |                    |                    |        |            |         | ADC1 Data B  | uffer 3  |          |          |           |        |          |        |         | xxxx          |

| ADC1BUF4  | 0308  |        | ADC1 Data Buffer 4   |                    |                    |        |            |         |              |          |          | xxxx     |           |        |          |        |         |               |

| ADC1BUF5  | 030A  |        |                      | ADC1 Data Buffer 5 |                    |        |            |         |              |          |          |          |           | xxxx   |          |        |         |               |

| ADC1BUF6  | 030C  |        |                      |                    | ADC1 Data Buffer 6 |        |            |         |              |          |          |          | xxxx      |        |          |        |         |               |

| ADC1BUF7  | 030E  |        |                      |                    |                    |        |            |         | ADC1 Data B  | uffer 7  |          |          |           |        |          |        |         | xxxx          |

| ADC1BUF8  | 0310  |        |                      |                    |                    |        |            |         | ADC1 Data B  | uffer 8  |          |          |           |        |          |        |         | xxxx          |

| ADC1BUF9  | 0312  |        | ADC1 Data Buffer 9 x |                    |                    |        |            |         |              |          |          | xxxx     |           |        |          |        |         |               |

| ADC1BUFA  | 0314  |        |                      |                    |                    |        |            |         | ADC1 Data Bu | Iffer 10 |          |          |           |        |          |        |         | xxxx          |

| ADC1BUFB  | 0316  |        |                      |                    |                    |        |            |         | ADC1 Data Bu | uffer 11 |          |          |           |        |          |        |         | xxxx          |

| ADC1BUFC  | 0318  |        |                      |                    |                    |        |            |         | ADC1 Data Bu | Iffer 12 |          |          |           |        |          |        |         | xxxx          |

| ADC1BUFD  | 031A  |        |                      |                    |                    |        |            |         | ADC1 Data Bu | Iffer 13 |          |          |           |        |          |        |         | xxxx          |

| ADC1BUFE  | 031C  |        |                      |                    |                    |        |            |         | ADC1 Data Bu | Iffer 14 |          |          |           |        |          |        |         | xxxx          |

| ADC1BUFF  | 031E  |        |                      |                    |                    |        |            |         | ADC1 Data Bu | iffer 15 |          |          |           |        |          |        |         | xxxx          |

| AD1CON1   | 0320  | ADON   | _                    | ADSIDL             | ADDMABM            | _      | AD12B      | FOR     | M<1:0>       | Ş        | SRC<2:0> | <b>`</b> | SSRCG     | SIMSAM | ASAM     | SAMP   | DONE    | 0000          |

| AD1CON2   | 0322  | ١      | VCFG<2:0>            | >                  | _                  | _      | CSCNA      | CHP     | S<1:0>       | BUFS     |          |          | SMPI<4:0> | >      |          | BUFM   | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _                    | _                  |                    |        | SAMC<4:03  | >       |              |          |          |          | ADCS      | <7:0>  |          |        |         | 0000          |

| AD1CHS123 | 0326  | _      | _                    | _                  | _                  | _      | CH123N     | NB<1:0> | CH123SB      | —        | _        | —        | _         | _      | CH123N   | A<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  | _                    | _                  |                    |        | CH0SB<4:0> |         |              | CH0NA    | _        | —        |           | С      | H0SA<4:0 | 0000   |         |               |

| AD1CSSH   | 032E  | CSS31  | CSS30                | _                  | _                  |        | CSS26      | CSS25   | CSS24        | _        |          | _        | —         | —      | —        | —      | —       | 0000          |

| AD1CSSL   | 0330  | CSS15  | CSS14                | CSS13              | CSS12              | CSS11  | CSS10      | CSS9    | CSS8         | CSS7     | CSS6     | CSS5     | CSS4      | CSS3   | CSS2     | CSS1   | CSS0    | 0000          |

| AD1CON4   | 0332  |        | _                    | _                  | ADDMAEN DMABL<2:0> |        |            |         |              |          | )>       | 0000     |           |        |          |        |         |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | —      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | -     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      |        | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | —      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

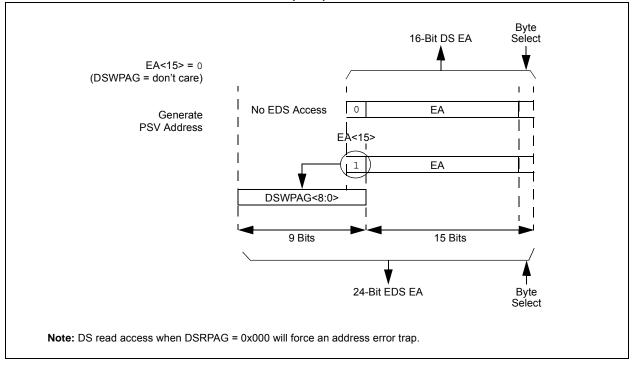

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |  |

|--------|-----|------------|-------|-------|--------|-------|-------|--|--|

| —      | —   |            |       | RP43  | R<5:0> |       |       |  |  |

| bit 15 |     |            |       |       |        |       | bit 8 |  |  |

|        |     |            |       |       |        |       |       |  |  |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |  |

| —      | —   | RP42R<5:0> |       |       |        |       |       |  |  |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP54  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

## 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 15.2 Output Compare Control Registers

# REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                                                                                                                                   | R/W-0                                  | R/W-0             | R/W-0             | R/W-0                  | U-0              | R/W-0         |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|-------------------|------------------------|------------------|---------------|

|               | 0-0                                                                                                                                   | OCSIDL                                 | OCTSEL2           | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |

| <br>bit 15    |                                                                                                                                       | COOIDE                                 |                   | OUTOLLI           | OUTOLLU                |                  | bit 8         |

| Sit 10        |                                                                                                                                       |                                        |                   |                   |                        |                  | bit 0         |

| R/W-0         | U-0                                                                                                                                   | R/W-0, HSC                             | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |

| ENFLT         |                                                                                                                                       | OCFLTB                                 | OCFLTA            | TRIGMODE          | OCM2                   | OCM1             | OCM0          |

| bit 7         |                                                                                                                                       |                                        |                   |                   |                        |                  | bit 0         |

|               |                                                                                                                                       |                                        |                   |                   |                        |                  |               |

| Legend:       |                                                                                                                                       | HSC = Hardw                            | are Settable/Cl   | earable bit       |                        |                  |               |

| R = Read      | able bit                                                                                                                              | W = Writable I                         | oit               | U = Unimplem      | nented bit, read       | as '0'           |               |

| -n = Value    | e at POR                                                                                                                              | '1' = Bit is set                       |                   | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |

|               |                                                                                                                                       |                                        |                   |                   |                        |                  |               |

| bit 15-14     | Unimplemen                                                                                                                            | ted: Read as 'o                        | )'                |                   |                        |                  |               |

| bit 13        | OCSIDL: Out                                                                                                                           | tput Compare x                         | Stop in Idle Mo   | de Control bit    |                        |                  |               |

|               |                                                                                                                                       | ompare x Halts                         |                   |                   |                        |                  |               |

|               | •                                                                                                                                     | compare x conti                        | •                 |                   | ode                    |                  |               |

| bit 12-10     |                                                                                                                                       | )>: Output Com                         | pare x Clock S    | elect bits        |                        |                  |               |

|               | 111 = Periph<br>110 = Reserv                                                                                                          | eral clock (FP)                        |                   |                   |                        |                  |               |

|               | 101 = PTGO                                                                                                                            |                                        |                   |                   |                        |                  |               |

|               |                                                                                                                                       | is the clock so                        |                   |                   | hronous clock          | is supported)    |               |

|               |                                                                                                                                       | is the clock so                        |                   |                   |                        |                  |               |

|               |                                                                                                                                       | ( is the clock so<br>( is the clock so |                   |                   |                        |                  |               |

|               |                                                                                                                                       | is the clock so                        |                   |                   |                        |                  |               |

| bit 9         | Unimplemen                                                                                                                            | ted: Read as '0                        | )'                |                   |                        |                  |               |

| bit 8         | ENFLTB: Fau                                                                                                                           | ult B Input Enab                       | le bit            |                   |                        |                  |               |

|               |                                                                                                                                       | compare Fault B<br>compare Fault B     |                   |                   |                        |                  |               |

| bit 7         | -                                                                                                                                     | ult A Input Enab                       |                   |                   |                        |                  |               |

|               | 1 = Output C                                                                                                                          | ompare Fault A<br>compare Fault A      | input (OCFA)      |                   |                        |                  |               |

| bit 6         | •                                                                                                                                     | ted: Read as '0                        | • • •             |                   |                        |                  |               |

| bit 5         | OCFLTB: PW                                                                                                                            | M Fault B Con                          | dition Status bit |                   |                        |                  |               |

|               |                                                                                                                                       | ult B condition of Fault B condition   |                   |                   |                        |                  |               |

| bit 4         | OCFLTA: PWM Fault A Condition Status bit                                                                                              |                                        |                   |                   |                        |                  |               |

|               | <ul> <li>1 = PWM Fault A condition on OCFA pin has occurred</li> <li>0 = No PWM Fault A condition on OCFA pin has occurred</li> </ul> |                                        |                   |                   |                        |                  |               |

| Note 1:       | OCxR and OCxF                                                                                                                         | 29 are double h                        | uffered in D\\//  | / mode only       |                        |                  |               |

| Note 1.<br>2: | Each Output Cor                                                                                                                       |                                        |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |

| 2.            | Generator (PTG                                                                                                                        |                                        |                   |                   |                        | 5.1 2 7.0 1 611p |               |

|               | PTGO4 = OC1                                                                                                                           | -                                      |                   |                   |                        |                  |               |

|               | PTGO5 = OC2                                                                                                                           |                                        |                   |                   |                        |                  |               |

|               | PTGO6 = OC3<br>PTGO7 = OC4                                                                                                            |                                        |                   |                   |                        |                  |               |

|               |                                                                                                                                       |                                        |                   |                   |                        |                  |               |

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

| U-0          | U-0                                          | R-0                        | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

|--------------|----------------------------------------------|----------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| _            |                                              | FBP5                       | FBP4           | FBP3              | FBP2             | FBP1            | FBP0  |  |  |  |  |

| bit 15       |                                              |                            |                |                   |                  |                 | bit 8 |  |  |  |  |

|              |                                              |                            |                |                   |                  |                 |       |  |  |  |  |

| U-0          | U-0                                          | R-0                        | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

|              |                                              | FNRB5                      | FNRB4          | FNRB3             | FNRB2            | FNRB1           | FNRB0 |  |  |  |  |

| bit 7        |                                              |                            |                |                   |                  |                 | bit ( |  |  |  |  |

| Legend:      |                                              |                            |                |                   |                  |                 |       |  |  |  |  |

| R = Readab   | le bit                                       | W = Writable               | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                        | '1' = Bit is set           |                | '0' = Bit is clea |                  | x = Bit is unkr | iown  |  |  |  |  |

|              |                                              |                            |                |                   |                  |                 |       |  |  |  |  |

| bit 15-14    | Unimpleme                                    | ented: Read as '           | 0'             |                   |                  |                 |       |  |  |  |  |

| bit 13-8     | FBP<5:0>: FIFO Buffer Pointer bits           |                            |                |                   |                  |                 |       |  |  |  |  |

|              | 011111 = RB31 buffer                         |                            |                |                   |                  |                 |       |  |  |  |  |

|              | 011110 <b>= F</b>                            | RB30 buffer                |                |                   |                  |                 |       |  |  |  |  |

|              | •                                            |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                            |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                            |                            |                |                   |                  |                 |       |  |  |  |  |

|              | 000001 = TRB1 buffer<br>000000 = TRB0 buffer |                            |                |                   |                  |                 |       |  |  |  |  |

| bit 7-6      | Unimpleme                                    | ented: Read as '           | 0'             |                   |                  |                 |       |  |  |  |  |

| bit 5-0      | FNRB<5:0                                     | >: FIFO Next Rea           | ad Buffer Poir | iter bits         |                  |                 |       |  |  |  |  |

|              | 011111 <b>= F</b>                            | RB31 buffer                |                |                   |                  |                 |       |  |  |  |  |

|              | 011110 <b>= F</b>                            | RB30 buffer                |                |                   |                  |                 |       |  |  |  |  |

|              | •                                            |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                            |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                            |                            |                |                   |                  |                 |       |  |  |  |  |

|              |                                              |                            |                |                   |                  |                 |       |  |  |  |  |

|              |                                              | FRB1 buffer<br>FRB0 buffer |                |                   |                  |                 |       |  |  |  |  |

#### REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

## 22.2 CTMU Control Registers

| REGISTER 2                                                                               | 22-1: CTM                                                                                                                                                    | UCON1: CTMU      | J CONTROL | REGISTER          | 1                |                        |        |  |  |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|-------------------|------------------|------------------------|--------|--|--|

| R/W-0                                                                                    | U-0                                                                                                                                                          | R/W-0            | R/W-0     | R/W-0             | R/W-0            | R/W-0                  | R/W-0  |  |  |

| CTMUEN                                                                                   | _                                                                                                                                                            | CTMUSIDL         | TGEN      | EDGEN             | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |  |

| bit 15                                                                                   |                                                                                                                                                              |                  |           |                   |                  |                        | bit 8  |  |  |

|                                                                                          |                                                                                                                                                              |                  |           |                   |                  |                        |        |  |  |

| U-0                                                                                      | U-0                                                                                                                                                          | U-0              | U-0       | U-0               | U-0              | U-0                    | U-0    |  |  |

|                                                                                          |                                                                                                                                                              | —                | _         |                   | <u> </u>         |                        | _      |  |  |

| bit 7                                                                                    |                                                                                                                                                              |                  |           |                   |                  |                        | bit 0  |  |  |

|                                                                                          |                                                                                                                                                              |                  |           |                   |                  |                        |        |  |  |

| Legend:                                                                                  |                                                                                                                                                              |                  |           |                   |                  |                        |        |  |  |

| R = Readable                                                                             | e bit                                                                                                                                                        | W = Writable b   | oit       | U = Unimplen      | nented bit, read | as '0'                 |        |  |  |

| -n = Value at                                                                            | POR                                                                                                                                                          | '1' = Bit is set |           | '0' = Bit is clea | ared             | x = Bit is unknown     |        |  |  |

| bit 15 <b>CTMUEN:</b> CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled |                                                                                                                                                              |                  |           |                   |                  |                        |        |  |  |

| bit 14                                                                                   | bit 14 Unimplemented: Read as '0'                                                                                                                            |                  |           |                   |                  |                        |        |  |  |

| bit 13                                                                                   | bit 13 CTMUSIDL: CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                  |           |                   |                  |                        |        |  |  |

| bit 12                                                                                   | TGEN: Time Generation Enable bit                                                                                                                             |                  |           |                   |                  |                        |        |  |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

| DC CHARACTERISTICS |           |                                                                     | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |      |      |       |                 |  |

|--------------------|-----------|---------------------------------------------------------------------|----------------------------------------------------------|------|------|-------|-----------------|--|

| Param<br>No.       | Symbol    | Characteristic                                                      | Min.                                                     | Тур. | Max. | Units | Conditions      |  |

| Operati            | ng Voltag | e                                                                   |                                                          |      |      |       |                 |  |

| DC10               | Vdd       | Supply Voltage                                                      | 3.0                                                      |      | 3.6  | V     |                 |  |

| DC16               | VPOR      | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | -                                                        | _    | Vss  | V     |                 |  |

| DC17               | Svdd      | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.03                                                     | _    | —    | V/ms  | 0V-1V in 100 ms |  |

#### TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

## TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

|                                     | Standard Operating Conditions (unless otherwise stated):Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                   |     |      |      |       |                                                       |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|------|-------|-------------------------------------------------------|--|--|

| Param<br>No. Symbol Characteristics |                                                                                                                                                                                          |                                                   |     | Тур. | Max. | Units | Comments                                              |  |  |

|                                     | Cefc                                                                                                                                                                                     | External Filter Capacitor<br>Value <sup>(1)</sup> | 4.7 | 10   |      | μF    | Capacitor must have a low series resistance (< 1 Ohm) |  |  |

**Note 1:** Typical VCAP voltage = 1.8 volts when VDD  $\geq$  VDDMIN.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

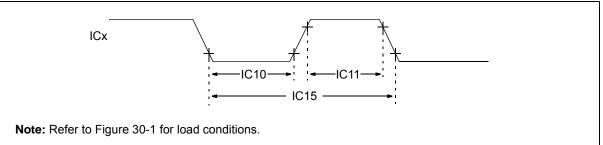

## FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                  |      |                     | Standard Operati<br>(unless otherwise<br>Operating tempera | e stated | )<br>∙40°C ≤ <sup>-</sup> | <b>3.0V to 3.6V</b><br>「A ≤ +85°C for Indu<br>「A ≤ +125°C for Ext |                                  |  |

|-----------------------------------------------------|------|---------------------|------------------------------------------------------------|----------|---------------------------|-------------------------------------------------------------------|----------------------------------|--|

| Param.<br>No. Symbol Characteristics <sup>(1)</sup> |      |                     | Min.                                                       | Max.     | Units                     | Conditions                                                        |                                  |  |

| IC10                                                | TccL | ICx Input Low Time  | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25             |          | ns                        | Must also meet<br>Parameter IC15                                  |                                  |  |

| IC11                                                | ТссН | ICx Input High Time | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25             | —        | ns                        | Must also meet<br>Parameter IC15                                  | N = prescale value<br>(1, 4, 16) |  |

| IC15                                                | TccP | ICx Input Period    | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50              | _        | ns                        |                                                                   |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

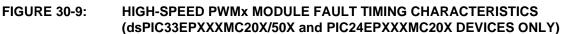

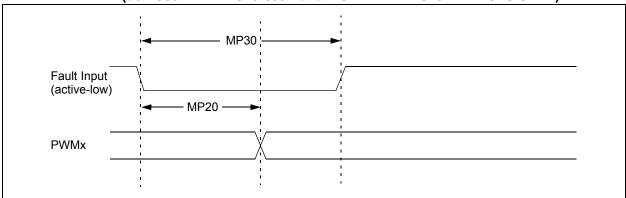

#### FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                    |

|--------------------|--------|-------------------------------------|-------------------------------------------------------|------|------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min.                                                  | Тур. | Max. | Units | Conditions         |

| MP10               | TFPWM  | PWMx Output Fall Time               |                                                       | —    | _    | ns    | See Parameter DO32 |

| MP11               | TRPWM  | PWMx Output Rise Time               | _                                                     | —    | _    | ns    | See Parameter DO31 |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                     | _    | 15   | ns    |                    |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                    | _    | _    | ns    |                    |

**Note 1:** These parameters are characterized but not tested in manufacturing.

# 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to 5.5V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(4)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                    | 10 mA                |

| Maximum current sourced/sunk by any 8x I/O pin                                    | 15 mA                |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(4)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Refer to the "Pin Diagrams" section for 5V tolerant pins.

- 4: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

| AC CHARACTERISTICS                               |        |                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |     |     |       |                                                  |  |  |

|--------------------------------------------------|--------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------------------------------------|--|--|

| Param<br>No.                                     | Symbol | Characteristic            | Min                                                                                                                                    | Тур | Max | Units | Conditions                                       |  |  |

| ADC Accuracy (12-Bit Mode) <sup>(1)</sup>        |        |                           |                                                                                                                                        |     |     |       |                                                  |  |  |

| HAD20a                                           | Nr     | Resolution <sup>(3)</sup> | 12 Data Bits                                                                                                                           |     |     | bits  |                                                  |  |  |

| HAD21a                                           | INL    | Integral Nonlinearity     | -5.5                                                                                                                                   | _   | 5.5 | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| HAD22a                                           | DNL    | Differential Nonlinearity | -1                                                                                                                                     | _   | 1   | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| HAD23a                                           | Gerr   | Gain Error                | -10                                                                                                                                    |     | 10  | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| HAD24a                                           | EOFF   | Offset Error              | -5                                                                                                                                     | —   | 5   | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |

| Dynamic Performance (12-Bit Mode) <sup>(2)</sup> |        |                           |                                                                                                                                        |     |     |       |                                                  |  |  |

| HAD33a                                           | Fnyq   | Input Signal Bandwidth    | _                                                                                                                                      | _   | 200 | kHz   |                                                  |  |  |

# TABLE 31-12: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

# TABLE 31-13: ADC MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS                               |        |                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |     |      |       |                                                  |  |

|--------------------------------------------------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|--------------------------------------------------|--|

| Param<br>No.                                     | Symbol | Characteristic            | Min                                                                                                                                 | Тур | Max  | Units | Conditions                                       |  |

| ADC Accuracy (10-Bit Mode) <sup>(1)</sup>        |        |                           |                                                                                                                                     |     |      |       |                                                  |  |

| HAD20b                                           | Nr     | Resolution <sup>(3)</sup> | 10 Data Bits                                                                                                                        |     | bits |       |                                                  |  |

| HAD21b                                           | INL    | Integral Nonlinearity     | -1.5                                                                                                                                | _   | 1.5  | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |

| HAD22b                                           | DNL    | Differential Nonlinearity | -0.25                                                                                                                               | _   | 0.25 | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |  |

| HAD23b                                           | Gerr   | Gain Error                | -2.5                                                                                                                                |     | 2.5  | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD24b                                           | EOFF   | Offset Error              | -1.25                                                                                                                               | _   | 1.25 | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| Dynamic Performance (10-Bit Mode) <sup>(2)</sup> |        |                           |                                                                                                                                     |     |      |       |                                                  |  |

| HAD33b                                           | Fnyq   | Input Signal Bandwidth    | _                                                                                                                                   | _   | 400  | kHz   |                                                  |  |

Note 1: These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

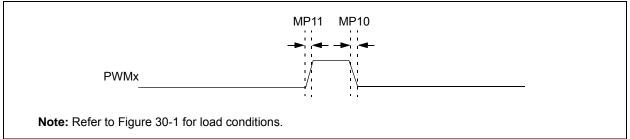

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

Note:

Microchip Technology Drawing C04-103C Sheet 1 of 2

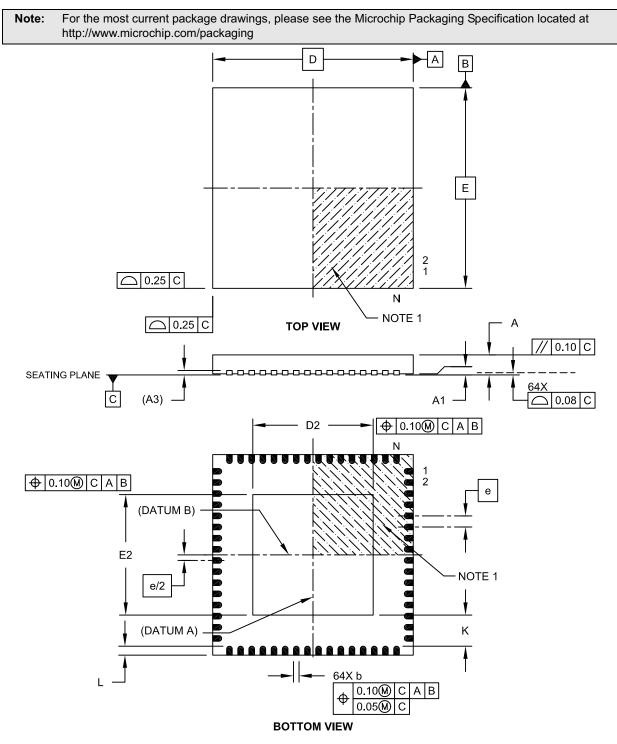

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2