Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202-e-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

| IABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP |       |                                     |                                     |          |        |           |        |       |             |             |              |        |        |          |           |          |       |               |

|--------------------------------------------------------------------|-------|-------------------------------------|-------------------------------------|----------|--------|-----------|--------|-------|-------------|-------------|--------------|--------|--------|----------|-----------|----------|-------|---------------|

| File Name                                                          | Addr. | Bit 15                              | Bit 14                              | Bit 13   | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5  | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

| OC1CON1                                                            | 0900  | —                                   | -                                   | OCSIDL   | C      | CTSEL<2:0 | )>     | —     | ENFLTB      | ENFLTA      | —            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2                                                            | 0902  | FLTMD                               | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC1RS                                                              | 0904  |                                     |                                     |          |        |           |        | Outp  | out Compare | e 1 Seconda | ary Register |        |        |          |           |          |       | xxxx          |

| OC1R                                                               | 0906  |                                     | Output Compare 1 Register xx        |          |        |           |        |       |             |             |              | xxxx   |        |          |           |          |       |               |

| OC1TMR                                                             | 0908  |                                     |                                     |          |        |           |        |       | Timer V     | alue 1 Regi | ster         |        |        |          |           |          |       | xxxx          |

| OC2CON1                                                            | 090A  | _                                   | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2                                                            | 090C  | FLTMD                               | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC2RS                                                              | 090E  | Output Compare 2 Secondary Register |                                     |          |        |           |        |       | xxxx        |             |              |        |        |          |           |          |       |               |

| OC2R                                                               | 0910  |                                     |                                     |          |        |           |        |       | Output Co   | mpare 2 Re  | gister       |        |        |          |           |          |       | xxxx          |

| OC2TMR                                                             | 0912  |                                     |                                     |          |        |           |        |       | Timer V     | alue 2 Regi | ster         |        |        |          |           |          |       | xxxx          |

| OC3CON1                                                            | 0914  | _                                   | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2                                                            | 0916  | FLTMD                               | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS                                                              | 0918  |                                     |                                     |          |        |           |        | Outp  | out Compare | e 3 Seconda | ary Register |        |        |          |           |          |       | xxxx          |

| OC3R                                                               | 091A  |                                     |                                     |          |        |           |        |       | Output Co   | mpare 3 Re  | gister       |        |        |          |           |          |       | xxxx          |

| OC3TMR                                                             | 091C  |                                     |                                     |          |        |           |        |       | Timer V     | alue 3 Regi | ster         |        |        |          |           |          |       | xxxx          |

| OC4CON1                                                            | 091E  | _                                   | -                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2                                                            | 0920  | FLTMD                               | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC4RS                                                              | 0922  |                                     | Output Compare 4 Secondary Register |          |        |           |        |       |             |             | xxxx         |        |        |          |           |          |       |               |

| OC4R                                                               | 0924  |                                     |                                     |          |        |           |        |       | Output Co   | mpare 4 Re  | gister       |        |        |          |           |          |       | xxxx          |

| OC4TMR                                                             | 0926  |                                     |                                     |          |        |           |        |       | Timer V     | alue 4 Regi | ster         |        |        |          |           |          |       | xxxx          |

### TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.1 PAGED MEMORY SCHEME

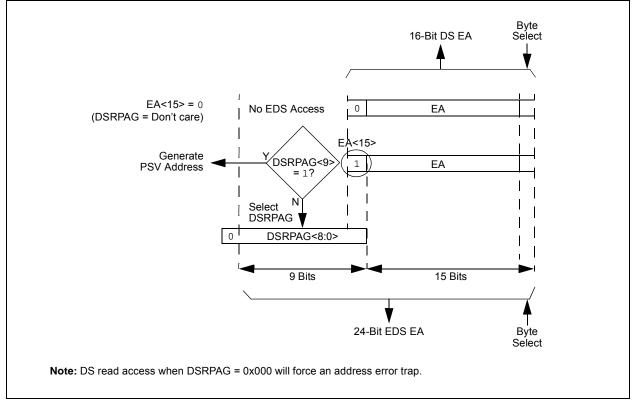

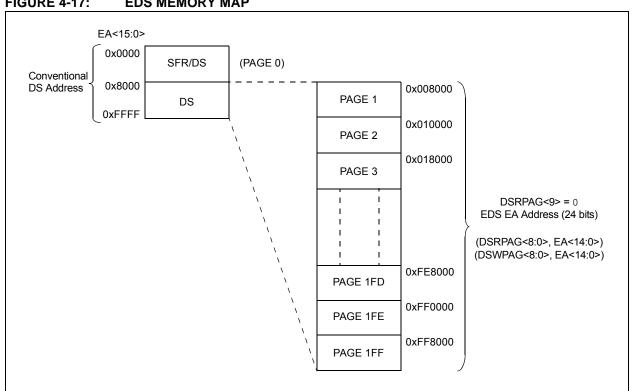

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00    |                                       |              |                   |                  |          |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|----------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0      | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —        | —      |

| bit 15          |                |                                       |              |                   |                  |          | bit 8  |

|                 |                |                                       |              |                   |                  |          |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0      | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1   | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |          | bit 0  |

|                 |                |                                       |              |                   |                  |          |        |

| Legend:         |                |                                       |              |                   |                  |          |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0' |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | x = Bit is unkr  | nown     |        |

|                 |                |                                       |              |                   |                  |          |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |          |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |          |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |          |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |          |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |          |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |          |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |          |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |          |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |          |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |          |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |          |        |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

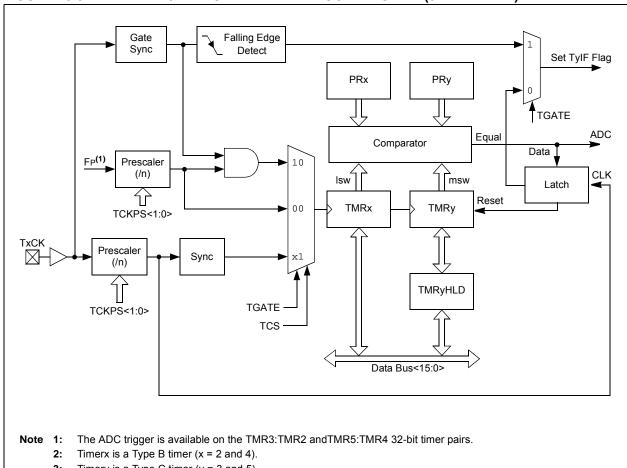

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

NOTES:

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|-----------------|----------------------------------------------------------------------|------------------|-------|-------------------|-------|-----------------|-------|--|--|--|

|                 |                                                                      |                  | QEILE | C<31:24>          |       |                 |       |  |  |  |

| bit 15          |                                                                      |                  |       |                   |       |                 | bit 8 |  |  |  |

|                 |                                                                      |                  |       |                   |       |                 |       |  |  |  |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|                 |                                                                      |                  | QEILE | C<23:16>          |       |                 |       |  |  |  |

| bit 7           |                                                                      |                  |       |                   |       |                 | bit 0 |  |  |  |

|                 |                                                                      |                  |       |                   |       |                 |       |  |  |  |

| Legend:         |                                                                      |                  |       |                   |       |                 |       |  |  |  |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                   |       |                 |       |  |  |  |

| -n = Value at P | OR                                                                   | '1' = Bit is set |       | '0' = Bit is clea | red   | x = Bit is unkr | nown  |  |  |  |

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R = Readable t |       | W = Writable<br>'1' = Bit is set |       | U = Unimplen<br>'0' = Bit is cle |       | ad as '0'<br>x = Bit is unknown |       |  |

|----------------|-------|----------------------------------|-------|----------------------------------|-------|---------------------------------|-------|--|

| Legend:        |       |                                  |       |                                  |       |                                 |       |  |

|                |       |                                  |       |                                  |       |                                 |       |  |

| bit 7          |       |                                  |       |                                  |       |                                 | bit   |  |

|                |       |                                  | QEIL  | EC<7:0>                          |       |                                 |       |  |

| R/W-0          | R/W-0 | R/W-0                            | R/W-0 | R/W-0                            | R/W-0 | R/W-0                           | R/W-0 |  |

| bit 15         |       |                                  |       |                                  |       |                                 | bit   |  |

|                |       |                                  | QEILE | EC<15:8>                         |       |                                 |       |  |

| R/W-0          | R/W-0 | R/W-0                            | R/W-0 | R/W-0                            | R/W-0 | R/W-0                           | R/W-0 |  |

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

#### 18.3 SPIx Control Registers

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 SPIEN SPISIDL SPIBEC<2:0> \_\_\_\_\_ bit 15 R/W-0 R/W-0 R/W-0 R/C-0, HS R/W-0 R/W-0 R-0, HS, HC R-0, HS, HC SRMPT SPIROV SRXMPT SISEL2 SISEL1 SISEL0 SPITBF SPIRBF bit 7 Legend: C = Clearable bit HS = Hardware Settable bit HC = Hardware Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables the module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables the module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues the module operation when device enters Idle mode 0 = Continues the module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPIx transfers that are pending. Slave mode: Number of SPIx transfers that are unread. SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) bit 7 1 = SPIx Shift register is empty and Ready-To-Send or receive the data 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit

#### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register 0 = No overflow has occurred SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode) 1 = RX FIFO is empty 0 = RX FIFO is not empty

#### bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

- 111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

- 110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

- 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

- 100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

- 011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

- 010 = Interrupt when the SPIx receive buffer is 3/4 or more full

- 001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

- 000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

bit 5

bit 8

bit 0

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

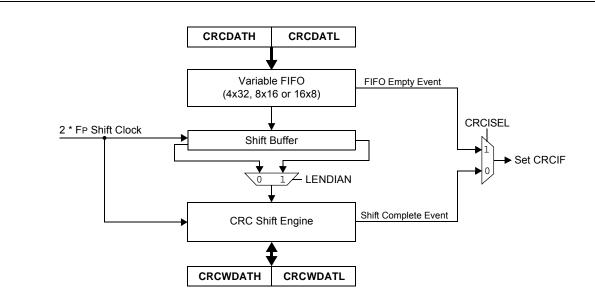

# 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

#### FIGURE 26-1: CRC BLOCK DIAGRAM

| Bit Field             | Description                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDTPRE                | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                         |

| WDTPOST<3:0>          | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                         |

| WDTWIN<1:0>           | Watchdog Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period |

| ALTI2C1               | Alternate I2C1 pin<br>1 = I2C1 is mapped to the SDA1/SCL1 pins<br>0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                                                                  |

| ALTI2C2               | Alternate I2C2 pin<br>1 = I2C2 is mapped to the SDA2/SCL2 pins<br>0 = I2C2 is mapped to the ASDA2/ASCL2 pins                                                                                  |

| JTAGEN <sup>(2)</sup> | JTAG Enable bit<br>1 = JTAG is enabled<br>0 = JTAG is disabled                                                                                                                                |

| ICS<1:0>              | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use       |

### TABLE 27-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

| Base<br>Instr<br># | Assembly<br>Mnemonic                                       |        | Assembly Syntax                                  | Description                               | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |

|--------------------|------------------------------------------------------------|--------|--------------------------------------------------|-------------------------------------------|---------------|-------------------------------|--------------------------|--|

| 46                 | MOV                                                        | MOV    | f,Wn                                             | Move f to Wn                              | 1             | 1                             | None                     |  |

|                    |                                                            | MOV    | f                                                | Move f to f                               | 1             | 1                             | None                     |  |

|                    |                                                            | MOV    | f,WREG                                           | Move f to WREG                            | 1             | 1                             | None                     |  |

|                    |                                                            | MOV    | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1             | 1                             | None                     |  |

|                    |                                                            | MOV.b  | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1             | 1                             | None                     |  |

|                    |                                                            | MOV    | Wn,f                                             | Move Wn to f                              | 1             | 1                             | None                     |  |

|                    |                                                            | MOV    | Wso,Wdo                                          | Move Ws to Wd                             | 1             | 1                             | None                     |  |

|                    |                                                            | MOV    | WREG, f                                          | Move WREG to f                            | 1             | 1                             | None                     |  |

|                    |                                                            | MOV.D  | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1             | 2                             | None                     |  |

|                    |                                                            | MOV.D  | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1             | 2                             | None                     |  |

| 47                 | MOVPAG                                                     | MOVPAG | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1             | 1                             | None                     |  |

|                    |                                                            | MOVPAG | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1             | 1                             | None                     |  |

|                    |                                                            | MOVPAG | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1             | 1                             | None                     |  |

|                    |                                                            | MOVPAG | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1             | 1                             | None                     |  |

|                    |                                                            | MOVPAG | Ws, DSWPAG                                       | Move Ws<8:0> to DSWPAG                    | 1             | 1                             | None                     |  |

|                    |                                                            | MOVPAG | Ws, TBLPAG                                       | Move Ws<7:0> to TBLPAG                    | 1             | 1                             | None                     |  |

| 48                 | MOVSAC                                                     | MOVSAC | Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>             | Prefetch and store accumulator            | 1             | 1                             | None                     |  |

| 49                 | MPY                                                        | MPY    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | Multiply Wm by Wn to Accumulator          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

|                    |                                                            | MPY    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Square Wm to Accumulator                  | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 50                 | MPY.N                                                      | MPY.N  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | -(Multiply Wm by Wn) to Accumulator       | 1             | 1                             | None                     |  |

| 51                 | 1 MSC MSC Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> |        | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Subtract from Accumulator    | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax    | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |

|--------------------|----------------------|--------|--------------------|------------------------------------|---------------|-------------------------------|--------------------------|--|

| 72                 | SL                   | SL     | f                  | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | SL     | f,WREG             | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | SL     | Ws,Wd              | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | SL     | Wb,Wns,Wnd         | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |  |

|                    |                      | SL     | Wb,#lit5,Wnd       | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |  |

| 73                 | SUB                  | SUB    | Acc <sup>(1)</sup> | Subtract Accumulators              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

|                    |                      | SUB    | f                  | f = f – WREG                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB    | f,WREG             | WREG = f – WREG                    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB    | #lit10,Wn          | Wn = Wn - lit10                    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB    | Wb,Ws,Wd           | Wd = Wb – Ws                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUB    | Wb,#lit5,Wd        | Wd = Wb - lit5                     | 1             | 1                             | C,DC,N,OV,Z              |  |

| 74                 | SUBB                 | SUBB   | f                  | $f = f - WREG - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB   | f,WREG             | WREG = f – WREG – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB   | #lit10,Wn          | $Wn = Wn - lit10 - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB   | Wb,Ws,Wd           | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBB   | Wb,#lit5,Wd        | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |  |

| 75                 | SUBR                 | SUBR   | f                  | f = WREG – f                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBR   | f,WREG             | WREG = WREG – f                    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBR   | Wb,Ws,Wd           | Wd = Ws – Wb                       | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBR   | Wb,#lit5,Wd        | Wd = lit5 – Wb                     | 1             | 1                             | C,DC,N,OV,Z              |  |

| 76                 | SUBBR                | SUBBR  | f                  | $f = WREG - f - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBBR  | f,WREG             | WREG = WREG – f – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBBR  | Wb,Ws,Wd           | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | SUBBR  | Wb,#lit5,Wd        | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |  |

| 77                 | SWAP                 | SWAP.b | Wn                 | Wn = nibble swap Wn                | 1             | 1                             | None                     |  |

|                    |                      | SWAP   | Wn                 | Wn = byte swap Wn                  | 1             | 1                             | None                     |  |

| 78                 | TBLRDH               | TBLRDH | Ws,Wd              | Read Prog<23:16> to Wd<7:0>        | 1             | 5                             | None                     |  |

| 79                 | TBLRDL               | TBLRDL | Ws,Wd              | Read Prog<15:0> to Wd              | 1             | 5                             | None                     |  |

| 80                 | TBLWTH               | TBLWTH | Ws,Wd              | Write Ws<7:0> to Prog<23:16>       | 1             | 2                             | None                     |  |

| 81                 | TBLWTL               | TBLWTL | Ws,Wd              | Write Ws to Prog<15:0>             | 1             | 2                             | None                     |  |

| 82                 | ULNK                 | ULNK   |                    | Unlink Frame Pointer               | 1             | 1                             | SFA                      |  |

| 83                 | XOR                  | XOR    | f                  | f = f .XOR. WREG                   | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR    | f,WREG             | WREG = f.XOR. WREG                 | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR    | #lit10,Wn          | Wd = lit10 .XOR. Wd                | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR    | Wb,Ws,Wd           | Wd = Wb .XOR. Ws                   | 1             | 1                             | N,Z                      |  |

|                    |                      | XOR    | Wb,#lit5,Wd        | Wd = Wb .XOR. lit5                 | 1             | 1                             | N,Z                      |  |

| 84                 | ZE                   | ZE     | Ws,Wnd             | Wnd = Zero-extend Ws               | 1             | 1                             | C,Z,N                    |  |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# TABLE 30-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | rics                                         | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |                    |       |                                |  |  |  |

|--------|-----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|-------|--------------------------------|--|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                 | Тур. <sup>(2)</sup> | Max.               | Units | Conditions                     |  |  |  |

| SP70   | FscP                  | Maximum SCK1 Input<br>Frequency              | _                                                                                                                                                                                                    |                     | Lesser of FP or 15 | MHz   | (Note 3)                       |  |  |  |

| SP72   | TscF                  | SCK1 Input Fall Time                         | _                                                                                                                                                                                                    |                     |                    | ns    | See Parameter DO32<br>(Note 4) |  |  |  |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                    |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |  |  |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                    |                     | _                  | ns    | See Parameter DO32<br>(Note 4) |  |  |  |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                    |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |  |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                    | 6                   | 20                 | ns    |                                |  |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                   |                     | _                  | ns    |                                |  |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                                                                                                                                                                   |                     |                    | ns    |                                |  |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                                                                                                                                                                   |                     | —                  | ns    |                                |  |  |  |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                                                                                                                                                                  |                     | —                  | ns    |                                |  |  |  |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                                                                                                                                                                   | _                   | 50                 | ns    | (Note 4)                       |  |  |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40                                                                                                                                                                                         | _                   | _                  | ns    | (Note 4)                       |  |  |  |

| SP60   | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge     | —                                                                                                                                                                                                    | _                   | 50                 | ns    |                                |  |  |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

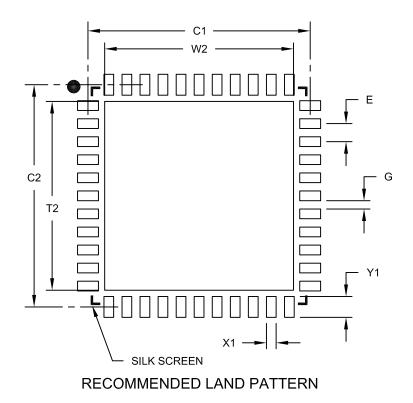

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 6.60 |

| Optional Center Pad Length | T2 |             |      | 6.60 |

| Contact Pad Spacing        | C1 |             | 8.00 |      |

| Contact Pad Spacing        | C2 |             | 8.00 |      |

| Contact Pad Width (X44)    | X1 |             |      | 0.35 |

| Contact Pad Length (X44)   | Y1 |             |      | 0.85 |

| Distance Between Pads      | G  | 0.25        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B