Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

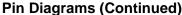

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202-h-mm |

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

**Note:** The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within

one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

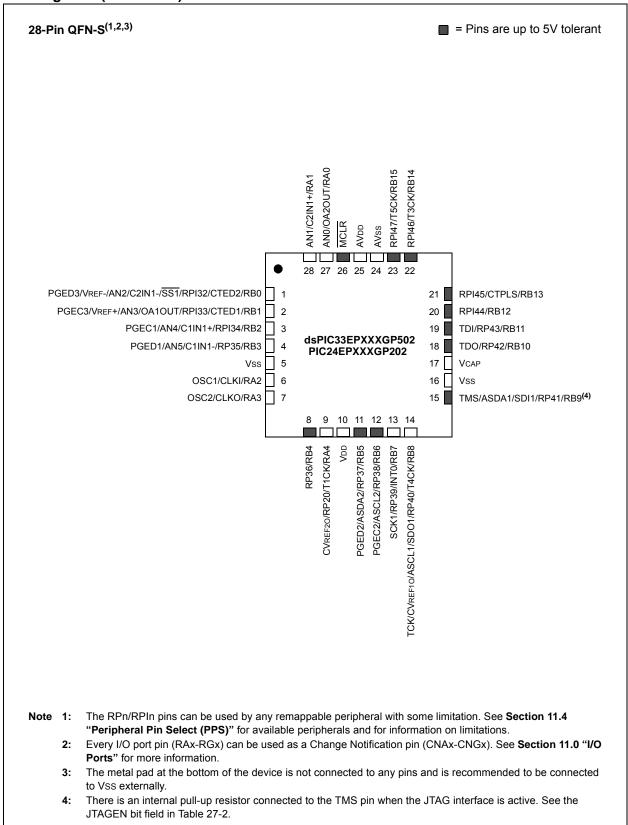

FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

## 4.1.1 PROGRAM MEMORY ORGANIZATION

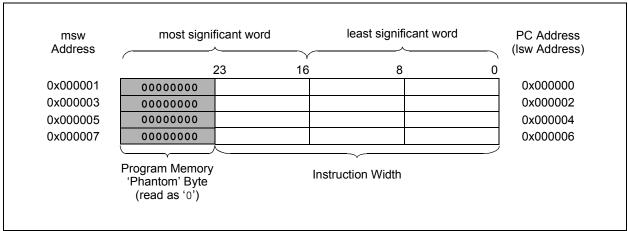

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x0000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

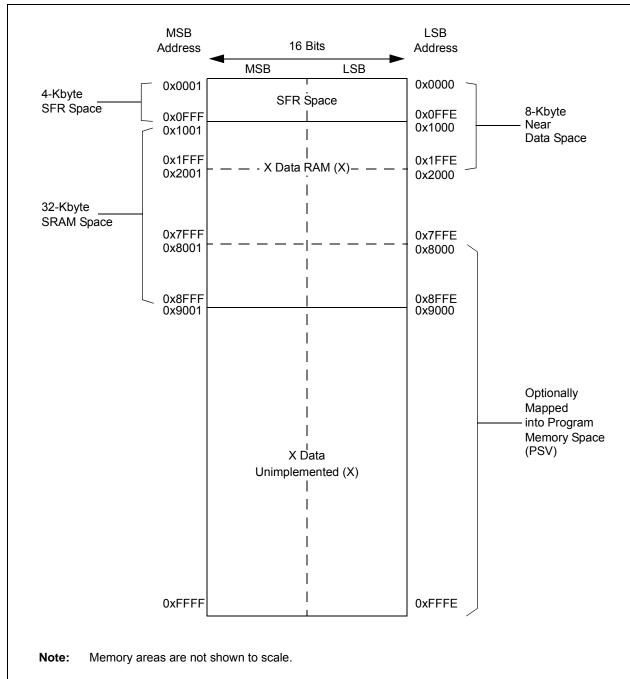

FIGURE 4-15: DATA MEMORY MAP FOR PIC24EP256GP/MC20X/50X DEVICES

#### TABLE 4-14: PWM GENERATOR 2 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14       | Bit 13  | Bit 12     | Bit 11                                             | Bit 10                                           | Bit 9  | Bit 8      | Bit 7     | Bit 6  | Bit 5   | Bit 4  | Bit 3 | Bit 2     | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------|---------|--------------|---------|------------|----------------------------------------------------|--------------------------------------------------|--------|------------|-----------|--------|---------|--------|-------|-----------|-------|--------|---------------|

| PWMCON2   | 0C40  | FLTSTAT | CLSTAT       | TRGSTAT | FLTIEN     | CLIEN                                              | TRGIEN                                           | ITB    | MDCS       | DTC<      | :1:0>  | DTCP    | _      | MTBS  | CAM       | XPRES | IUE    | 0000          |

| IOCON2    | 0C42  | PENH    | PENL         | POLH    | POLL       | PMOD                                               | <1:0>                                            | OVRENH | OVRENL     | OVRDA     | T<1:0> | FLTDA   | T<1:0> | CLDA  | \T<1:0>   | SWAP  | OSYNC  | C000          |

| FCLCON2   | 0C44  | _       |              | C       | LSRC<4:0   | >                                                  |                                                  | CLPOL  | CLMOD      |           | FLT    | SRC<4:0 | >      |       | FLTPOL    | FLTMO | D<1:0> | 00F8          |

| PDC2      | 0C46  |         |              |         | PDC2<15:0> |                                                    |                                                  |        |            |           |        |         |        |       | 0000      |       |        |               |

| PHASE2    | 0C48  |         | PHASE2<15:0> |         |            |                                                    |                                                  |        |            |           |        |         |        | 0000  |           |       |        |               |

| DTR2      | 0C4A  | _       | _            |         | DTR2<13:0> |                                                    |                                                  |        |            |           |        |         |        |       | 0000      |       |        |               |

| ALTDTR2   | 0C4C  | _       | _            |         |            |                                                    |                                                  |        | AL         | TDTR2<13: | 0>     |         |        |       |           |       |        | 0000          |

| TRIG2     | 0C52  |         |              |         |            |                                                    |                                                  | TF     | RGCMP<15:0 | >         |        |         |        |       |           |       |        | 0000          |

| TRGCON2   | 0C54  |         | TRGDI        | /<3:0>  |            | _                                                  | _                                                | _      | _          | _         | _      |         |        | TRO   | GSTRT<5:0 | )>    |        | 0000          |

| LEBCON2   | 0C5A  | PHR     | PHF          | PLR     | PLF        | FLTLEBEN CLLEBEN — — — BCH BCL BPHH BPHL BPLH BPLL |                                                  |        |            |           |        |         | 0000   |       |           |       |        |               |

| LEBDLY2   | 0C5C  | _       | _            | _       |            |                                                    |                                                  |        |            |           |        |         |        | 0000  |           |       |        |               |

| AUXCON2   | 0C5E  | _       | _            | _       | _          |                                                    | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN ( |        |            |           |        |         |        | 0000  |           |       |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15       | Bit 14     | Bit 13  | Bit 12     | Bit 11       | Bit 10                                        | Bit 9  | Bit 8      | Bit 7     | Bit 6  | Bit 5   | Bit 4   | Bit 3 | Bit 2     | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------|--------------|------------|---------|------------|--------------|-----------------------------------------------|--------|------------|-----------|--------|---------|---------|-------|-----------|-------|--------|---------------|

| PWMCON3   | 0C60  | FLTSTAT      | CLSTAT     | TRGSTAT | FLTIEN     | CLIEN        | TRGIEN                                        | ITB    | MDCS       | DTC<      | 1:0>   | DTCP    | _       | MTBS  | CAM       | XPRES | IUE    | 0000          |

| IOCON3    | 0C62  | PENH         | PENL       | POLH    | POLL       | PMOD         | <1:0>                                         | OVRENH | OVRENL     | OVRDA     | T<1:0> | FLTDA   | \T<1:0> | CLD   | AT<1:0>   | SWAP  | OSYNC  | C000          |

| FCLCON3   | 0C64  | _            |            | C       | CLSRC<4:0  | <b> &gt;</b> |                                               | CLPOL  | CLMOD      |           | FLT    | SRC<4:0 | >       |       | FLTPOL    | FLTMO | D<1:0> | 00F8          |

| PDC3      | 0C66  |              | PDC3<15:0> |         |            |              |                                               |        |            |           |        |         |         | 0000  |           |       |        |               |

| PHASE3    | 0C68  | PHASE3<15:0> |            |         |            |              |                                               |        |            |           |        |         | 0000    |       |           |       |        |               |

| DTR3      | 0C6A  | _            | _          |         | DTR3<13:0> |              |                                               |        |            |           |        |         |         |       | 0000      |       |        |               |

| ALTDTR3   | 0C6C  | _            | _          |         |            |              |                                               |        | AL         | TDTR3<13: | :0>    |         |         |       |           |       |        | 0000          |

| TRIG3     | 0C72  |              |            |         |            |              |                                               | T      | RGCMP<15:0 | )>        |        |         |         |       |           |       |        | 0000          |

| TRGCON3   | 0C74  |              | TRGDI      | V<3:0>  |            | _            | _                                             | _      | _          | _         | _      |         |         | TRO   | GSTRT<5:0 | )>    |        | 0000          |

| LEBCON3   | 0C7A  | PHR          | PHF        | PLR     | PLF        | FLTLEBEN     | CLLEBEN                                       | _      | _          | _         | _      | ВСН     | BCL     | врнн  | BPHL      | BPLH  | BPLL   | 0000          |

| LEBDLY3   | 0C7C  | _            | _          | _       | LEB<11:0>  |              |                                               |        |            |           |        |         |         | 0000  |           |       |        |               |

| AUXCON3   | 0C7E  | _            | _          | _       | _          |              | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLE |        |            |           |        |         | CHOPLEN | 0000  |           |       |        |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

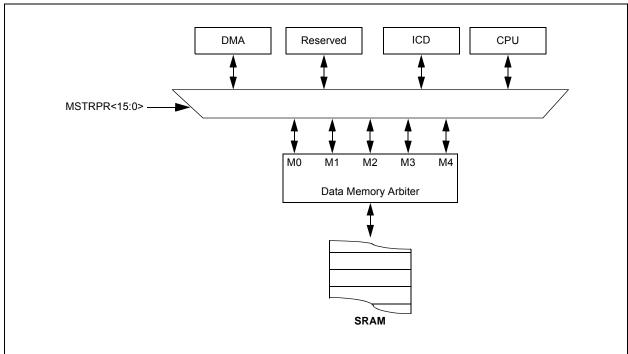

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

TABLE 4-62: DATA MEMORY BUS ARBITER PRIORITY

| Priority     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

## 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note:

The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

## 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note:

All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XBREVx value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note:

Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

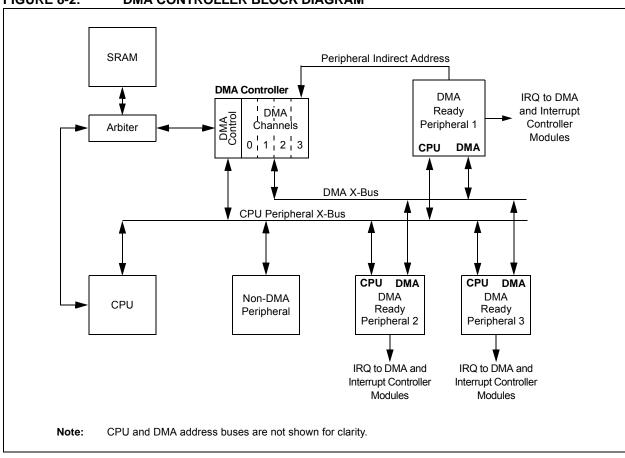

#### FIGURE 8-2: DMA CONTROLLER BLOCK DIAGRAM

#### 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

#### 9.3 Oscillator Control Registers

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | _   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | R/W-0  | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|--------|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | IOLOCK | LOCK | _   | CF <sup>(3)</sup> | _   | _   | OSWEN |

| bit 7   |        |      |     |                   |     |     | bit 0 |

| Legend:           | y = Value set from Configu | y = Value set from Configuration bits on POR |                    |  |  |  |  |  |  |

|-------------------|----------------------------|----------------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0'           |                    |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |  |  |  |

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits (read-only)

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 11 **Unimplemented:** Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 7 CLKLOCK: Clock Lock Enable bit

1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified

0 = Clock and PLL selections are not locked, configurations may be modified

bit 6 IOLOCK: I/O Lock Enable bit

1 = I/O lock is active

0 = I/O lock is not active

bit 5 **LOCK:** PLL Lock Status bit (read-only)

1 = Indicates that PLL is in lock or PLL start-up timer is satisfied

0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

**Note 1:** Writes to this register require an unlock sequence. Refer to "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual" (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   |     | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------|-------|-------|-------|

| _     |       |       |       | U2RXR<6:0 | >     |       |       |

| bit 7 |       |       |       |           |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 **U2RXR<6:0>:** Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

•

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |       |       |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **DISSCK:** Disable SCKx Pin bit (SPIx Master modes only)

1 = Internal SPIx clock is disabled, pin functions as I/O

0 = Internal SPIx clock is enabled

bit 11 DISSDO: Disable SDOx Pin bit

1 = SDOx pin is not used by the module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data is sampled at end of data output time

0 = Input data is sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin is used for Slave mode

$0 = \overline{SSx}$  pin is not used by the module; pin is controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

${\tt 1}$  = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both primary and secondary prescalers to the value of 1:1.

#### 21.2 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- · Disable mode

- · Normal Operation mode

- · Listen Only mode

- · Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3 ECAN Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

#### 21.3.1 KEY RESOURCES

- "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 21-6: CXINTF: ECANX INTERRUPT FLAG REGISTER (CONTINUED)

bit 1 RBIF: RX Buffer Interrupt Flag bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 TBIF: TX Buffer Interrupt Flag bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

#### 24.4 Step Commands and Format

TABLE 24-1: PTG STEP COMMAND FORMAT

| Step Command Byte: |               |  |  |  |  |  |  |

|--------------------|---------------|--|--|--|--|--|--|

| STEPx<7:0>         |               |  |  |  |  |  |  |

| CMD<3:0>           | OPTION<3:0>   |  |  |  |  |  |  |

| bit 7 bit          | 4 bit 3 bit 0 |  |  |  |  |  |  |

| bit 7-4 | CMD<3:0> | Step<br>Command                                          | Command Description                                                                                                                                                                |  |  |  |  |  |

|---------|----------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | 0000     | PTGCTRL                                                  | Execute control command as described by OPTION<3:0>.                                                                                                                               |  |  |  |  |  |

|         | 0001     | PTGADD                                                   | Add contents of PTGADJ register to target register as described by OPTION<3:0>.                                                                                                    |  |  |  |  |  |

|         |          | PTGCOPY                                                  | Copy contents of PTGHOLD register to target register as described by OPTION<3:0>.                                                                                                  |  |  |  |  |  |

|         | 001x     | PTGSTRB                                                  | Copy the value contained in CMD<0>:OPTION<3:0> to the CH0SA<4:0> bits (AD1CHS0<4:0>).                                                                                              |  |  |  |  |  |

|         | 0100     | PTGWHI                                                   | Wait for a low-to-high edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                 |  |  |  |  |  |

|         | 0101     | PTGWLO                                                   | Wait for a high-to-low edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                 |  |  |  |  |  |

|         | 0110     | Reserved                                                 | Reserved.                                                                                                                                                                          |  |  |  |  |  |

|         | 0111     | PTGIRQ                                                   | Generate individual interrupt request as described by OPTION3<:0>.                                                                                                                 |  |  |  |  |  |

|         | 100x     | PTGTRIG                                                  | Generate individual trigger output as described by < <cmd<0>:OPTION&lt;3:0&gt;&gt;.</cmd<0>                                                                                        |  |  |  |  |  |

|         | 101x     | PTGJMP                                                   | Copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR) and jump to that Step queue.</cmd<0>                                                    |  |  |  |  |  |

|         | 110x     | PTGC0 = PTGC0LIM: Increment the Queue Pointer (PTGQPTR). |                                                                                                                                                                                    |  |  |  |  |  |

|         |          |                                                          | PTGC0 ≠ PTGC0LIM: Increment Counter 0 (PTGC0) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue</cmd<0>  |  |  |  |  |  |

|         | 111x     | PTGJMPC1                                                 | PTGC1 = PTGC1LIM: Increment the Queue Pointer (PTGQPTR).                                                                                                                           |  |  |  |  |  |

|         |          |                                                          | PTGC1 ≠ PTGC1LIM: Increment Counter 1 (PTGC1) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue.</cmd<0> |  |  |  |  |  |

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

- 2: Refer to Table 24-2 for the trigger output descriptions.

- 3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

TABLE 30-48: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)

TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |

|--------------------|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP70               | FscP                  | Maximum SCK1 Input Frequency               | _                                                                                                                                                                                                                                                | _                   | 11   | MHz   | (Note 3)                    |

| SP72               | TscF                  | SCK1 Input Fall Time                       | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP73               | TscR                  | SCK1 Input Rise Time                       | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                 | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                 | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge  | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to First SCK1 Edge  | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge  | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓ Input            | 120                                                                                                                                                                                                                                              | _                   | _    | ns    |                             |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance     | 10                                                                                                                                                                                                                                               | _                   | 50   | ns    | (Note 4)                    |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                      | 1.5 Tcy + 40                                                                                                                                                                                                                                     | _                   | _    | ns    | (Note 4)                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS (CONTINUED)

| DC CHARACTERISTICS |                                   | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                                              |                     |                                              |             |                                                 |

|--------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------|----------------------------------------------|-------------|-------------------------------------------------|

| Param<br>No.       | Symbol                            | Characteristic                                                                                                                                                                                                                                                  | Min.                                         | Typ. <sup>(2)</sup> | Max.                                         | Units       | Conditions                                      |

| Op Am              | DC Charac                         | cteristics                                                                                                                                                                                                                                                      |                                              |                     |                                              |             |                                                 |

| CM40               | VCMR                              | Common-Mode Input<br>Voltage Range                                                                                                                                                                                                                              | AVss                                         | _                   | AVDD                                         | V           |                                                 |

| CM41               | CMRR                              | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                                                                                                                                                                                                                   | _                                            | 40                  | _                                            | db          | VCM = AVDD/2                                    |

| CM42               | VOFFSET                           | Op Amp Offset<br>Voltage <sup>(3)</sup>                                                                                                                                                                                                                         | _                                            | ±5                  | _                                            | mV          |                                                 |

| CM43               | VGAIN                             | Open-Loop Voltage<br>Gain <sup>(3)</sup>                                                                                                                                                                                                                        | _                                            | 90                  | _                                            | db          |                                                 |

| CM44               | los                               | Input Offset Current                                                                                                                                                                                                                                            | _                                            | _                   | _                                            | _           | See pad leakage<br>currents in Table 30-11      |

| CM45               | lв                                | Input Bias Current                                                                                                                                                                                                                                              | _                                            | _                   | _                                            | _           | See pad leakage<br>currents in Table 30-11      |

| CM46               | lout                              | Output Current                                                                                                                                                                                                                                                  | _                                            | _                   | 420                                          | μΑ          | With minimum value of RFEEDBACK (CM48)          |

| CM48               | RFEEDBACK                         | Feedback Resistance<br>Value                                                                                                                                                                                                                                    | 8                                            | _                   | _                                            | kΩ          |                                                 |

| CM49a              | VOADC                             | Output Voltage<br>Measured at OAx Using<br>ADC <sup>(3,4)</sup>                                                                                                                                                                                                 | AVss + 0.077<br>AVss + 0.037<br>AVss + 0.018 |                     | AVDD - 0.077<br>AVDD - 0.037<br>AVDD - 0.018 | V<br>V<br>V | IOUT = 420 μA<br>IOUT = 200 μA<br>IOUT = 100 μA |

| CM49b              |                                   | Output Voltage<br>Measured at OAxOUT<br>Pin <sup>(3,4,5)</sup>                                                                                                                                                                                                  | AVss + 0.210<br>AVss + 0.100<br>AVss + 0.050 | _                   | AVDD - 0.210<br>AVDD - 0.100<br>AVDD - 0.050 | V<br>V<br>V | ΙΟυΤ = 420 μΑ<br>ΙΟυΤ = 200 μΑ<br>ΙΟυΤ = 100 μΑ |

| CM51               | R <sub>INT</sub> 1 <sup>(6)</sup> | Internal Resistance 1<br>(Configuration A<br>and B) <sup>(3,4,5)</sup>                                                                                                                                                                                          | 198                                          | 264                 | 317                                          | Ω           | Min = -40°C<br>Typ = +25°C<br>Max = +125°C      |

Note 1: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 3: Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

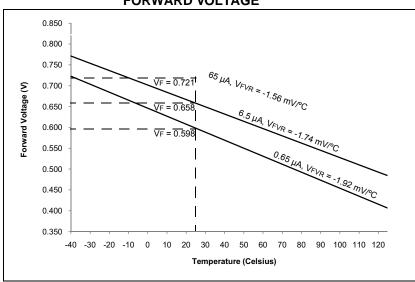

Temperature (Celsius)

TYPICAL CTMU TEMPERATURE DIODE FIGURE 32-11: **FORWARD VOLTAGE**

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support