Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202-h-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES

| F <i>P</i>        | MIL                            | ES                            |              |                      |               |                |                                                |                              |        |                    |                  |                                    | _    | _                    | _                            | _                   |      |     | _        | _         |                                |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

|                   | ()                             | es)                           |              |                      |               | Rei            | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |      |                      | -                            |                     |      |     |          |           |                                |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I²C™ | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | PTG | I/O Pins | Pins      | Packages                       |

| PIC24EP32MC202    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC202    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128MC202   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| PIC24EP256MC202   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512MC202   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP32MC203    | 512                            | 32                            | 4            | -                    |               |                | <u> </u>                                       | ,                            | 6      | 6                  |                  | <u> </u>                           | 6    |                      | _                            |                     | v    | ~   | 0-       |           | ) (T) A                        |

| PIC24EP64MC203    | 1024                           | 64                            | 8            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| PIC24EP32MC204    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      | 1   |          |           |                                |

| PIC24EP64MC204    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| PIC24EP128MC204   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256MC204   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          | 40        | UQFN                           |

| PIC24EP512MC204   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC206    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP128MC206   | 1024                           | 128                           | 16           | F                    | 4             |                | 6                                              | 4                            | 2      | 2                  |                  | 2                                  | 2    | 1                    | 10                           | 2/4                 | Vaa  | Vaa | 50       | 64        | TQFP,                          |

| PIC24EP256MC206   | 1024                           | 256                           | 32           | <sup>5</sup><br>32   | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4 Ye              | Yes  | Yes | 53       | 04        | QFN                            |

| PIC24EP512MC206   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC202  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC202  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC202 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3 <b>(1)</b>      | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC202 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC202 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC203  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  |                  | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC203  | 1024                           | 64                            | 8            | э                    | 4             | 4              | 0                                              | -                            | 2      | 2                  |                  | ა                                  | 2    | I                    | 0                            | 3/4                 | res  | tes | 25       | 30        | VILA                           |

| dsPIC33EP32MC204  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC204  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| dsPIC33EP128MC204 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | —                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256MC204 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | UQFN                           |

| dsPIC33EP512MC204 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC206  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP128MC206 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | TQFP,                          |

| dsPIC33EP256MC206 | 1024                           | 256                           | 32           | 5                    | +             | 1              | 0                                              | 1                            | 2      | 2                  |                  | 5                                  | 2    | · ·                  | 10                           | 5/4                 | 165  | 163 | 55       | 04        | QFN                            |

| dsPIC33EP512MC206 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC502  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC502  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,<br>SOIC,                |

| dsPIC33EP128MC502 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC502 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC502 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC503  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC503  | 1024                           | 64                            | 8            | ~                    |               |                |                                                |                              | _      | _                  |                  |                                    | _    |                      | Ĵ                            | <i></i>             |      |     |          |           |                                |

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details. 2: Only SPI2 is remappable.

3: INTO is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

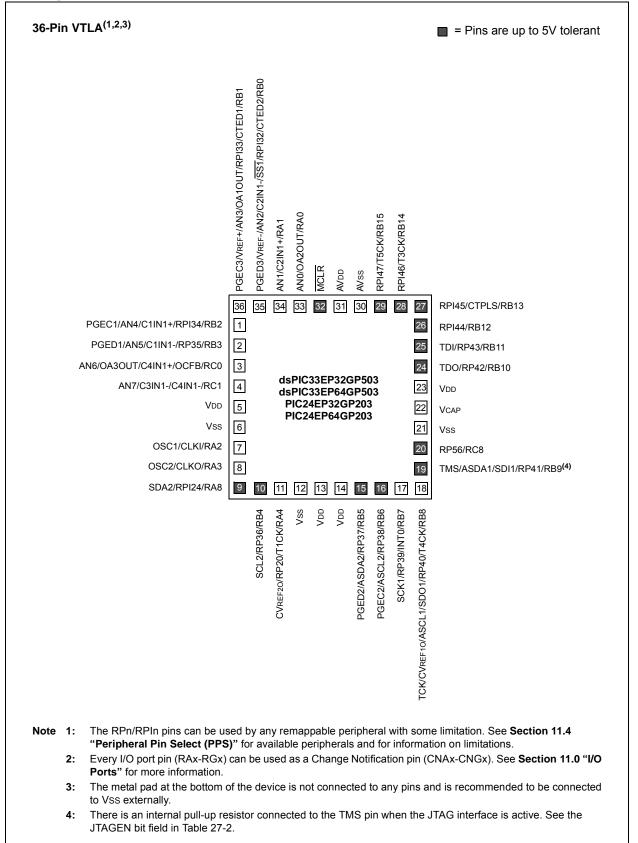

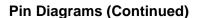

# **Pin Diagrams (Continued)**

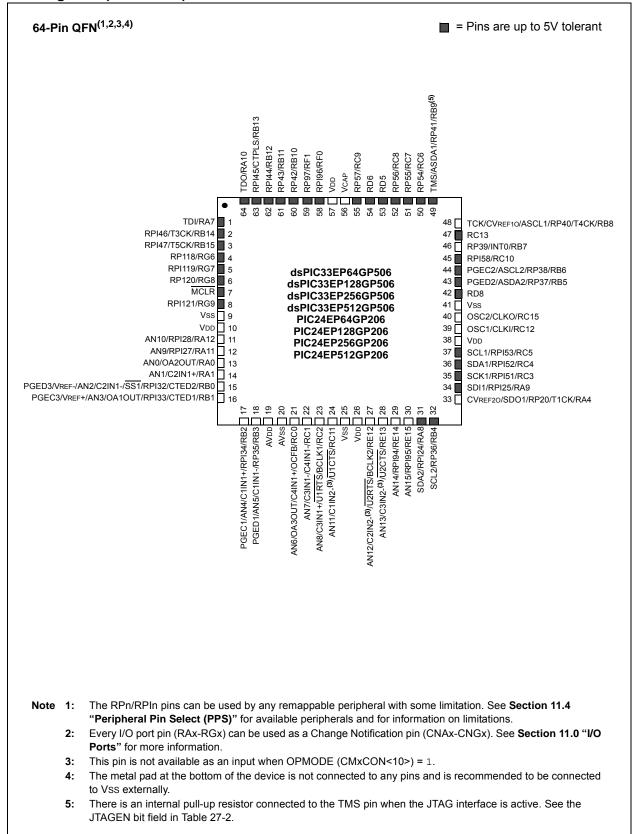

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

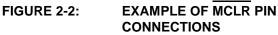

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

|              |       |        |        | -                       | -      | -          |        |       |       |       |            |       |       |            |       |       |       |               |

|--------------|-------|--------|--------|-------------------------|--------|------------|--------|-------|-------|-------|------------|-------|-------|------------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13                  | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0  | _      |        |                         |        | NT1R<6:0>  |        |       |       |       | _          | _     | _     | _          |       | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —      | —                       | -      |            | -      |       |       | -     | INT2R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR3       | 06A6  |        | _      | _                       | _      | _          | _      | _     | _     | _     |            |       | -     | [2CKR<6:0> | >     |       |       | 0000          |

| RPINR7       | 06AE  | _      |        |                         |        | IC2R<6:0>  |        |       |       | —     |            |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |        |                         |        | IC4R<6:0>  |        |       |       | —     | IC3R<6:0>  |       |       |            |       | 0000  |       |               |

| RPINR11      | 06B6  | _      | _      | _                       | —      | —          | _      | _     | _     | —     |            |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12      | 06B8  | _      |        | FLT2R<6:0> — FLT1R<6:0> |        |            |        |       |       | 0000  |            |       |       |            |       |       |       |               |

| RPINR14      | 06BC  | _      |        |                         | (      | QEB1R<6:0  | >      |       |       | —     |            |       | (     | QEA1R<6:0> | >     |       |       | 0000          |

| RPINR15      | 06BE  | _      |        |                         | Н      | OME1R<6:0  | )>     |       |       | —     |            |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  | _      | _      | _                       | —      | _          | _      | _     | _     | —     |            |       | ι     | J1RXR<6:0> | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _      | _                       | _      | _          | _      | _     | _     | —     |            |       | ι     | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |        | •                       | S      | CK2INR<6:0 | )>     |       |       | _     |            |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      |                         | _      | _          | _      | _     | _     | _     |            |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR37      | 06EA  | _      |        |                         | S      | YNCI1R<6:0 | )>     |       |       | _     | _          | _     | _     | _          | _     | _     | _     | 0000          |

| RPINR38      | 06EC  | _      |        |                         | DT     | CMP1R<6:   | 0>     |       |       | _     | _          | _     | _     |            | _     | _     | _     | 0000          |

| RPINR39      | 06EE  | _      |        |                         | DT     | CMP3R<6:   | 0>     |       |       | —     |            |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

# 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^{N}$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume    |  |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | word-sized data (LSb of every EA is always |  |  |  |  |  |  |  |  |  |  |

|       | clear). The XBREVx value is scaled         |  |  |  |  |  |  |  |  |  |  |

|       | accordingly to generate compatible (byte)  |  |  |  |  |  |  |  |  |  |  |

|       | addresses.                                 |  |  |  |  |  |  |  |  |  |  |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

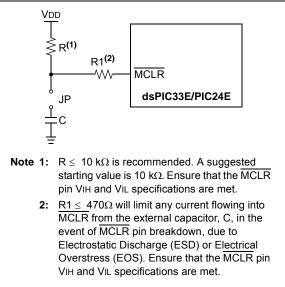

### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                  | U-0                                       | U-0              | U-0             | U-0              | U-0             | U-0                | R/W-0   |  |

|----------------------------------------------------------------------|-------------------------------------------|------------------|-----------------|------------------|-----------------|--------------------|---------|--|

| _                                                                    | —                                         | —                |                 | —                | —               | —                  | PLLDIV8 |  |

| bit 15                                                               |                                           |                  |                 |                  |                 |                    | bit 8   |  |

|                                                                      |                                           |                  |                 |                  |                 |                    |         |  |

| R/W-0                                                                | R/W-0                                     | R/W-1            | R/W-1           | R/W-0            | R/W-0           | R/W-0              | R/W-0   |  |

| PLLDIV7                                                              | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3          | PLLDIV2         | PLLDIV1            | PLLDIV0 |  |

| bit 7                                                                |                                           |                  |                 |                  |                 |                    | bit 0   |  |

|                                                                      |                                           |                  |                 |                  |                 |                    |         |  |

| Legend:                                                              |                                           |                  |                 |                  |                 |                    |         |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                           |                  |                 |                  |                 |                    |         |  |

| -n = Value at P                                                      | OR                                        | '1' = Bit is set |                 | '0' = Bit is cle | ared            | x = Bit is unknown |         |  |

|                                                                      |                                           |                  |                 |                  |                 |                    |         |  |

| bit 15-9                                                             | Unimplemen                                | ted: Read as '   | 0'              |                  |                 |                    |         |  |

| bit 8-0                                                              | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted    | as 'M', PLL mul | tiplier)           |         |  |

|                                                                      | 111111111 =                               | = 513            |                 |                  |                 |                    |         |  |

|                                                                      | •                                         |                  |                 |                  |                 |                    |         |  |

|                                                                      | •                                         |                  |                 |                  |                 |                    |         |  |

|                                                                      | •                                         |                  |                 |                  |                 |                    |         |  |

|                                                                      | 000110000 =                               | = 50 (default)   |                 |                  |                 |                    |         |  |

|                                                                      |                                           |                  |                 |                  |                 |                    |         |  |

|                                                                      | •                                         |                  |                 |                  |                 |                    |         |  |

|                                                                      | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                  |                 |                    |         |  |

|                                                                      |                                           |                  |                 |                  |                 |                    |         |  |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2                      | 2: PERIPHER                                         | AL MODULE      | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |  |  |  |

|--------------|-------------------------------------------|-----------------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| U-0          | U-0                                       | U-0                                                 | U-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _            |                                           | —                                                   |                | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |  |  |

| bit 15       |                                           |                                                     |                |                   |                 |                 | bit   |  |  |  |  |  |  |

| U-0          | U-0                                       | U-0                                                 | U-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|              |                                           |                                                     |                | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |  |  |

| bit 7        |                                           |                                                     |                |                   |                 |                 | bit   |  |  |  |  |  |  |

|              |                                           |                                                     |                |                   |                 |                 |       |  |  |  |  |  |  |

| Legend:      | 1.1.1                                     |                                                     |                |                   |                 |                 |       |  |  |  |  |  |  |

| R = Readab   |                                           | W = Writable b                                      | Dit            | •                 | nented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value a | at POR                                    | '1' = Bit is set                                    |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |  |

| bit 15-12    | Unimplemen                                | ted: Read as '0                                     | ,              |                   |                 |                 |       |  |  |  |  |  |  |

| bit 11       | -                                         | t Capture 4 Mod                                     |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                         | oture 4 module is                                   |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 0 = Input Cap                             | oture 4 module is                                   | s enabled      |                   |                 |                 |       |  |  |  |  |  |  |

| bit 10       | IC3MD: Input                              | IC3MD: Input Capture 3 Module Disable bit           |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 1 = Input Capture 3 module is disabled    |                                                     |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 0 = Input Capture 3 module is enabled     |                                                     |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 9        |                                           | Capture 2 Mod                                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                           | oture 2 module is<br>oture 2 module is              |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 8        | IC1MD: Input Capture 1 Module Disable bit |                                                     |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 1 = Input Cap                             | oture 1 module is<br>oture 1 module is              | s disabled     |                   |                 |                 |       |  |  |  |  |  |  |

| bit 7-4      |                                           | ted: Read as '0                                     |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 3        | OC4MD: Out                                | put Compare 4                                       | Module Disable | e bit             |                 |                 |       |  |  |  |  |  |  |

|              |                                           | 1 = Output Compare 4 module is disabled             |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | -                                         | ompare 4 modu                                       |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 2        |                                           | put Compare 3                                       |                | e bit             |                 |                 |       |  |  |  |  |  |  |

|              | •                                         | ompare 3 modul                                      |                |                   |                 |                 |       |  |  |  |  |  |  |

| L:1 4        | -                                         | ompare 3 modul                                      |                | . h.:4            |                 |                 |       |  |  |  |  |  |  |

| bit 1        |                                           | put Compare 2                                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | $\perp$ – Output Co                       | ompare 2 modu                                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 0 = Output Co                             | ompare 2 modul                                      | le is enabled  |                   |                 |                 |       |  |  |  |  |  |  |

| bit 0        |                                           | ompare 2 modul<br>put Compare 1                     |                | e bit             |                 |                 |       |  |  |  |  |  |  |

| bit 0        | OC1MD: Out                                | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable | e bit             |                 |                 |       |  |  |  |  |  |  |

#### ~

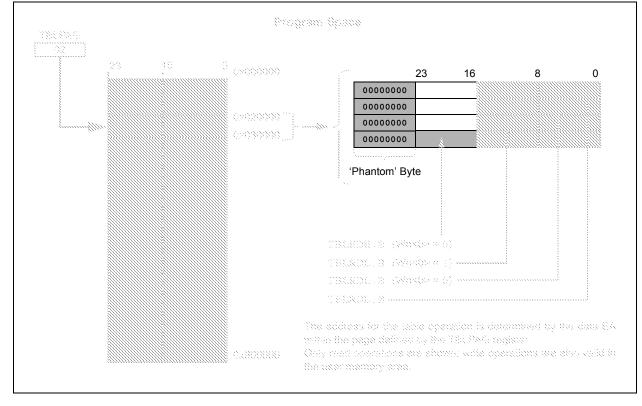

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 22.2 CTMU Control Registers

| REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1                                                                                                                    |            |                                             |         |                   |                  |                        |        |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------|---------|-------------------|------------------|------------------------|--------|--|--|--|--|--|

| R/W-0                                                                                                                                                               | U-0        | R/W-0                                       | R/W-0   | R/W-0             | R/W-0            | R/W-0                  | R/W-0  |  |  |  |  |  |

| CTMUEN                                                                                                                                                              | _          | CTMUSIDL                                    | TGEN    | EDGEN             | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |  |  |  |  |

| bit 15                                                                                                                                                              |            |                                             |         |                   |                  |                        | bit 8  |  |  |  |  |  |

|                                                                                                                                                                     |            |                                             |         |                   |                  |                        |        |  |  |  |  |  |

| U-0                                                                                                                                                                 | U-0        | U-0                                         | U-0     | U-0               | U-0              | U-0                    | U-0    |  |  |  |  |  |

|                                                                                                                                                                     |            | —                                           | _       |                   | <u> </u>         |                        | _      |  |  |  |  |  |

| bit 7 bit 0                                                                                                                                                         |            |                                             |         |                   |                  |                        |        |  |  |  |  |  |

|                                                                                                                                                                     |            |                                             |         |                   |                  |                        |        |  |  |  |  |  |

| Legend:                                                                                                                                                             |            |                                             |         |                   |                  |                        |        |  |  |  |  |  |

| R = Readable                                                                                                                                                        | e bit      | W = Writable b                              | oit     | U = Unimplen      | nented bit, read | as '0'                 |        |  |  |  |  |  |

| -n = Value at                                                                                                                                                       | POR        | '1' = Bit is set                            |         | '0' = Bit is clea | ared             | x = Bit is unknown     |        |  |  |  |  |  |

| bit 15                                                                                                                                                              | 1 = Module | TMU Enable bit<br>is enabled<br>is disabled |         |                   |                  |                        |        |  |  |  |  |  |

| bit 14                                                                                                                                                              | Unimpleme  | nted: Read as '0                            | 3       |                   |                  |                        |        |  |  |  |  |  |

| bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |            |                                             |         |                   |                  |                        |        |  |  |  |  |  |

| bit 12                                                                                                                                                              | TGEN: Time | Generation Ena                              | ble bit |                   |                  |                        |        |  |  |  |  |  |

### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                | R/W-0               | R/W-0                                                                                                                                             | R/W-0                                                                                                        | R/W-0            | R/W-0           | R/W-0   |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------|-----------------|---------|--|--|--|

| PTGCLK2         | PTGCLK1                                                                                                                                                                                                                                                                                                                                              | PTGCLK0             | PTGDIV4                                                                                                                                           | PTGDIV3                                                                                                      | PTGDIV2          | PTGDIV1         | PTGDIV0 |  |  |  |

| bit 15          | 1                                                                                                                                                                                                                                                                                                                                                    | 1                   | 1                                                                                                                                                 |                                                                                                              | 1                |                 | bit     |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                | R/W-0               | R/W-0                                                                                                                                             | U-0                                                                                                          | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| PTGPWD3         | PTGPWD2                                                                                                                                                                                                                                                                                                                                              | PTGPWD1             | PTGPWD0                                                                                                                                           | _                                                                                                            | PTGWDT2          | PTGWDT1         | PTGWDTC |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                      |                     |                                                                                                                                                   |                                                                                                              |                  |                 | bit     |  |  |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                      |                     |                                                                                                                                                   |                                                                                                              |                  |                 |         |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                                                  | W = Writable        | bit                                                                                                                                               | U = Unimpler                                                                                                 | mented bit, read | l as '0'        |         |  |  |  |

| -n = Value at F | POR                                                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set    |                                                                                                                                                   | '0' = Bit is cle                                                                                             | ared             | x = Bit is unkr | nown    |  |  |  |

| bit 15-13       | 111 = Reserv<br>110 = Reserv<br>101 = PTG m<br>100 = PTG m<br>011 = PTG m<br>010 = PTG m<br>001 = PTG m                                                                                                                                                                                                                                              |                     | urce will be T3<br>urce will be T2<br>urce will be T1<br>urce will be TA<br>urce will be Fc                                                       | SCLK<br>SCLK<br>CLK<br>D<br>DSC                                                                              |                  |                 |         |  |  |  |

| bit 12-8        | 11111 = Divio<br>11110 = Divio<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                    | de-by-31<br>de-by-2 | Clock Presca                                                                                                                                      | ler (divider) bi                                                                                             | ts               |                 |         |  |  |  |

| bit 7-4         | 00001 = Divide-by-2<br>00000 = Divide-by-1<br><b>PTGPWD&lt;3:0&gt;:</b> PTG Trigger Output Pulse-Width bits<br>1111 = All trigger outputs are 16 PTG clock cycles wide<br>1110 = All trigger outputs are 15 PTG clock cycles wide<br>0001 = All trigger outputs are 2 PTG clock cycles wide<br>0000 = All trigger outputs are 1 PTG clock cycle wide |                     |                                                                                                                                                   |                                                                                                              |                  |                 |         |  |  |  |

| bit 3           | Unimplemen                                                                                                                                                                                                                                                                                                                                           | ted: Read as '      | 0'                                                                                                                                                |                                                                                                              |                  |                 |         |  |  |  |

| bit 2-0         | PTGWDT<2:0<br>111 = Watcho<br>110 = Watcho<br>101 = Watcho<br>011 = Watcho<br>011 = Watcho<br>010 = Watcho<br>010 = Watcho                                                                                                                                                                                                                           |                     | Watchdog Tir<br>ime-out after 5<br>ime-out after 2<br>ime-out after 1<br>ime-out after 3<br>ime-out after 3<br>ime-out after 3<br>ime-out after 8 | 12 PTG clock<br>56 PTG clock<br>28 PTG clock<br>4 PTG clocks<br>2 PTG clocks<br>6 PTG clocks<br>6 PTG clocks | S<br>S           | 5               |         |  |  |  |

# REGISTER 24-2: PTGCON: PTG CONTROL REGISTER

# 25.1 Op Amp Application Considerations

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

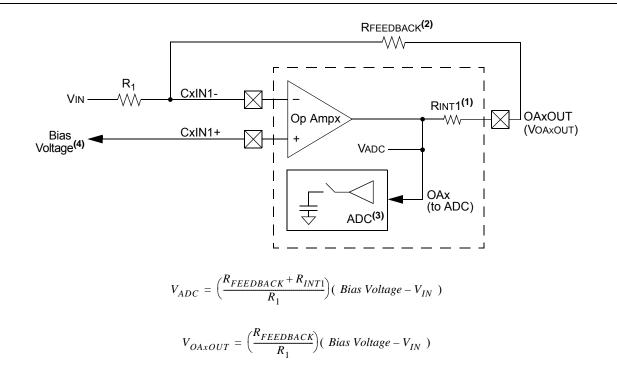

## 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

### FIGURE 25-6: OP AMP CONFIGURATION A

Note 1: See Table 30-53 for the Typical value.

- 2: See Table 30-53 for the Minimum value for the feedback resistor.

- 3: See Table 30-60 and Table 30-61 for the minimum sample time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

| DC CHARACTERISTICS |        |                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                                               |  |

|--------------------|--------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                          | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions                                                                                                                                    |  |

|                    | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                                                                                                                                                                                                                                                                       |      |      |       |                                                                                                                                               |  |

| DI50               |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                                                                                                                                                                                                                                                    | —    | +1   | μA    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in at high-impedance} \end{split}$                         |  |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |  |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |  |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                      |  |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |  |

| DI55               |        | MCLR                                    | -5                                                                                                                                                                                                                                                                                    | —    | +5   | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |  |