Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202-h-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                                                    | 25  |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             | 123 |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           | 153 |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

| 16.0  | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     | 225 |

| 17.0  | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) | 249 |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

| 19.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      | 273 |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                                 | 281 |

| 21.0  | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    | 287 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                                                | 315 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    | 321 |

| 24.0  | Peripheral Trigger Generator (PTG) Module                                                          | 337 |

|       | Op Amp/Comparator Module                                                                           |     |

| 26.0  | Programmable Cyclic Redundancy Check (CRC) Generator                                               | 373 |

| 27.0  | Special Features                                                                                   | 379 |

| 28.0  | Instruction Set Summary                                                                            | 387 |

| 29.0  | Development Support                                                                                | 397 |

| 30.0  | Electrical Characteristics                                                                         | 401 |

| 31.0  | High-Temperature Electrical Characteristics                                                        | 467 |

| 32.0  | DC and AC Device Characteristics Graphs                                                            | 475 |

| 33.0  | Packaging Information                                                                              | 479 |

|       | endix A: Revision History                                                                          |     |

| Index | X                                                                                                  | 517 |

| The I | Microchip Web Site                                                                                 | 525 |

| Cust  | omer Change Notification Service                                                                   | 525 |

| Cust  | omer Support                                                                                       | 525 |

| Prod  | uct Identification System                                                                          | 527 |

TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9     | Bit 8 | Bit 7       | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1      | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|-----------|-------|-------------|---------|-------------|---------|---------|--------|------------|--------|---------------|

| IPC35        | 0886  | 1      | ,      | JTAGIP<2:0 | )>      | _       |        | ICDIP<2:0 | >     | 1           | _       | -           | 1       | _       | _      | _          | _      | 4400          |

| IPC36        | 0888  | -      | ı      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<   | 2:0>  | ı           | P       | TGSTEPIP<2  | :0>     | _       | -      | ı          | -      | 4440          |

| IPC37        | 088A  | -      | _      | _          | _       | _       | P      | TG3IP<2:0 | )>    | ı           |         | PTG2IP<2:0> | >       | _       | F      | TG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE     | COVTE | SFTACERR    | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL    | -      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | -       | _       | _      | _         | -     | ı           | _       | _           | ı       | _       | INT2EP | INT1EP     | INT0EP | 8000          |

| INTCON3      | 08C4  | ı      | _      | _          | -       | _       | _      | _         | -     | ı           | _       | DAE         | DOOVR   | _       | -      | ı          | -      | 0000          |

| INTCON4      | 08C6  | -      | _      | _          | _       | _       | _      | _         | _     | -           | _       | _           |         | _       | _      | _          | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _          | _       |         | ILR<   | 3:0>      |       | VECNUM<7:0> |         |             |         |         |        | 0000       |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | 1      | -      | -      | CMPMD  | _      | _      | CRCMD  | -     | _     | -      | -      | -      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | 1      | -      | -      | _      | _      | _      | _      | -     | _     | -      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | _      | 1      | -      | -      | PWM3MD | PWM2MD | PWM1MD | _      | -     | _     | -      | -      | -      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVIDI       | 0760  | _      | _      | _      | _      | _      | _      |        | _      | _      | _     | _     | DMA2MD | PIGND  | _      | _      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | INT2R<6:0> |       |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 INT2R<6:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | T2CKR<6:0> | •     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

# REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

## REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER (2)

| R/W-1  | R/W-1 | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0  | R/W-0  |

|--------|-------|-------|-------|----------------------|----------------------|--------|--------|

| PENH   | PENL  | POLH  | POLL  | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup> | OVRENH | OVRENL |

| bit 15 |       |       |       |                      |                      |        | bit 8  |

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|---------|---------|---------|---------|--------|--------|-------|-------|

| OVRDAT1 | OVRDAT0 | FLTDAT1 | FLTDAT0 | CLDAT1 | CLDAT0 | SWAP  | OSYNC |

| bit 7   |         |         |         |        |        |       | bit 0 |

Legend:

bit 12

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared -n = Value at POR x = Bit is unknown

bit 15 PENH: PWMxH Output Pin Ownership bit

1 = PWMx module controls PWMxH pin

0 = GPIO module controls PWMxH pin

bit 14 PENL: PWMxL Output Pin Ownership bit

1 = PWMx module controls PWMxL pin

0 = GPIO module controls PWMxL pin

bit 13 POLH: PWMxH Output Pin Polarity bit

> 1 = PWMxH pin is active-low 0 = PWMxH pin is active-high

POLL: PWMxL Output Pin Polarity bit

1 = PWMxL pin is active-low

0 = PWMxL pin is active-high

PMOD<1:0>: PWMx # I/O Pin Mode bits(1) bit 11-10

11 = Reserved; do not use

10 = PWMx I/O pin pair is in the Push-Pull Output mode

01 = PWMx I/O pin pair is in the Redundant Output mode

00 = PWMx I/O pin pair is in the Complementary Output mode

bit 9 **OVRENH:** Override Enable for PWMxH Pin bit

1 = OVRDAT<1> controls output on PWMxH pin

0 = PWMx generator controls PWMxH pin

bit 8 **OVRENL:** Override Enable for PWMxL Pin bit

1 = OVRDAT<0> controls output on PWMxL pin

0 = PWMx generator controls PWMxL pin

bit 7-6 OVRDAT<1:0>: Data for PWMxH, PWMxL Pins if Override is Enabled bits

If OVERENH = 1, PWMxH is driven to the state specified by OVRDAT<1>.

If OVERENL = 1, PWMxL is driven to the state specified by OVRDAT<0>.

FLTDAT<1:0>: Data for PWMxH and PWMxL Pins if FLTMOD is Enabled bits bit 5-4

If Fault is active, PWMxH is driven to the state specified by FLTDAT<1>.

If Fault is active, PWMxL is driven to the state specified by FLTDAT<0>.

bit 3-2 CLDAT<1:0>: Data for PWMxH and PWMxL Pins if CLMOD is Enabled bits

If current-limit is active, PWMxH is driven to the state specified by CLDAT<1>.

If current-limit is active, PWMxL is driven to the state specified by CLDAT<0>.

**Note 1:** These bits should not be changed after the PWMx module is enabled (PTEN = 1).

If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

# 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs react to complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en555464

### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1)

- 1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect

- 0 = Address Detect mode is disabled

- bit 4 RIDLE: Receiver Idle bit (read-only)

- 1 = Receiver is Idle

- 0 = Receiver is active

- bit 3 **PERR:** Parity Error Status bit (read-only)

- 1 = Parity error has been detected for the current character (character at the top of the receive FIFO)

- 0 = Parity error has not been detected

- bit 2 **FERR:** Framing Error Status bit (read-only)

- 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)

- 0 = Framing error has not been detected

- bit 1 OERR: Receive Buffer Overrun Error Status bit (clear/read-only)

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1  $\rightarrow$  0 transition) resets the receiver buffer and the UxRSR to the empty state

- bit 0 URXDA: UARTx Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for transmit operation.

#### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-------|-------|-------|-----------|-------|-------|-------|--|

|        | F7BP< | <3:0> |       | F6BP<3:0> |       |       |       |  |

| bit 15 |       |       |       |           |       |       | bit 8 |  |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | F5BP< | <3:0> |       |       | F4BP  | <3:0> |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F7BP<3:0>: RX Buffer Mask for Filter 7 bits

1111 = Filter hits received in RX FIFO buffer

1110 = Filter hits received in RX Buffer 14

•

0001 = Filter hits received in RX Buffer 1

0000 = Filter hits received in RX Buffer 0

bit 11-8 F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>)

bit 7-4 F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>)

bit 3-0 F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>)

### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 |

|--------|-------|-------|-------|-------|-------|--------|-------|

|        | F11BP | <3:0> |       |       | F10BF | P<3:0> |       |

| bit 15 |       |       |       |       |       |        | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | F9BP< | <3:0> |       |       | F8BP  | <3:0> |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F11BP<3:0>: RX Buffer Mask for Filter 11 bits

1111 = Filter hits received in RX FIFO buffer

1110 = Filter hits received in RX Buffer 14

•

0001 = Filter hits received in RX Buffer 1

0000 = Filter hits received in RX Buffer 0

bit 11-8 F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bits<15:12>)

bit 7-4 F9BP<3:0>: RX Buffer Mask for Filter 9 bits (same values as bits<15:12>)

bit 3-0 **F8BP<3:0>:** RX Buffer Mask for Filter 8 bits (same values as bits<15:12>)

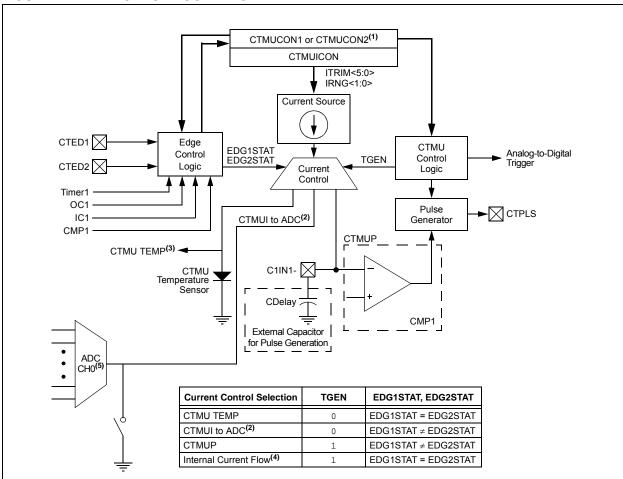

FIGURE 22-1: CTMU BLOCK DIAGRAM

- Note 1: When the CTMU is not actively used, set TGEN = 1, and ensure that EDG1STAT = EDG2STAT. All other settings allow current to flow into the ADC or the C1IN1- pin. If using the ADC for other purposes besides the CTMU, set IDISSEN = 0. If IDISSEN is set to '1', it will short the output of the ADC CH0 MUX to Vss.

- 2: CTMUI connects to the output of the ADC CH0 MUX. When CTMU current is steered into this node, the current will flow out through the selected ADC channel determined by the CH0 MUX (see the CH0Sx bits in the AD1CHS0 register).

- 3: CTMU TEMP connects to one of the ADC CH0 inputs; see CH0SA and CH0SB (AD1CHS0<12:8,4:0).

- 4: If TGEN = 1 and EDG1STAT = EDG2STAT, CTMU current source is still enabled and may be shunted to Vss internally. This should be considered in low-power applications.

- 5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

# 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0 CH123SA: Channel 1, 2, 3 Positive Input Select for Sample MUXA bit

In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value        |         | ADC Channel |         |  |

|--------------|---------|-------------|---------|--|

| value        | CH1     | CH2         | СНЗ     |  |

| <b>1</b> (2) | OA1/AN3 | OA2/AN0     | OA3/AN6 |  |

| 0(1,2)       | OA2/AN0 | AN1         | AN2     |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

## REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

```

CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits(1)

bit 4-0

11111 = Open; use this selection with CTMU capacitive and time measurement

11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP)

11101 = Reserved

11100 = Reserved

11011 = Reserved

11010 = Channel 0 positive input is the output of OA3/AN6<sup>(2,3)</sup>

11001 = Channel 0 positive input is the output of OA2/AN0<sup>(2)</sup>

11000 = Channel 0 positive input is the output of OA1/AN3<sup>(2)</sup>

10110 = Reserved

10000 = Reserved

01111 = Channel 0 positive input is AN15<sup>(1,3)</sup>

01110 = Channel 0 positive input is AN14<sup>(1,3)</sup>

01101 = Channel 0 positive input is AN13<sup>(1,3)</sup>

00010 = Channel 0 positive input is AN2(1,3)

00001 = Channel 0 positive input is AN1<sup>(1,3)</sup>

00000 = Channel 0 positive input is AN0^{(1,3)}

```

- Note 1: AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- **3:** See the "Pin Diagrams" section for the available analog channels for each device.

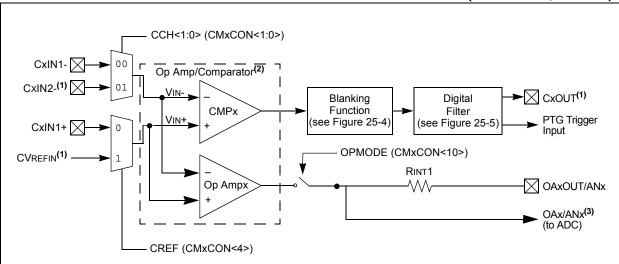

# 25.0 OP AMP/COMPARATOR MODULE

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

## FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

- Note 1: This input/output is not available as a selection when configured as an op amp (OPMODE (CMxCON<10>) = 1).

- 2: This module can be configured either as an op amp or a comparator using the OPMODE bit.

- 3: When configured as an op amp (OPMODE = 1), the ADC samples the op amp output; otherwise, the ADC samples the ANx pin.

### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

## 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS |                                |               | Standard Opera<br>(unless otherwi<br>Operating temperating temperating temperating temperating temperature) | erature -40°C ≤ Ta ≤ +85 | 3.6V<br>5°C for Industrial<br>25°C for Extended |  |  |  |

|--------------------|--------------------------------|---------------|-------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------|--|--|--|

| Parameter<br>No.   | Тур.                           | Max.          | Units Conditions                                                                                            |                          |                                                 |  |  |  |

| Power-Down (       | Current (IPD) <sup>(1)</sup> – | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                             | 232MC20X/50X and PIC2    | 24EP32GP/MC20X                                  |  |  |  |

| DC60d              | 30                             | 100           | μΑ                                                                                                          | -40°C                    |                                                 |  |  |  |

| DC60a              | 35                             | 100           | μΑ                                                                                                          | +25°C                    | 3.3V                                            |  |  |  |

| DC60b              | 150                            | 200           | μΑ                                                                                                          | +85°C                    | 3.37                                            |  |  |  |

| DC60c              | 250                            | 500           | μΑ                                                                                                          | +125°C                   |                                                 |  |  |  |

| Power-Down (       | Current (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                             | P64MC20X/50X and PIC2    | 24EP64GP/MC20X                                  |  |  |  |

| DC60d              | 25                             | 100           | μΑ                                                                                                          | -40°C                    |                                                 |  |  |  |

| DC60a              | 30                             | 100           | μΑ                                                                                                          | +25°C                    | 3 31/                                           |  |  |  |

| DC60b              | 150                            | 350           | μΑ                                                                                                          | +85°C                    | 3.3V                                            |  |  |  |

| DC60c              | 350                            | 800           | μΑ                                                                                                          | +125°C                   |                                                 |  |  |  |

| Power-Down C       | Current (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                                                                              | P128MC20X/50X and PIC    | C24EP128GP/MC20X                                |  |  |  |

| DC60d              | 30                             | 100           | μΑ                                                                                                          | -40°C                    |                                                 |  |  |  |

| DC60a              | 35                             | 100           | μА                                                                                                          | +25°C                    | 3.3V                                            |  |  |  |

| DC60b              | 150                            | 350           | μΑ                                                                                                          | +85°C                    | 3.5 v                                           |  |  |  |

| DC60c              | 550                            | 1000          | μΑ                                                                                                          | +125°C                   |                                                 |  |  |  |

| Power-Down C       | Current (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                                                                              | P256MC20X/50X and PIC    | C24EP256GP/MC20X                                |  |  |  |

| DC60d              | 35                             | 100           | μΑ                                                                                                          | -40°C                    |                                                 |  |  |  |

| DC60a              | 40                             | 100           | μΑ                                                                                                          | +25°C                    | 3.3V                                            |  |  |  |

| DC60b              | 250                            | 450           | μА                                                                                                          | +85°C                    | 3.5V                                            |  |  |  |

| DC60c              | 1000                           | 1200          | μА                                                                                                          | +125°C                   |                                                 |  |  |  |

| Power-Down C       | Current (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                                                                              | P512MC20X/50X and PIC    | C24EP512GP/MC20X                                |  |  |  |

| DC60d              | 40                             | 100           | μА                                                                                                          | -40°C                    |                                                 |  |  |  |

| DC60a              | 45                             | 100           | μΑ                                                                                                          | +25°C                    | 3.3V                                            |  |  |  |

| DC60b              | 350                            | 800           | μΑ                                                                                                          | +85°C                    | J.JV                                            |  |  |  |

| DC60c              | 1100                           | 1500          | μА                                                                                                          | +125°C                   |                                                 |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- · JTAG is disabled

TABLE 30-48: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)

TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Op<br>(unless other<br>Operating te | erwise st           | <b>ated)</b><br>e -40° | C ≤ Ta ≤ | V to 3.6V<br>:+85°C for Industrial<br>:+125°C for Extended |

|--------------------|-----------------------|--------------------------------------------|----------------------------------------------|---------------------|------------------------|----------|------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                         | Typ. <sup>(2)</sup> | Max.                   | Units    | Conditions                                                 |

| SP70               | FscP                  | Maximum SCK1 Input Frequency               | _                                            | _                   | 11                     | MHz      | (Note 3)                                                   |

| SP72               | TscF                  | SCK1 Input Fall Time                       | _                                            | _                   | _                      | ns       | See Parameter DO32 (Note 4)                                |

| SP73               | TscR                  | SCK1 Input Rise Time                       | _                                            | _                   | _                      | ns       | See Parameter DO31 (Note 4)                                |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                 | _                                            | _                   | _                      | ns       | See Parameter DO32 (Note 4)                                |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                 | _                                            | _                   | _                      | ns       | See Parameter DO31 (Note 4)                                |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge  | _                                            | 6                   | 20                     | ns       |                                                            |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to First SCK1 Edge  | 30                                           | _                   | _                      | ns       |                                                            |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge | 30                                           | _                   | _                      | ns       |                                                            |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge  | 30                                           | _                   | _                      | ns       |                                                            |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓ Input            | 120                                          | _                   | _                      | ns       |                                                            |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance     | 10                                           | _                   | 50                     | ns       | (Note 4)                                                   |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                      | 1.5 Tcy + 40                                 | _                   | _                      | ns       | (Note 4)                                                   |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

TABLE 30-61: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                                                     | (unless                             |         | <b>e stated)<sup>(</sup></b><br>ature -4 | <b>1)</b><br>0°C ≤ TA | OV to 3.6V<br>≤ +85°C for Industrial<br>≤ +125°C for Extended |

|--------------------|--------|-----------------------------------------------------------------------------------------------------|-------------------------------------|---------|------------------------------------------|-----------------------|---------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                      | Characteristic Min. Typ. Max. Units |         |                                          |                       | Conditions                                                    |

|                    |        | Clock                                                                                               | k Parame                            | ters    |                                          |                       |                                                               |

| AD50               | TAD    | ADC Clock Period                                                                                    | 76                                  | _       | _                                        | ns                    |                                                               |

| AD51               | trc    | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                    | _                                   | 250     | _                                        | ns                    |                                                               |

|                    |        | Con                                                                                                 | version F                           | Rate    |                                          |                       |                                                               |

| AD55               | tconv  | Conversion Time                                                                                     | _                                   | 12 TAD  | _                                        | _                     |                                                               |

| AD56               | FCNV   | Throughput Rate                                                                                     | _                                   | _       | 1.1                                      | Msps                  | Using simultaneous sampling                                   |

| AD57a              | Тѕамр  | Sample Time when Sampling any ANx Input                                                             | 2 TAD                               | _       | _                                        | _                     |                                                               |

| AD57b              | TSAMP  | Sample Time when Sampling the Op Amp Outputs (Configuration A and Configuration B) <sup>(4,5)</sup> | 4 TAD                               | _       | _                                        | _                     |                                                               |

|                    | -      | Timin                                                                                               | g Param                             | eters   |                                          |                       |                                                               |

| AD60               | tPCS   | Conversion Start from Sample Trigger <sup>(2,3)</sup>                                               | 2 TAD                               | _       | 3 TAD                                    | _                     | Auto-convert trigger is not selected                          |

| AD61               | tPSS   | Sample Start from Setting Sample (SAMP) bit (2,3))                                                  | 2 TAD                               | _       | 3 TAD                                    | _                     |                                                               |

| AD62               | tcss   | Conversion Completion to Sample Start (ASAM = $1$ ) <sup>(2,3)</sup>                                | _                                   | 0.5 TAD | _                                        | _                     |                                                               |

| AD63               | tDPU   | Time to Stabilize Analog Stage from ADC Off to ADC On(2,3)                                          | _                                   | _       | 20                                       | μS                    | (Note 6)                                                      |

- **Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- **5:** See Figure 25-7 for configuration information.

- **6:** The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

#### TABLE 30-62: DMA MODULE TIMING REQUIREMENTS

| AC CH        | CHARACTERISTICS                |                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |            |  |  |

|--------------|--------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|

| Param<br>No. | Characteristic                 | Min.                 | Typ. <sup>(1)</sup>                                                                                                                                                                                                                              | Max. | Units | Conditions |  |  |

| DM1          | DMA Byte/Word Transfer Latency | 1 Tcy <sup>(2)</sup> | _                                                                                                                                                                                                                                                | _    | ns    |            |  |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

### 33.0 PACKAGING INFORMATION

## 33.1 Package Marking Information

### 28-Lead SPDIP

### Example

## 28-Lead SOIC (.300")

## Example

### 28-Lead SSOP

### Example

## 28-Lead QFN-S (6x6x0.9 mm)

# Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note:** In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

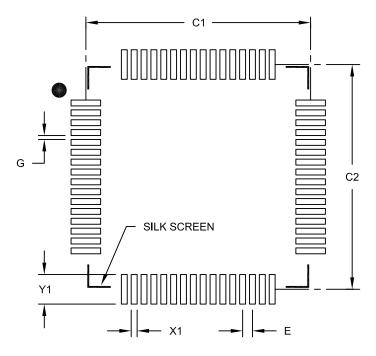

# 64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | N   | <b>ILLIMETER</b> | S        |      |

|--------------------------|-----|------------------|----------|------|

| Dimension                | MIN | NOM              | MAX      |      |

| Contact Pitch            | Е   |                  | 0.50 BSC |      |

| Contact Pad Spacing      | C1  |                  | 11.40    |      |

| Contact Pad Spacing      | C2  |                  | 11.40    |      |

| Contact Pad Width (X64)  | X1  |                  |          | 0.30 |

| Contact Pad Length (X64) | Y1  |                  |          | 1.50 |

| Distance Between Pads    | G   | 0.20             |          |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

| PMD (PIC24EPXXXMC20X Devices)94             | CMxMSKCON (Comparator x Mask              |     |

|---------------------------------------------|-------------------------------------------|-----|

| PORTA (PIC24EPXXXGP/MC202,                  | Gating Control)                           | 368 |

| dsPIC33EPXXXGP/MC202/502 Devices) 104       | CMxMSKSRC (Comparator x Mask Source       |     |

| PORTA (PIC24EPXXXGP/MC203,                  | Select Control)                           | 366 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103       | CORCON (Core Control)4                    |     |

| PORTA (PIC24EPXXXGP/MC204,                  | CRCCON1 (CRC Control 1)                   |     |

| dsPIC33EPXXXGP/MC204/504 Devices) 102       | CRCCON2 (CRC Control 2)                   |     |

| PORTA (PIC24EPXXXGP/MC206,                  | CRCXORH (CRC XOR Polynomial High)         |     |

| ·                                           |                                           |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 99        | CRCXORL (CRC XOR Polynomial Low)          |     |

| PORTB (PIC24EPXXXGP/MC202,                  | CTMUCON1 (CTMU Control 1)                 |     |

| dsPIC33EPXXXGP/MC202/502 Devices) 104       | CTMUCON2 (CTMU Control 2)                 |     |

| PORTB (PIC24EPXXXGP/MC203,                  | CTMUICON (CTMU Current Control)           | 319 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103       | CVRCON (Comparator Voltage                |     |

| PORTB (PIC24EPXXXGP/MC204,                  | Reference Control)                        | 371 |

| dsPIC33EPXXXGP/MC204/504 Devices) 102       | CxBUFPNT1 (ECANx Filter 0-3               |     |

| PORTB (PIC24EPXXXGP/MC206,                  | Buffer Pointer 1)                         | 300 |

| dsPIC33EPXXXGP/MC206/506 Devices) 99        | CxBUFPNT2 (ECANx Filter 4-7               |     |

| PORTC (PIC23EPXXXGP/MC203,                  | Buffer Pointer 2)                         | 301 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103       | CxBUFPNT3 (ECANx Filter 8-11              |     |

| PORTC (PIC24EPXXXGP/MC204,                  | Buffer Pointer 3)                         | 301 |

| dsPIC33EPXXXGP/MC204/504 Devices) 102       | CxBUFPNT4 (ECANx Filter 12-15             |     |

| PORTC (PIC24EPXXXGP/MC206,                  | Buffer Pointer 4)                         | 302 |

| dsPIC33EPXXXGP/MC206/506 Devices) 99        | CxCFG1 (ECANx Baud Rate Configuration 1)  |     |

| PORTD (PIC24EPXXXGP/MC206,                  | CxCFG2 (ECANx Baud Rate Configuration 2)  |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100       | CxCTRL1 (ECANx Control 1)                 |     |

| PORTE (PIC24EPXXXGP/MC206,                  | CxCTRL2 (ECANx Control 2)                 |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100       | CxEC (ECANx Transmit/Receive Error Count) |     |

| PORTF (PIC24EPXXXGP/MC206,                  | CxFCTRL (ECANx FIFO Control)              |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100       | CxFEN1 (ECANx Acceptance Filter Enable 1) |     |

| PORTG (PIC24EPXXXGP/MC206 and               | CxFIFO (ECANx FIFO Status)                |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 101       | CxFMSKSEL1 (ECANx Filter 7-0              | 254 |

| PTG78                                       | Mask Selection 1)                         | 304 |

| PWM (dsPIC33EPXXXMC20X/50X,                 | CxFMSKSEL2 (ECANx Filter 15-8             | 304 |

| PIC24EPXXXMC20X Devices)79                  | Mask Selection 2)                         | 305 |

| ·                                           |                                           |     |

| PWM Generator 1 (dsPIC33EPXXXMC20X/50X,     | CXINTE (ECANX Interrupt Enable)           |     |

| PIC24EPXXXMC20X Devices)                    | CXINTF (ECANx Interrupt Flag)             | 295 |

| PWM Generator 2 (dsPIC33EPXXXMC20X/50X,     | CxRXFnEID (ECANx Acceptance Filter n      | 204 |

| PIC24EPXXXMC20X Devices)                    | Extended Identifier)                      | 304 |

| PWM Generator 3 (dsPIC33EPXXXMC20X/50X,     | CxRXFnSID (ECANx Acceptance Filter n      | 202 |

| PIC24EPXXXMC20X Devices)80                  | Standard Identifier)                      |     |

| QEI1 (dsPIC33EPXXXMC20X/50X,                | CxRXFUL1 (ECANx Receive Buffer Full 1)    |     |

| PIC24EPXXXMC20X Devices)81                  | CxRXFUL2 (ECANx Receive Buffer Full 2)    | 307 |

| Reference Clock                             | CxRXMnEID (ECANx Acceptance Filter Mask n | 000 |

| SPI1 and SPI2                               | Extended Identifier)                      | 306 |

| System Control93                            | CxRXMnSID (ECANx Acceptance Filter Mask n |     |

| Time1 through Time575                       | Standard Identifier)                      | 306 |

| UART1 and UART282                           | CxRXOVF1 (ECANx Receive                   |     |

| Registers                                   | Buffer Overflow 1)                        | 308 |

| AD1CHS0 (ADC1 Input Channel 0 Select)       | CxRXOVF2 (ECANx Receive                   |     |

| AD1CHS123 (ADC1 Input                       | Buffer Overflow 2)                        | 308 |

| Channel 1, 2, 3 Select) 331                 | CxTRmnCON (ECANx TX/RX                    |     |

| AD1CON1 (ADC1 Control 1)325                 | Buffer mn Control)                        | 309 |

| AD1CON2 (ADC1 Control 2)                    | CxVEC (ECANx Interrupt Code)              | 292 |

| AD1CON3 (ADC1 Control 3)329                 | DEVID (Device ID)                         | 383 |

| AD1CON4 (ADC1 Control 4)                    | DEVREV (Device Revision)                  |     |

| AD1CSSH (ADC1 Input Scan Select High) 335   | DMALCA (DMA Last Channel Active Status)   |     |

| AD1CSSL (ADC1 Input Scan Select Low)336     | DMAPPS (DMA Ping-Pong Status)             |     |

| ALTDTRx (PWMx Alternate Dead-Time)238       | DMAPWC (DMA Peripheral Write              |     |

| AUXCONx (PWMx Auxiliary Control)247         | Collision Status)                         | 148 |

| CHOP (PWMx Chop Clock Generator)234         | DMARQC (DMA Request Collision Status)     |     |

| CLKDIV (Clock Divisor)158                   | DMAXCNT (DMA Channel x Transfer Count)    |     |

| CM4CON (Comparator 4 Control)               | DMAXCON (DMA Channel x Control)           |     |

| CMSTAT (Op Amp/Comparator Status)360        | DMAXPAD (DMA Channel x                    | 172 |

| CMxCON (Comparator x Control, x = 1,2,3)362 | Peripheral Address)                       | 116 |

| CMxFLTR (Comparator x Filter Control)370    | DMAxREQ (DMA Channel x IRQ Select)        |     |

| CIVINI LTA (COMPARATOR & FILLER CONTROL)    | DIMAKNER (DIMA CHAITHELY INC. SELECT)     | 143 |