Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202t-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

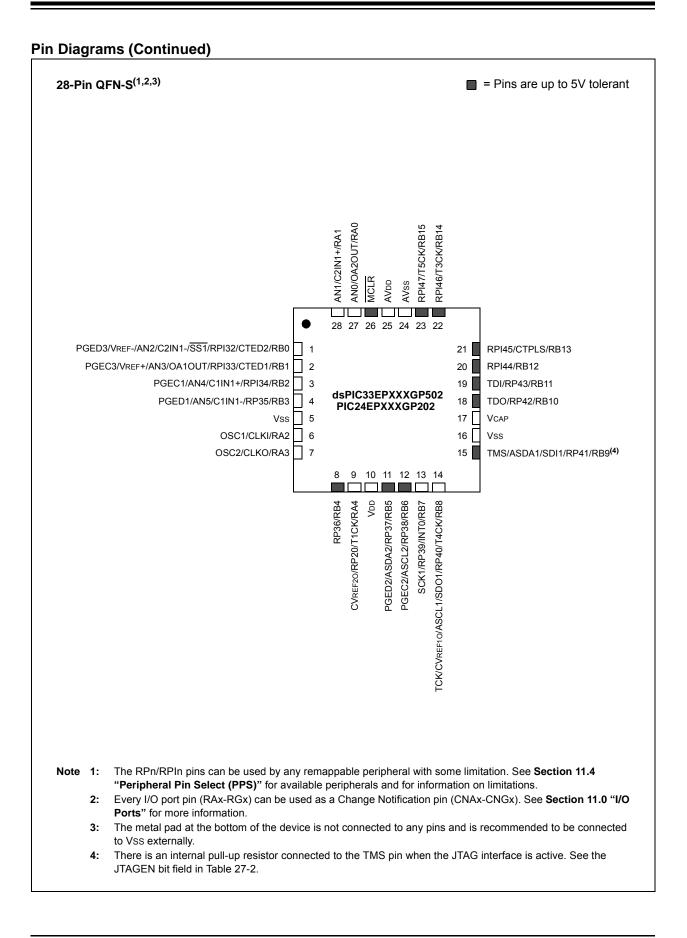

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |  |  |  |  |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |  |  |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |  |  |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |  |  |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |  |  |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |  |  |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |  |  |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |  |  |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |  |  |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |  |  |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |  |  |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |  |  |  |  |

| C3IN2-                        | I.          | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |  |  |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |  |  |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |  |  |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |  |  |  |  |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |  |  |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |  |  |  |  |

| C4OUT                         | 0           |                | Yes     |                                                                                                 |  |  |  |  |

| CVREF10                       | 0           | Analog         | No      | - p - p p                                                                                       |  |  |  |  |

| CVREF20                       | 0           | Analog         | No      |                                                                                                 |  |  |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |  |  |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |  |  |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |  |  |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |  |  |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |  |  |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |  |  |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |  |  |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |  |  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |  |  |  |  |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |  |  |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |  |  |  |  |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |  |  |  |  |

| VREF+                         | 1           | Analog         | No      |                                                                                                 |  |  |  |  |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |  |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |  |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3** "**On-Chip Voltage Regulator**" for details.

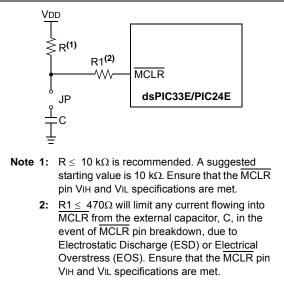

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

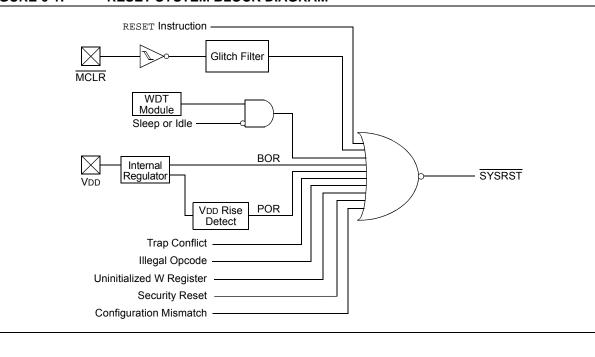

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

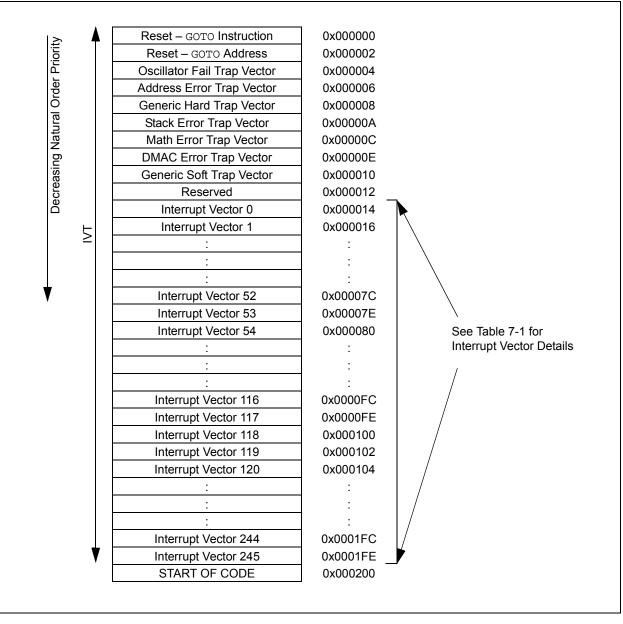

### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

|                                               | Vector | IRQ        |                   | Interrupt Bit Location |          |             |  |

|-----------------------------------------------|--------|------------|-------------------|------------------------|----------|-------------|--|

| Interrupt Source                              | #      | #          | IVT Address       | Flag                   | Enable   | Priority    |  |

|                                               | High   | est Natura | al Order Priority |                        |          |             |  |

| INT0 – External Interrupt 0                   | 8      | 0          | 0x000014          | IFS0<0>                | IEC0<0>  | IPC0<2:0>   |  |

| IC1 – Input Capture 1                         | 9      | 1          | 0x000016          | IFS0<1>                | IEC0<1>  | IPC0<6:4>   |  |

| OC1 – Output Compare 1                        | 10     | 2          | 0x000018          | IFS0<2>                | IEC0<2>  | IPC0<10:8>  |  |

| T1 – Timer1                                   | 11     | 3          | 0x00001A          | IFS0<3>                | IEC0<3>  | IPC0<14:12> |  |

| DMA0 – DMA Channel 0                          | 12     | 4          | 0x00001C          | IFS0<4>                | IEC0<4>  | IPC1<2:0>   |  |

| IC2 – Input Capture 2                         | 13     | 5          | 0x00001E          | IFS0<5>                | IEC0<5>  | IPC1<6:4>   |  |

| OC2 – Output Compare 2                        | 14     | 6          | 0x000020          | IFS0<6>                | IEC0<6>  | IPC1<10:8>  |  |

| T2 – Timer2                                   | 15     | 7          | 0x000022          | IFS0<7>                | IEC0<7>  | IPC1<14:12> |  |

| T3 – Timer3                                   | 16     | 8          | 0x000024          | IFS0<8>                | IEC0<8>  | IPC2<2:0>   |  |

| SPI1E – SPI1 Error                            | 17     | 9          | 0x000026          | IFS0<9>                | IEC0<9>  | IPC2<6:4>   |  |

| SPI1 – SPI1 Transfer Done                     | 18     | 10         | 0x000028          | IFS0<10>               | IEC0<10> | IPC2<10:8>  |  |

| U1RX – UART1 Receiver                         | 19     | 11         | 0x00002A          | IFS0<11>               | IEC0<11> | IPC2<14:12> |  |

| U1TX – UART1 Transmitter                      | 20     | 12         | 0x00002C          | IFS0<12>               | IEC0<12> | IPC3<2:0>   |  |

| AD1 – ADC1 Convert Done                       | 21     | 13         | 0x00002E          | IFS0<13>               | IEC0<13> | IPC3<6:4>   |  |

| DMA1 – DMA Channel 1                          | 22     | 14         | 0x000030          | IFS0<14>               | IEC0<14> | IPC3<10:8>  |  |

| Reserved                                      | 23     | 15         | 0x000032          | _                      | _        | _           |  |

| SI2C1 – I2C1 Slave Event                      | 24     | 16         | 0x000034          | IFS1<0>                | IEC1<0>  | IPC4<2:0>   |  |

| MI2C1 – I2C1 Master Event                     | 25     | 17         | 0x000036          | IFS1<1>                | IEC1<1>  | IPC4<6:4>   |  |

| CM – Comparator Combined Event                | 26     | 18         | 0x000038          | IFS1<2>                | IEC1<2>  | IPC4<10:8>  |  |

| CN – Input Change Interrupt                   | 27     | 19         | 0x00003A          | IFS1<3>                | IEC1<3>  | IPC4<14:12> |  |

| INT1 – External Interrupt 1                   | 28     | 20         | 0x00003C          | IFS1<4>                | IEC1<4>  | IPC5<2:0>   |  |

| Reserved                                      | 29-31  | 21-23      | 0x00003E-0x000042 | —                      | —        | _           |  |

| DMA2 – DMA Channel 2                          | 32     | 24         | 0x000044          | IFS1<8>                | IEC1<8>  | IPC6<2:0>   |  |

| OC3 – Output Compare 3                        | 33     | 25         | 0x000046          | IFS1<9>                | IEC1<9>  | IPC6<6:4>   |  |

| OC4 – Output Compare 4                        | 34     | 26         | 0x000048          | IFS1<10>               | IEC1<10> | IPC6<10:8>  |  |

| T4 – Timer4                                   | 35     | 27         | 0x00004A          | IFS1<11>               | IEC1<11> | IPC6<14:12> |  |

| T5 – Timer5                                   | 36     | 28         | 0x00004C          | IFS1<12>               | IEC1<12> | IPC7<2:0>   |  |

| INT2 – External Interrupt 2                   | 37     | 29         | 0x00004E          | IFS1<13>               | IEC1<13> | IPC7<6:4>   |  |

| U2RX – UART2 Receiver                         | 38     | 30         | 0x000050          | IFS1<14>               | IEC1<14> | IPC7<10:8>  |  |

| U2TX – UART2 Transmitter                      | 39     | 31         | 0x000052          | IFS1<15>               | IEC1<15> | IPC7<14:12> |  |

| SPI2E – SPI2 Error                            | 40     | 32         | 0x000054          | IFS2<0>                | IEC2<0>  | IPC8<2:0>   |  |

| SPI2 – SPI2 Transfer Done                     | 41     | 33         | 0x000056          | IFS2<1>                | IEC2<1>  | IPC8<6:4>   |  |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42     | 34         | 0x000058          | IFS2<2>                | IEC2<2>  | IPC8<10:8>  |  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43     | 35         | 0x00005A          | IFS2<3>                | IEC2<3>  | IPC8<14:12> |  |

| DMA3 – DMA Channel 3                          | 44     | 36         | 0x00005C          | IFS2<4>                | IEC2<4>  | IPC9<2:0>   |  |

| IC3 – Input Capture 3                         | 45     | 37         | 0x00005E          | IFS2<5>                | IEC2<5>  | IPC9<6:4>   |  |

| IC4 – Input Capture 4                         | 46     | 38         | 0x000060          | IFS2<6>                | IEC2<6>  | IPC9<10:8>  |  |

| Reserved                                      | 47-56  | 39-48      | 0x000062-0x000074 | —                      | —        | —           |  |

| SI2C2 – I2C2 Slave Event                      | 57     | 49         | 0x000076          | IFS3<1>                | IEC3<1>  | IPC12<6:4>  |  |

| MI2C2 – I2C2 Master Event                     | 58     | 50         | 0x000078          | IFS3<2>                | IEC3<2>  | IPC12<10:8> |  |

| Reserved                                      | 59-64  | 51-56      | 0x00007A-0x000084 |                        | _        |             |  |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65     | 57         | 0x000086          | IFS3<9>                | IEC3<9>  | IPC14<6:4>  |  |

### TABLE 7-1: INTERRUPT VECTOR DETAILS

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| U-0             | U-0                                                                                          | U-0                                                                                                                                                                     | U-0                                                                             | R-0               | R-0              | R-0             | R-0     |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------|--|--|--|--|

|                 | —                                                                                            |                                                                                                                                                                         |                                                                                 | ILR3              | ILR2             | ILR1            | ILR0    |  |  |  |  |

| bit 15          |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit 8   |  |  |  |  |

| R-0             | R-0                                                                                          | R-0                                                                                                                                                                     | R-0                                                                             | R-0               | R-0              | R-0             | R-0     |  |  |  |  |

| VECNUM7         | VECNUM6                                                                                      | VECNUM5                                                                                                                                                                 | VECNUM4                                                                         | VECNUM3           | VECNUM2          | VECNUM1         | VECNUM0 |  |  |  |  |

| bit 7           |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit C   |  |  |  |  |

| Legend:         |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

| R = Readable    | bit                                                                                          | W = Writable                                                                                                                                                            | bit                                                                             | U = Unimplen      | nented bit, read | as '0'          |         |  |  |  |  |

| -n = Value at I | POR                                                                                          | '1' = Bit is set                                                                                                                                                        |                                                                                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |

| bit 15-12       | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                          | 0'                                                                              |                   |                  |                 |         |  |  |  |  |

| bit 11-8        | ILR<3:0>: New CPU Interrupt Priority Level bits                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | 1111 = CPU Interrupt Priority Level is 15                                                    |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | 0001 = CPU Interrupt Priority Level is 1<br>0000 = CPU Interrupt Priority Level is 0         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

| bit 7-0         | VECNUM<7:0>: Vector Number of Pending Interrupt bits                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | 11111111 = 255, Reserved; do not use                                                         |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |  |  |  |  |

|                 | 00001000 = 8<br>00000111 = 7<br>00000110 = 8<br>00000101 = 8<br>00000100 = 7<br>00000011 = 3 | 9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, DMAC error<br>4, Math error tr<br>3, Stack error t<br>2, Generic hard<br>1, Address erro | rnal Interrupt C<br>o not use<br>error trap<br>trap<br>rap<br>d trap<br>or trap | )                 |                  |                 |         |  |  |  |  |

### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

NOTES:

### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                   | U-0                                                                                            | U-0                                                                             | U-0    | U-0              | U-0              | U-0             | U-0   |  |  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------|------------------|------------------|-----------------|-------|--|--|--|--|--|

| _                     | —                                                                                              | —                                                                               |        | —                | —                | —               | _     |  |  |  |  |  |

| bit 15                |                                                                                                |                                                                                 |        |                  |                  |                 | bit   |  |  |  |  |  |

|                       |                                                                                                |                                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

| R/W-0                 | R/W-0                                                                                          | R/W-0                                                                           | U-0    | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| IVRIE                 | WAKIE                                                                                          | ERRIE                                                                           | —      | FIFOIE           | RBOVIE           | RBIE            | TBIE  |  |  |  |  |  |

| bit 7                 |                                                                                                |                                                                                 |        |                  |                  |                 | bit   |  |  |  |  |  |

| Lonondi               |                                                                                                |                                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

| Legend:<br>R = Readab | la hit                                                                                         | W = Writable t                                                                  | .it    | II – Unimplor    | nented bit, read |                 |       |  |  |  |  |  |

| -n = Value a          |                                                                                                | '1' = Bit is set                                                                | אנ     | '0' = Bit is cle |                  | x = Bit is unkr |       |  |  |  |  |  |

|                       | IL FOR                                                                                         | I – DILIS SEL                                                                   |        |                  | areu             |                 |       |  |  |  |  |  |

| bit 15-8              | Unimplemen                                                                                     | ted: Read as '0                                                                 | )'     |                  |                  |                 |       |  |  |  |  |  |

| bit 7                 | -                                                                                              |                                                                                 |        | bit              |                  |                 |       |  |  |  |  |  |

|                       |                                                                                                | IVRIE: Invalid Message Interrupt Enable bit<br>1 = Interrupt request is enabled |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                                                                                                | request is not e                                                                |        |                  |                  |                 |       |  |  |  |  |  |

| bit 6                 | WAKIE: Bus                                                                                     | WAKIE: Bus Wake-up Activity Interrupt Enable bit                                |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                                                                                                | 1 = Interrupt request is enabled                                                |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                                                                                                | request is not e                                                                |        |                  |                  |                 |       |  |  |  |  |  |

| bit 5                 |                                                                                                | Interrupt Enabl                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

|                       | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |                                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

| L:1 4                 |                                                                                                | •                                                                               |        |                  |                  |                 |       |  |  |  |  |  |

| bit 4                 | -                                                                                              | ted: Read as '0                                                                 |        | - 64             |                  |                 |       |  |  |  |  |  |

| bit 3                 |                                                                                                | FIFOIE: FIFO Almost Full Interrupt Enable bit                                   |        |                  |                  |                 |       |  |  |  |  |  |

|                       | 1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                       |                                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

| bit 2                 | <b>RBOVIE:</b> RX Buffer Overflow Interrupt Enable bit                                         |                                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                                                                                                | 1 = Interrupt request is enabled                                                |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                                                                                                | 0 = Interrupt request is not enabled                                            |        |                  |                  |                 |       |  |  |  |  |  |

| bit 1                 | RBIE: RX Buffer Interrupt Enable bit                                                           |                                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

|                       | 1 = Interrupt request is enabled                                                               |                                                                                 |        |                  |                  |                 |       |  |  |  |  |  |

|                       | •                                                                                              | request is not e                                                                |        |                  |                  |                 |       |  |  |  |  |  |

| bit 0                 |                                                                                                | fer Interrupt En                                                                |        |                  |                  |                 |       |  |  |  |  |  |

|                       |                                                                                                | request is enabl                                                                |        |                  |                  |                 |       |  |  |  |  |  |

|                       | 0 = Interrupt i                                                                                | request is not e                                                                | napled |                  |                  |                 |       |  |  |  |  |  |

### REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

### 22.2 CTMU Control Registers

| REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1                                                                                                                    |            |                                             |         |                   |                  |                        |                |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------|---------|-------------------|------------------|------------------------|----------------|--|--|

| R/W-0                                                                                                                                                               | U-0        | R/W-0                                       | R/W-0   | R/W-0             | R/W-0            | R/W-0                  | R/W-0          |  |  |

| CTMUEN                                                                                                                                                              | _          | CTMUSIDL                                    | TGEN    | EDGEN             | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG         |  |  |

| bit 15                                                                                                                                                              |            |                                             |         |                   |                  | bit 8                  |                |  |  |

|                                                                                                                                                                     |            |                                             |         |                   |                  |                        |                |  |  |

| U-0                                                                                                                                                                 | U-0        | U-0                                         | U-0     | U-0               | U-0              | U-0                    | U-0            |  |  |

| _                                                                                                                                                                   |            | —                                           | _       |                   | <u> </u>         |                        | _              |  |  |

| bit 7 bit 0                                                                                                                                                         |            |                                             |         |                   |                  |                        |                |  |  |

|                                                                                                                                                                     |            |                                             |         |                   |                  |                        |                |  |  |

| Legend:                                                                                                                                                             |            |                                             |         |                   |                  |                        |                |  |  |

| R = Readable                                                                                                                                                        | e bit      | W = Writable b                              | oit     | U = Unimplen      | nented bit, read | l as '0'               |                |  |  |

| -n = Value at                                                                                                                                                       | POR        | '1' = Bit is set                            |         | '0' = Bit is clea | ared             | x = Bit is unkn        | Bit is unknown |  |  |

| bit 15                                                                                                                                                              | 1 = Module | TMU Enable bit<br>is enabled<br>is disabled |         |                   |                  |                        |                |  |  |

| bit 14                                                                                                                                                              | Unimpleme  | nted: Read as '0                            | 3       |                   |                  |                        |                |  |  |

| bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |            |                                             |         |                   |                  |                        |                |  |  |

| bit 12                                                                                                                                                              | TGEN: Time | Generation Ena                              | ble bit |                   |                  |                        |                |  |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

### 25.3 Op Amp/Comparator Registers

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0             | U-0            | R-0                     | R-0                  | R-0                  | R-0                  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------------|----------------------|----------------------|----------------------|--|--|--|--|

| PSIDL         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _               | _              | C4EVT <sup>(1)</sup>    | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT <sup>(1)</sup> |  |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | •              |                         |                      |                      | bit                  |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                |                         |                      |                      |                      |  |  |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0             | U-0            | R-0                     | R-0                  | R-0                  | R-0                  |  |  |  |  |

| _             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _               | _              | C4OUT <sup>(2)</sup>    | C3OUT <sup>(2)</sup> | C2OUT <sup>(2)</sup> | C10UT <sup>(2)</sup> |  |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                |                         |                      |                      | bit                  |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                |                         |                      |                      |                      |  |  |  |  |

| Legend:       | - 1-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | L:4            |                         |                      |                      |                      |  |  |  |  |