Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

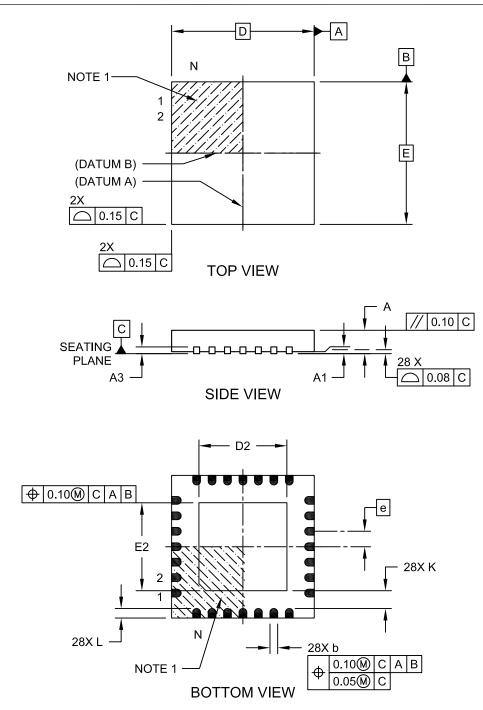

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc202t-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

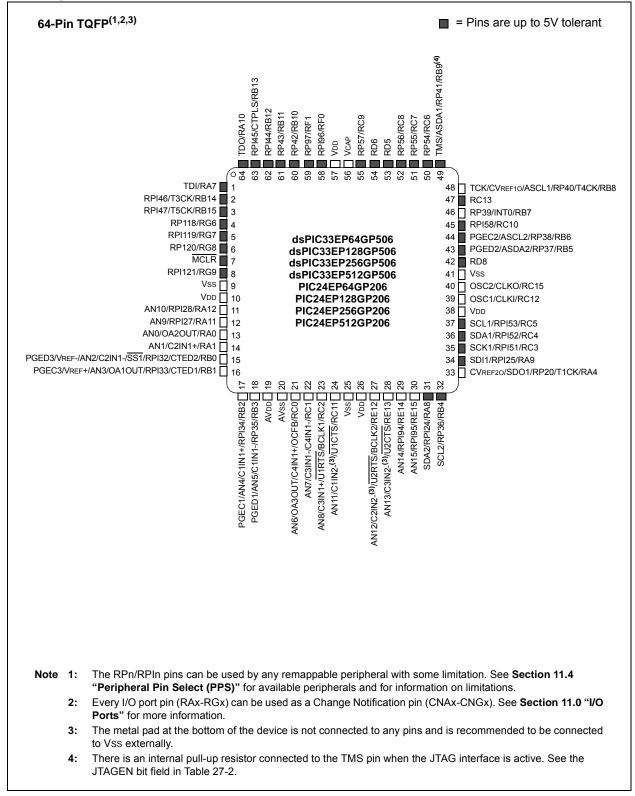

## **Pin Diagrams (Continued)**

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

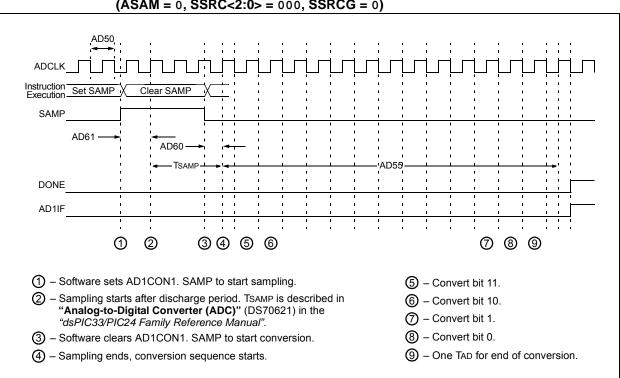

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

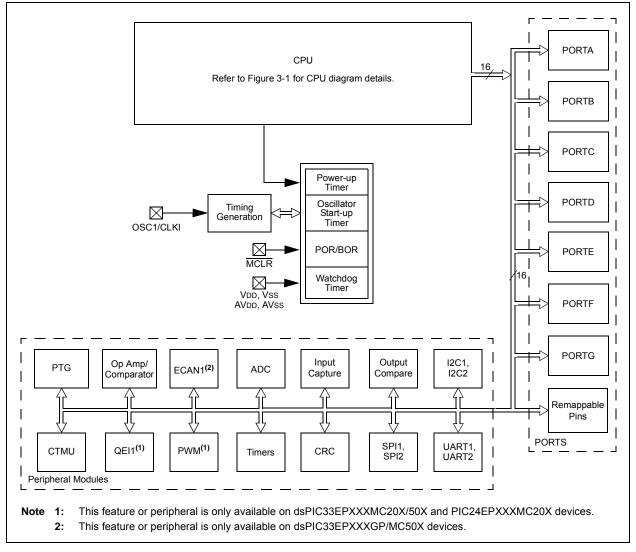

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

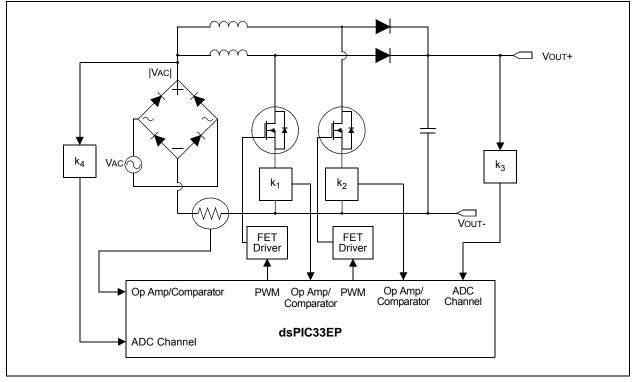

### FIGURE 2-7: INTERLEAVED PFC

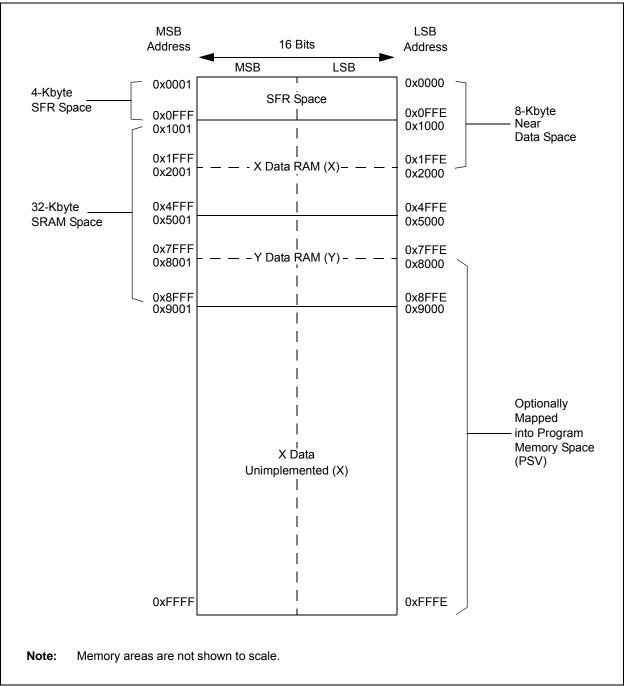

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                                    | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|-------------------------------------------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN                                     | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _                                         | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN                                     | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |                                           |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN                                     | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _                                         | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN                                     | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  | SPI2 Transmit and Receive Buffer Register |        |         |        |        |        |            |              |             | 0000       |        |       |            |       |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |  |  |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |  |  |  |  |  |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |  |  |  |  |  |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |  |  |  |  |  |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |  |  |  |  |  |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |  |  |  |  |  |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |  |  |  |  |  |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |  |  |  |  |  |

## 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

## REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                  |                   | -               |                |

|--------------|-----------|--------------------------------------|-------|------------------|-------------------|-----------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:       | 0>                |                 |                |

| bit 15       |           |                                      |       |                  |                   |                 | bit 8          |

|              |           |                                      |       |                  |                   |                 |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0              | U-0               | U-0             | U-0            |

| —            | —         | —                                    | _     |                  | _                 | —               | —              |

| bit 7        |           |                                      |       |                  |                   |                 | bit C          |

|              |           |                                      |       |                  |                   |                 |                |

| Legend:      |           |                                      |       |                  |                   |                 |                |

| R = Readal   | ole bit   | W = Writable                         | bit   | U = Unimpler     | mented bit, read  | d as '0'        |                |

| -n = Value a | at POR    | '1' = Bit is set                     | :     | '0' = Bit is cle | ared              | x = Bit is unkr | nown           |

|              |           |                                      |       |                  |                   |                 |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                  |                   |                 |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                | on Input 1 to the | e Corresponding | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              |           | Input tied to CM                     | P1    |                  |                   |                 |                |

|              |           | Input tied to Vss                    |       |                  |                   |                 |                |

| bit 7-0      |           | nted: Read as '                      |       |                  |                   |                 |                |

|              |           |                                      | -     |                  |                   |                 |                |

| U-0              | R/W-0                                                                       | R/W-0                              | R/W-0           | R/W-0             | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |

|------------------|-----------------------------------------------------------------------------|------------------------------------|-----------------|-------------------|--------------------------------|----------------------|-----------------|--|--|--|--|

| _                | CLSRC4                                                                      | CLSRC3                             | CLSRC2          | CLSRC1            | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |

| bit 15           |                                                                             |                                    | •               |                   |                                |                      | bit 8           |  |  |  |  |

|                  | <b>D</b> 4 4                                                                | D 0.01 4                           | <b>D</b> 444    |                   | DAMA                           | DAMA                 | DAMO            |  |  |  |  |

| R/W-1            | R/W-1                                                                       | R/W-1                              | R/W-1           | R/W-1             | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                                                     | FLTSRC2                            | FLTSRC1         | FLTSRC0           | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      | DI              |  |  |  |  |

| Legend:          |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

| R = Readable     | bit                                                                         | W = Writable                       | bit             | U = Unimpler      | mented bit, read               | l as '0'             |                 |  |  |  |  |

| -n = Value at I  | POR                                                                         | '1' = Bit is set                   |                 | '0' = Bit is cle  | ared                           | x = Bit is unkr      | nown            |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

| bit 15           | Unimplemen                                                                  | ted: Read as '                     | 0'              |                   |                                |                      |                 |  |  |  |  |

| bit 14-10        | CLSRC<4:0>                                                                  | Current-Limit                      | Control Signa   | al Source Seleo   | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |  |

|                  | 11111 = Fault 32                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 11110 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | •<br>01100 = Reserved                                                       |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 01011 = Comparator 4                                                        |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             | Amp/Comparat                       | or 3            |                   |                                |                      |                 |  |  |  |  |

|                  | •                                                                           | Amp/Comparat                       |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 01000 = Op Amp/Comparator 1                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00111 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00110 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00101 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00100 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00011 <b>= Fault 4</b>                                                      |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00010 = Fault 3                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00001 = Fault 2                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00000 <b>= Fau</b>                                                          | ( <i>)</i>                         |                 |                   | ~                              |                      |                 |  |  |  |  |

| bit 9            | <b>CLPOL:</b> Current-Limit Polarity for PWM Generator # bit <sup>(2)</sup> |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 1 = The selected current-limit source is active-low                         |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 0 = The selec                                                               | cted current-lim                   | it source is ac | tive-high         |                                |                      |                 |  |  |  |  |

| bit 8            | CLMOD: Cur                                                                  | rent-Limit Mode                    | e Enable for P  | WM Generator      | r # bit                        |                      |                 |  |  |  |  |

|                  |                                                                             | imit mode is er<br>imit mode is di |                 |                   |                                |                      |                 |  |  |  |  |

|                  | ne PWMLOCK                                                                  |                                    |                 | <6>) is a '1', th | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |

| the              | unlock sequen                                                               | ce has been ex                     | ecuted.         |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

## REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|------------------|------------------------------------|-------|-------|-------|--|--|

|                                    |       |       | INDXH            | LD<15:8>                           |       |       |       |  |  |

| bit 15                             |       |       |                  |                                    |       |       | bit 8 |  |  |

|                                    |       |       |                  |                                    |       |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |       | INDXF            | ILD<7:0>                           |       |       |       |  |  |

| bit 7                              |       |       |                  |                                    |       |       | bit 0 |  |  |

| Legend:                            |       |       |                  |                                    |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       | it               | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | x = Bit is unkr                    | nown  |       |       |  |  |

## REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

## REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                                     | R/W-0                                                                                         |  |  |

|------------------------------------|-------|----------------------------------|-------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

|                                    |       | QEIIC                            | <31:24>                             |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |

|                                    |       |                                  |                                     |                                                                                       |                                                                                                                                                           | bit 8                                                                                         |  |  |

|                                    |       |                                  |                                     |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |

| R/W-0                              | R/W-0 | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                                     | R/W-0                                                                                         |  |  |

|                                    |       | QEIIC                            | <23:16>                             |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |

|                                    |       |                                  |                                     |                                                                                       |                                                                                                                                                           | bit 0                                                                                         |  |  |

|                                    |       |                                  |                                     |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |

|                                    |       |                                  |                                     |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |

| R = Readable bit W = Writable bit  |       |                                  | U = Unimplemented bit, read as '0'  |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |

| -n = Value at POR '1' = Bit is set |       |                                  | '0' = Bit is cleared x = Bit is u   |                                                                                       |                                                                                                                                                           | nown                                                                                          |  |  |

|                                    | R/W-0 | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplen | QEIIC<31:24>           R/W-0         R/W-0         R/W-0           QEIIC<23:16>           it         W = Writable bit         U = Unimplemented bit, real | QEIIC<31:24>           R/W-0         R/W-0         R/W-0         R/W-0           QEIIC<23:16> |  |  |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0                | R/W-0 | R/W-0            | R/W-0            | R/W-0   | R/W-0                              | R/W-0 | R/W-0 |  |

|----------------------|-------|------------------|------------------|---------|------------------------------------|-------|-------|--|

|                      |       |                  | QEII             | C<15:8> |                                    |       |       |  |

| bit 15               |       |                  |                  |         |                                    |       | bit 8 |  |

| R/W-0                | R/W-0 | R/W-0            | R/W-0            | R/W-0   | R/W-0                              | R/W-0 | R/W-0 |  |

|                      |       |                  | QEI              | C<7:0>  |                                    |       |       |  |

| bit 7                |       |                  |                  |         |                                    |       | bit C |  |

| Legend:              |       |                  |                  |         |                                    |       |       |  |

| R = Readable bit     |       | W = Writable     | W = Writable bit |         | U = Unimplemented bit, read as '0' |       |       |  |

| -n = Value at POR '1 |       | '1' = Bit is set | '1' = Bit is set |         | '0' = Bit is cleared               |       | nown  |  |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

NOTES:

## 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

## REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                                    |       |       | PTGA  | DJ<15:8>                                |       |       |       |  |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |       | PTGA  | DJ<7:0>                                 |       |       |       |  |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       | oit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

## REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGL0<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15      |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0      | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|------------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

| PTGL0<7:0> |             |       |       |       |       |       |       |  |  |  |

| bit 7      | bit 7 bit 0 |       |       |       |       |       |       |  |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN-0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

| REGISTER 25-5: | CMxMSKCON: COMPARATOR x MASK GATING |  |  |  |  |

|----------------|-------------------------------------|--|--|--|--|

|                | CONTROL REGISTER                    |  |  |  |  |

| R/W-0                            |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|--------------------|--------------|--|--|

|                                  | U-0                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                   | R/W-0             | R/W-0              | R/W-0        |  |  |

| HLMS                             | —                                                                                                                                                                                                                                                                                                                         | OCEN                                                                                                                                                                                                                                                                                                          | OCNEN                                                                                                                                                                                                                                                        | OBEN                                    | OBNEN             | OAEN               | OANEN        |  |  |

| bit 15                           |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    | bit          |  |  |

| R/W-0                            | R/W-0                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                   | R/W-0             | R/W-0              | R/W-0        |  |  |

| NAGS                             | PAGS                                                                                                                                                                                                                                                                                                                      | ACEN                                                                                                                                                                                                                                                                                                          | ACNEN                                                                                                                                                                                                                                                        | ABEN                                    | ABNEN             | AAEN               | AANEN        |  |  |

| bit 7                            |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    | bit          |  |  |

| Legend:                          |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

| R = Readable                     | bit                                                                                                                                                                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                                                                                                  | bit                                                                                                                                                                                                                                                          | U = Unimple                             | mented bit, read  | l as '0'           |              |  |  |

| -n = Value at POR                |                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                              | '0' = Bit is cle                        |                   | x = Bit is unknown |              |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

| bit 15                           | HLMS: High                                                                                                                                                                                                                                                                                                                | or Low-Level N                                                                                                                                                                                                                                                                                                | Asking Select                                                                                                                                                                                                                                                | bits                                    |                   |                    |              |  |  |

|                                  | •                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                            |                                         | erted ('0') compa | rator signal from  | n propagatin |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         | erted ('1') compa |                    |              |  |  |

| bit 14                           | Unimplemen                                                                                                                                                                                                                                                                                                                | ted: Read as '                                                                                                                                                                                                                                                                                                | 0'                                                                                                                                                                                                                                                           |                                         |                   |                    |              |  |  |

| bit 13                           | OCEN: OR G                                                                                                                                                                                                                                                                                                                | Sate C Input Er                                                                                                                                                                                                                                                                                               | able bit                                                                                                                                                                                                                                                     |                                         |                   |                    |              |  |  |

|                                  | 1 = MCI is co                                                                                                                                                                                                                                                                                                             | nnected to OR                                                                                                                                                                                                                                                                                                 | gate                                                                                                                                                                                                                                                         |                                         |                   |                    |              |  |  |

|                                  | 0 = MCI is no                                                                                                                                                                                                                                                                                                             | ot connected to                                                                                                                                                                                                                                                                                               | OR gate                                                                                                                                                                                                                                                      |                                         |                   |                    |              |  |  |

| bit 12                           | OCNEN: OR                                                                                                                                                                                                                                                                                                                 | Gate C Input I                                                                                                                                                                                                                                                                                                | nverted Enable                                                                                                                                                                                                                                               | e bit                                   |                   |                    |              |  |  |

|                                  | <ul> <li>1 = Inverted MCI is connected to OR gate</li> <li>0 = Inverted MCI is not connected to OR gate</li> </ul>                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                            | jate                                    |                   |                    |              |  |  |

| bit 11                           | OBEN: OR Gate B Input Enable bit                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

|                                  | 1 = MBI is connected to OR gate<br>0 = MBI is not connected to OR gate                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

| bit 10                           |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                                                                                                                            |                                         |                   |                    |              |  |  |

|                                  | <b>OBNEN:</b> OR Gate B Input Inverted Enable bit<br>1 = Inverted MBI is connected to OR gate                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                              | e dit                                   |                   |                    |              |  |  |

|                                  | 1 = Inverted I                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                             | ed to OR gate                                                                                                                                                                                                                                                |                                         |                   |                    |              |  |  |

| bit 9                            | 1 = Inverted  <br>0 = Inverted                                                                                                                                                                                                                                                                                            | MBI is connect                                                                                                                                                                                                                                                                                                | ed to OR gate<br>nected to OR g                                                                                                                                                                                                                              |                                         |                   |                    |              |  |  |

| bit 9                            | 1 = Inverted I<br>0 = Inverted I<br><b>OAEN:</b> OR G                                                                                                                                                                                                                                                                     | MBI is connect<br>MBI is not conr                                                                                                                                                                                                                                                                             | ed to OR gate<br>nected to OR g<br>able bit                                                                                                                                                                                                                  |                                         |                   |                    |              |  |  |

| bit 9                            | 1 = Inverted I<br>0 = Inverted I<br><b>OAEN:</b> OR G<br>1 = MAI is co                                                                                                                                                                                                                                                    | MBI is connect<br>MBI is not conr<br>Gate A Input En                                                                                                                                                                                                                                                          | ed to OR gate<br>nected to OR g<br>able bit<br>gate                                                                                                                                                                                                          |                                         |                   |                    |              |  |  |

| bit 9<br>bit 8                   | 1 = Inverted I<br>0 = Inverted I<br><b>OAEN:</b> OR G<br>1 = MAI is co<br>0 = MAI is no                                                                                                                                                                                                                                   | MBI is connect<br>MBI is not conr<br>Gate A Input En<br>nnected to OR                                                                                                                                                                                                                                         | ed to OR gate<br>nected to OR g<br>hable bit<br>gate<br>OR gate                                                                                                                                                                                              | jate                                    |                   |                    |              |  |  |

|                                  | 1 = Inverted I<br>0 = Inverted I<br><b>OAEN:</b> OR G<br>1 = MAI is co<br>0 = MAI is no<br><b>OANEN:</b> OR<br>1 = Inverted I                                                                                                                                                                                             | MBI is connect<br>MBI is not conr<br>Gate A Input En<br>Innected to OR<br>of connected to<br>Gate A Input I<br>MAI is connect                                                                                                                                                                                 | ed to OR gate<br>nected to OR g<br>able bit<br>gate<br>OR gate<br>nverted Enable<br>ed to OR gate                                                                                                                                                            | jate<br>e bit                           |                   |                    |              |  |  |