Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

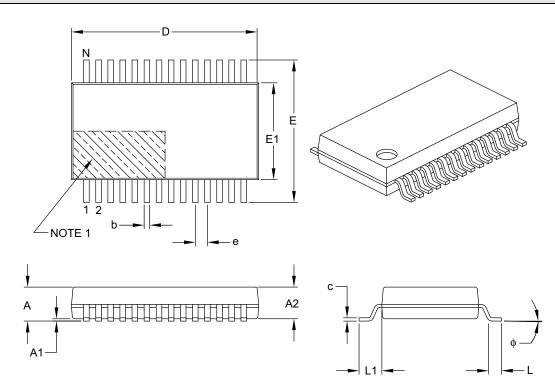

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc204-e-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

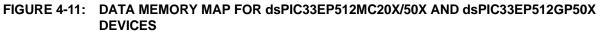

### 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

### TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address       |           |                     |                     |     |  |

|------------------------|---------------|-----------------------------|-----------|---------------------|---------------------|-----|--|

| Access Type            | Space         | <23>                        | <22:16>   | <15>                | <14:1>              | <0> |  |

| Instruction Access     | User          | 0                           |           | PC<22:1>            |                     | 0   |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xxx |           |                     |                     |     |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0> Data EA<15:0    |           |                     |                     |     |  |

| (Byte/Word Read/Write) |               | 0                           | 0xxx xxxx |                     | XXXX XXXX XXXX XXXX |     |  |

|                        | Configuration | TBLPAG<7:0>                 |           | Data EA<15:0>       |                     |     |  |

|                        |               | 1                           | xxx xxxx  | XXXX XXXX XXXX XXXX |                     |     |  |

### FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                | U-0                                                                          | U-0              | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |

|----------------------|------------------------------------------------------------------------------|------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| FORCE <sup>(1)</sup> |                                                                              | _                | _                     | —                |                  | _               |         |  |  |  |  |

| bit 15               |                                                                              |                  |                       |                  |                  |                 | bit 8   |  |  |  |  |

|                      |                                                                              |                  |                       |                  |                  |                 |         |  |  |  |  |

| R/W-0                | R/W-0                                                                        | R/W-0            | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

| IRQSEL7              | IRQSEL6                                                                      | IRQSEL5          | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |

| bit 7                |                                                                              |                  |                       |                  |                  |                 | bit     |  |  |  |  |

| Legend:              |                                                                              | S = Settable b   | oit                   |                  |                  |                 |         |  |  |  |  |

| R = Readable         | bit                                                                          | W = Writable     | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at F      | POR                                                                          | '1' = Bit is set |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |

|                      |                                                                              |                  |                       |                  |                  |                 |         |  |  |  |  |

| bit 15               | FORCE: Force                                                                 | e DMA Transfe    | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |

|                      | 1 = Forces a single DMA transfer (Manual mode)                               |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 0 = Automatic DMA transfer initiation by DMA request                         |                  |                       |                  |                  |                 |         |  |  |  |  |

| bit 14-8             | Unimplemen                                                                   | ted: Read as 'd  | )'                    |                  |                  |                 |         |  |  |  |  |

| bit 7-0              | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                           |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>                            |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100110 = IC4 – Input Capture 4                                             |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100101 = IC3 - Input Capture 3                                             |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100010 = ECAN1 - RX Data Ready(2)                                          |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00100001 = SPI2 Transfer Done<br>00011111 = UART2TX – UART2 Transmitter      |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011111 = UART2TX - UART2 Transmitter $00011110 = UART2RX - UART2 Receiver$ |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011100 = TMR5 - Timer5                                                     |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011011 = TMR4 – Timer4                                                     |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011010 = OC4 – Output Compare 4                                            |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00011001 = OC3 – Output Compare 3                                            |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001101 = ADC1 – ADC1 Convert done                                          |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001100 = UART1TX – UART1 Transmitter                                       |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver                                          |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001010 = SPI1 – Transfer Done<br>00001000 = TMR3 – Timer3                  |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00001000 = TMRS - TimerS<br>00000111 = TMR2 - Timer2                         |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00000111 - 10002 - 100012<br>00000110 = OC2 - Output Compare 2               |                  |                       |                  |                  |                 |         |  |  |  |  |

|                      |                                                                              | IC2 – Input Ca   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 0000010 =                                                                    | OC1 – Output (   | Compare 1             |                  |                  |                 |         |  |  |  |  |

|                      |                                                                              | IC1 – Input Ca   |                       |                  |                  |                 |         |  |  |  |  |

|                      | 00000000 =                                                                   | INT0 – Externa   | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00                                                                                                                        |                                                           |              |                   |                  |                 |        |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| U-0             | U-0                                                                                                                                | U-0                                                       | U-0          | U-0               | U-0              | U-0             | U-0    |  |  |  |  |

| —               | —                                                                                                                                  | —                                                         | —            | —                 | —                | —               | —      |  |  |  |  |

| bit 15          |                                                                                                                                    |                                                           |              |                   |                  |                 | bit 8  |  |  |  |  |

|                 |                                                                                                                                    |                                                           |              |                   |                  |                 |        |  |  |  |  |

| U-0             | U-0                                                                                                                                | U-0                                                       | U-0          | R-0               | R-0              | R-0             | R-0    |  |  |  |  |

| —               |                                                                                                                                    | —                                                         | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |  |  |  |  |

| bit 7           |                                                                                                                                    |                                                           |              |                   |                  |                 | bit 0  |  |  |  |  |

|                 |                                                                                                                                    |                                                           |              |                   |                  |                 |        |  |  |  |  |

| Legend:         |                                                                                                                                    |                                                           |              |                   |                  |                 |        |  |  |  |  |

| R = Readable    | bit                                                                                                                                | W = Writable                                              | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value at F | POR                                                                                                                                | '1' = Bit is set                                          |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |  |  |  |  |

|                 |                                                                                                                                    |                                                           |              |                   |                  |                 |        |  |  |  |  |

| bit 15-4        | Unimplemen                                                                                                                         | ted: Read as '                                            | כ'           |                   |                  |                 |        |  |  |  |  |

| bit 3           | RQCOL3: DN                                                                                                                         | RQCOL3: DMA Channel 3 Transfer Request Collision Flag bit |              |                   |                  |                 |        |  |  |  |  |

|                 | <ul> <li>1 = User force and interrupt-based request collision is detected</li> <li>0 = No request collision is detected</li> </ul> |                                                           |              |                   |                  |                 |        |  |  |  |  |

| <b>h</b> # 0    | •                                                                                                                                  |                                                           |              | est Callisian Fl  | aa hit           |                 |        |  |  |  |  |

| bit 2           |                                                                                                                                    | /IA Channel 2 T<br>ce and interrupt                       | •            |                   | 0                |                 |        |  |  |  |  |

|                 |                                                                                                                                    | e and interrupt<br>est collision is d                     |              |                   | elecieu          |                 |        |  |  |  |  |

| bit 1           | RQCOL1: DN                                                                                                                         | /IA Channel 1 T                                           | ransfer Requ | est Collision F   | ag bit           |                 |        |  |  |  |  |

|                 | 1 = User force and interrupt-based request collision is detected                                                                   |                                                           |              |                   |                  |                 |        |  |  |  |  |

|                 | 0 = No reque                                                                                                                       | est collision is d                                        | etected      |                   |                  |                 |        |  |  |  |  |

| bit 0           | RQCOLO: DN                                                                                                                         | /IA Channel 0 T                                           | ransfer Requ | est Collision F   | lag bit          |                 |        |  |  |  |  |

|                 | 1 = User force                                                                                                                     | e and interrupt                                           | -based reque | st collision is d | etected          |                 |        |  |  |  |  |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

| U-0       R/W-0       R/W       R/W       R/W </th <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>U-0</th> <th>U-0</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0         | R/W-0                                 | R/W-0                                                                                                                                      | R/W-0                            | R/W-0                   | R/W-0            | U-0               | U-0           |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------|------------------|-------------------|---------------|--|--|--|

| U-0       U-0       RW-0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PHR           | PHF                                   | PLR                                                                                                                                        | PLF                              | FLTLEBEN                | CLLEBEN          | —                 |               |  |  |  |

| -         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPH         BPHL         BPLH         BPHH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 15        |                                       |                                                                                                                                            |                                  |                         |                  |                   | bit           |  |  |  |

| bit 7       t         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking is applied to selected Fault input       1 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0           | U-0                                   | R/W-0                                                                                                                                      | R/W-0                            | R/W-0                   | R/W-0            | R/W-0             | R/W-0         |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>nn = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 PHR: PWMxH Rising Edge Trigger Enable bit<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxH<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Rising edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Leading-Edge Blanking is applied to selected Fault input<br>0 = Leading-Edge Blanking is applied to selected Fault input<br>1 = Leading-Edge Blanking is applied to selected Current-limit input<br>1 = Leading-Edge Blanking is not applied to selected current-limit input<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low<br>0 = No blanking when selected blanking signal Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when Selected blanking signal is low<br>0 = No blanking when PWMxH dupt is high<br>0 = No blanking when PWMxH dupt signals) when PWMxH output is high<br>0 = No blanking when PWMxH tow Enable bit<br>1 = State blanking (of current-limit and/ | _             | _                                     | BCH <sup>(1)</sup>                                                                                                                         | BCL <sup>(1)</sup>               | BPHH                    | BPHL             | BPLH              | BPLL          |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PWMxH         bit 13       PLR: PWMxL Rising Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxL         bit 13       PLR: PWMxL Falling Edge Trigger Enable bit       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking is not applied to selected Fault input         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking is not applied to selected current-limit input         bit 9-6       Unimplemented: Read as '0'       1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking signal is high       1 = State blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7         |                                       |                                                                                                                                            |                                  |                         |                  |                   | bit           |  |  |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxH       11 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxH       11 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores fising edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input       0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking signal Figh Enable bit         1 = State blanking in Selected Blanking Singal High Enable bit <sup>(1)</sup> 1 = State blanking in Sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:       |                                       |                                                                                                                                            |                                  |                         |                  |                   |               |  |  |  |

| <ul> <li>PHR: PWMxH Rising Edge Trigger Enable bit         <ol> <li>Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R = Readabl   | e bit                                 | W = Writable                                                                                                                               | bit                              | U = Unimpler            | mented bit, read | as '0'            |               |  |  |  |

| <ul> <li>1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxH</li> <li>PHF: PWMxH Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>PLR: PVMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>Det Leading-Edge Blanking ignores ralling edge of PWMxL</li> <li>D = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit</li> <li>1 = Leading-Edge Blanking Signal Liph Enable bit<sup>(1)</sup></li> <li>1 = State blanking (or current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No b</li></ul>                                                                                                                                                                | -n = Value at | POR                                   | '1' = Bit is set                                                                                                                           | :                                | '0' = Bit is cle        | ared             | x = Bit is unkr   | nown          |  |  |  |

| <ul> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>bit 13 PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 12 FLTLEBEN: Fault Input Leading-Edge Blanking Counter</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is nigh</li> <li>0 = No bla</li></ul>                                                                                                                                                                 | bit 15        | 1 = Rising ed                         | ge of PWMxH                                                                                                                                | will trigger Le                  | ading-Edge Bla          |                  |                   |               |  |  |  |

| <ul> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>pLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11</li> <li>FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking when selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH dutput is high</li> <li>0 = No blanking when PWMxH Low Enable bit</li> <li>1 = State blanking (of</li></ul>                                                                                                                                                         | bit 14        | 1 = Falling ed                        | lge of PWMxH                                                                                                                               | will trigger Le                  | eading-Edge Bla         | 0                |                   |               |  |  |  |

| bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit         1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = No blanking when selected Blanking signal Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         0 = No blanking when P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 13        | 1 = Rising ed                         | ge of PWMxL                                                                                                                                | will trigger Le                  | ading-Edge Bla          |                  |                   |               |  |  |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking in PWMxL Low Enable bit</li></ul>                                                                                                                                                                 | bit 12        | 1 = Falling ed                        | lge of PWMxL                                                                                                                               | will trigger Le                  | ading-Edge Bla          |                  |                   |               |  |  |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>bit 9-6</li> <li>Unimplemented: Read as '0'</li> <li>bit 5</li> <li>BCH: Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>bit 4</li> <li>BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL Ligh Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL output is high</li> </ul>                                                                                                                                                                                                 | bit 11        | 1 = Leading-E                         | Edge Blanking                                                                                                                              | is applied to                    | selected Fault in       | nput             |                   |               |  |  |  |

| bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         0 = No blanking when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       State blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxL output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 10        | 1 = Leading-E                         | Edge Blanking                                                                                                                              | is applied to                    | selected current        | t-limit input    |                   |               |  |  |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 9-6       | Unimplemen                            | ted: Read as '                                                                                                                             | 0'                               |                         |                  |                   |               |  |  |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>BPHH: Blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 5         | 1 = State blar                        | nking (of currer                                                                                                                           | nt-limit and/or                  | Fault input sigr        |                  | cted blanking s   | ignal is high |  |  |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 4         | 1 = State blar                        | nking (of currer                                                                                                                           | nt-limit and/or                  | Fault input sigr        |                  | cted blanking s   | ignal is low  |  |  |  |

| 1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 3         | 1 = State blar                        | nking (of currer                                                                                                                           | nt-limit and/or                  | Fault input sigr        | nals) when PWN   | /IxH output is h  | igh           |  |  |  |

| bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 2         | 1 = State blar                        | <b>BPHL:</b> Blanking in PWMxH Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low |                                  |                         |                  |                   |               |  |  |  |

| bit 0 <b>BPLL:</b> Blanking in PWMxL Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 1         | <b>BPLH:</b> Blanki<br>1 = State blar | ing in PWMxL<br>hking (of currer                                                                                                           | High Enable I<br>nt-limit and/or | bit<br>Fault input sigr | nals) when PWN   | /IxL output is hi | gh            |  |  |  |

| $\sim$ i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 0         | <b>BPLL:</b> Blanki<br>1 = State blar | ng in PWMxL I<br>hking (of currer                                                                                                          | Low Enable b<br>nt-limit and/or  | it<br>Fault input sigr  | nals) when PWN   | /IxL output is lo | w             |  |  |  |

### REGISTER 16-16: LEBCONX: PWMx LEADING-EDGE BLANKING CONTROL REGISTER

Note 1: The blanking signal is selected via the BLANKSELx bits in the AUXCONx register.

### 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register