Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc204-h-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   |                                | (se                           |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

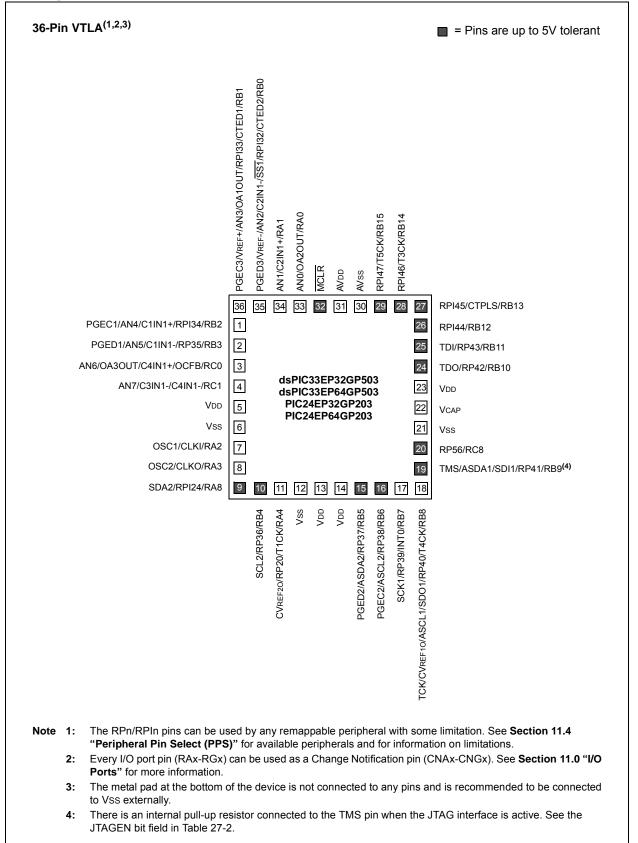

## **Pin Diagrams (Continued)**

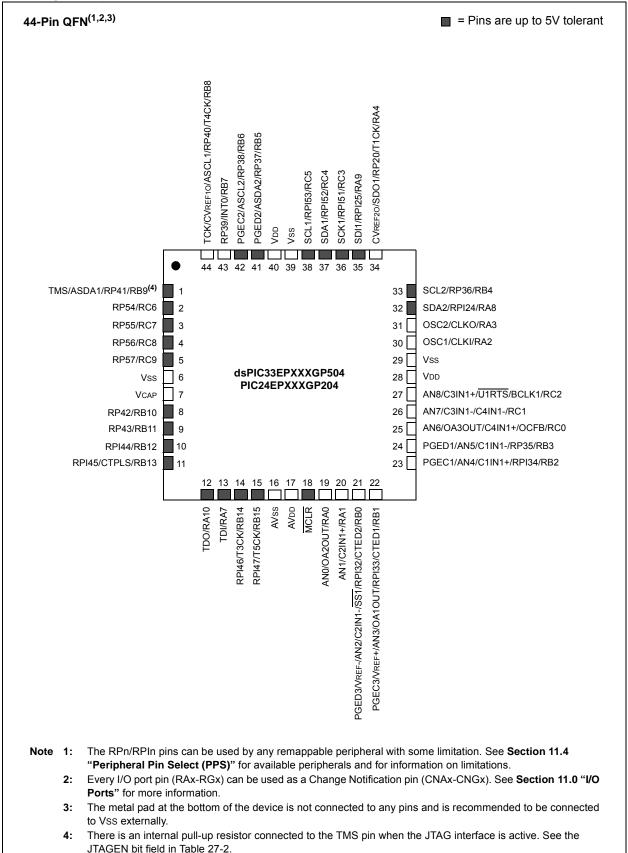

## **Pin Diagrams (Continued)**

## **Table of Contents**

| 1.0   | Device Overview                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             |     |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           |     |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

|       | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     |     |

|       | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) |     |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                                                 |     |

|       | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    |     |

|       | Charge Time Measurement Unit (CTMU)                                                                |     |

|       | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    |     |

|       | Peripheral Trigger Generator (PTG) Module                                                          |     |

| 25.0  | Op Amp/Comparator Module                                                                           |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                                               |     |

| 27.0  |                                                                                                    |     |

|       |                                                                                                    |     |

| 29.0  | Development Support                                                                                |     |

|       | Electrical Characteristics                                                                         |     |

|       | High-Temperature Electrical Characteristics                                                        |     |

|       | DC and AC Device Characteristics Graphs                                                            |     |

|       | Packaging Information                                                                              |     |

|       | ndix A: Revision History                                                                           |     |

|       | (                                                                                                  |     |

|       | Vicrochip Web Site                                                                                 |     |

|       | omer Change Notification Service                                                                   |     |

|       | omer Support                                                                                       |     |

| Produ | uct Identification System                                                                          | 527 |

## 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

## 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | SFA: Stack Frame Active Status bit                                                        |

|-------|-------------------------------------------------------------------------------------------|

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and |

|       | DSWPAG values                                                                             |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space              |

| hit 1 | PND: Dounding Mode Select hit(1)                                                          |

- bit 1 **RND:** Rounding Mode Select bit<sup>(1)</sup>

- 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

bit 0 IF: Integer or Fractional Multiplier Mode Select bit<sup>(1)</sup> 1 = Integer mode is enabled for DSP multiply 0 = Fractional mode is enabled for DSP multiply

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

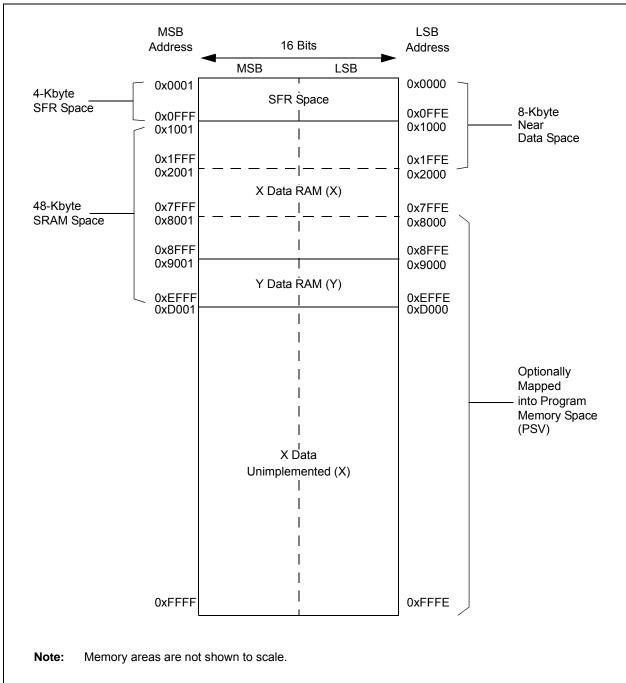

## 4.2 Data Address Space

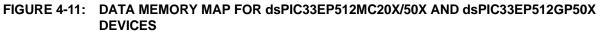

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

## 13.2 Timer Control Registers

| R/W-0         | U-0                                   | R/W-0                              | U-0            | U-0              | U-0             | U-0             | U-0   |

|---------------|---------------------------------------|------------------------------------|----------------|------------------|-----------------|-----------------|-------|

| TON           |                                       | TSIDL                              | —              | _                |                 |                 | _     |

| bit 15        |                                       |                                    |                |                  |                 |                 | bit 8 |

|               |                                       |                                    |                |                  |                 |                 |       |

| U-0           | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |

| _             | TGATE                                 | TCKPS1                             | TCKPS0         | T32              | _               | TCS             | _     |

| bit 7         |                                       |                                    |                |                  |                 |                 | bit ( |

| <u> </u>      |                                       |                                    |                |                  |                 |                 |       |

| Legend:       | - 1-:4                                |                                    |                | II II.           |                 |                 |       |

| R = Readable  |                                       | W = Writable                       |                | -                | nented bit, rea |                 |       |

| -n = Value at | PUR                                   | '1' = Bit is set                   |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |

| bit 15        | TON: Timerx                           | On hit                             |                |                  |                 |                 |       |

|               | When T32 = 2                          |                                    |                |                  |                 |                 |       |

|               | 1 = Starts 32-                        | bit Timerx/y                       |                |                  |                 |                 |       |

|               | 0 = Stops 32-                         |                                    |                |                  |                 |                 |       |

|               | <u>When T32 = 0</u><br>1 = Starts 16- |                                    |                |                  |                 |                 |       |

|               | 0 = Stops 16-                         |                                    |                |                  |                 |                 |       |

| bit 14        | Unimplemen                            | ted: Read as '                     | )'             |                  |                 |                 |       |

| bit 13        | TSIDL: Timer                          | x Stop in Idle M                   | lode bit       |                  |                 |                 |       |

|               |                                       | ues module op                      |                |                  | dle mode        |                 |       |

|               |                                       | s module opera                     |                | ode              |                 |                 |       |

| bit 12-7      | -                                     | ted: Read as '                     |                |                  |                 |                 |       |

| bit 6         |                                       | erx Gated Time                     | Accumulation   | Enable bit       |                 |                 |       |

|               | When TCS =<br>This bit is igno        |                                    |                |                  |                 |                 |       |

|               | When TCS =                            |                                    |                |                  |                 |                 |       |

|               | 1 = Gated tim                         | e accumulatior                     |                |                  |                 |                 |       |

|               |                                       | e accumulation                     |                |                  |                 |                 |       |

| bit 5-4       |                                       | : Timerx Input                     | Clock Prescal  | e Select bits    |                 |                 |       |

|               | 11 = 1:256<br>10 = 1:64               |                                    |                |                  |                 |                 |       |

|               | 01 = 1:8                              |                                    |                |                  |                 |                 |       |

|               | 00 = 1:1                              |                                    |                |                  |                 |                 |       |

| bit 3         | T32: 32-Bit Ti                        | mer Mode Sele                      | ect bit        |                  |                 |                 |       |

|               |                                       | nd Timery form<br>nd Timery act as |                |                  |                 |                 |       |

| bit 2         | Unimplemen                            | ted: Read as '                     | )'             |                  |                 |                 |       |

| bit 1         | TCS: Timerx                           | Clock Source S                     | elect bit      |                  |                 |                 |       |

|               | 1 = External c<br>0 = Internal cl     | clock is from pir<br>lock (FP)     | n, TxCK (on th | ne rising edge)  |                 |                 |       |

| bit 0         | Unimplomon                            | ted: Read as '                     | ı'             |                  |                 |                 |       |

## REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |

|------------|---------------------------------------|------------------------------------|----------------|------------------|------------------------------|-----------------|--------|

| ADCTS4     | ADCTS3                                | ADCTS2                             | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |

| bit 15     |                                       |                                    |                |                  |                              |                 | bit 8  |

| R/W-0      | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |

| OC4CS      |                                       | OC2CS                              | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |

| bit 7      |                                       | 00100                              |                |                  |                              |                 | bit (  |

| Legend:    |                                       |                                    |                |                  |                              |                 |        |

| R = Reada  | ble bit                               | W = Writable                       | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |

| -n = Value | at POR                                | '1' = Bit is set                   |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |

|            |                                       |                                    |                |                  |                              |                 |        |

| bit 15     | ADCTS4: Sa                            | mple Trigger P                     | TGO15 for AE   | OC bit           |                              |                 |        |

|            | 1 = Generate                          | es Trigger wher                    | the broadcas   | t command is     | executed                     |                 |        |

|            | 0 = Does not                          | generate Trigg                     | er when the b  | roadcast com     | mand is execute              | ed              |        |

| bit 14     |                                       | mple Trigger P                     |                |                  |                              |                 |        |

|            |                                       | es Trigger wher                    |                |                  |                              | al              |        |

| bit 13     |                                       |                                    |                |                  | mand is execute              | a               |        |

| DIE 13     |                                       | mple Trigger P<br>es Trigger wher  |                |                  | evecuted                     |                 |        |

|            |                                       |                                    |                |                  | mand is execute              | ed              |        |

| bit 12     |                                       | mple Trigger P                     |                |                  |                              |                 |        |

|            | 1 = Generate                          | es Trigger wher                    | the broadcas   | t command is     | executed                     |                 |        |

|            |                                       |                                    |                |                  | mand is execute              | ed              |        |

| bit 11     | -                                     | ger/Synchroniz                     |                |                  |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 10     | IC3TSS: Trig                          | ger/Synchroniz                     | ation Source f | for IC3 bit      |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 9      | IC2TSS: Trig                          | ger/Synchroniz                     | ation Source f | for IC2 bit      |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 8      |                                       | ger/Synchroniz                     |                |                  |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 7      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            |                                       | es clock pulse v<br>generate clock |                |                  | d is executed command is exe | cuted           |        |

| bit 6      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            |                                       | es clock pulse v<br>aenerate clock |                |                  | d is executed command is exe | cuted           |        |

| bit 5      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            | 1 = Generate                          | es clock pulse v                   | when the broad |                  | d is executed command is exe | cuted           |        |

|            | This register is rea<br>PTGSTRT = 1). | -                                  |                |                  |                              |                 | and    |

|            | This register is on                   | lv used with the                   | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |

|            |                                       | .,                                 |                |                  | c.op commune                 | •               |        |

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN-0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | R/W-0                        | U-0              | U-0                                    | U-0              | R/W-0                        | U-0              | U-0            |

|-----------------|------------------------------|------------------|----------------------------------------|------------------|------------------------------|------------------|----------------|

|                 | CVR2OE <sup>(1)</sup>        | _                | _                                      | _                | VREFSEL                      | _                | _              |

| bit 15          |                              |                  |                                        |                  |                              |                  | bit            |

| <b>D</b> 444 0  | DAALO                        | DAALO            |                                        | <b>D</b> 444 0   | DAALO                        | DANA             | <b>D</b> 444 0 |

| R/W-0           | R/W-0                        | R/W-0            | R/W-0                                  | R/W-0            | R/W-0                        | R/W-0            | R/W-0          |

| CVREN           | CVR10E <sup>(1)</sup>        | CVRR             | CVRSS <sup>(2)</sup>                   | CVR3             | CVR2                         | CVR1             | CVR0           |

| bit 7           |                              |                  |                                        |                  |                              |                  | bit            |

| Legend:         |                              |                  |                                        |                  |                              |                  |                |

| R = Readable    | bit                          | W = Writable     | bit                                    | U = Unimple      | mented bit, read             | as '0'           |                |

| -n = Value at F | POR                          | '1' = Bit is set | t                                      | '0' = Bit is cle | eared                        | x = Bit is unkn  | iown           |

|                 |                              |                  |                                        |                  |                              |                  |                |

| bit 15          | Unimplement                  |                  |                                        |                  |                              |                  |                |

| bit 14          |                              | •                | ige Reference                          | •                | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | nected to the C<br>onnected from       |                  | nin                          |                  |                |

| bit 13-11       | Unimplement                  |                  |                                        |                  | <b>F</b>                     |                  |                |

| bit 10          | -                            |                  | age Reference                          | e Select bit     |                              |                  |                |

|                 | 1 = CVREFIN =                | -                | C                                      |                  |                              |                  |                |

|                 | 0 = CVREFIN is               | s generated by   | y the resistor ne                      | etwork           |                              |                  |                |

| bit 9-8         | Unimplement                  | ted: Read as '   | 0'                                     |                  |                              |                  |                |

| bit 7           |                              |                  | e Reference E                          |                  |                              |                  |                |

|                 |                              |                  | erence circuit is<br>erence circuit is |                  | wn                           |                  |                |

| bit 6           | CVR1OE: Co                   | mparator Volta   | ige Reference                          | 1 Output Ena     | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | n the CVREF1C                          |                  | n                            |                  |                |

| bit 5           | CVRR: Comp                   | arator Voltage   | Reference Ra                           | nge Selection    | n bit                        |                  |                |

|                 | 1 = CVRSRC/2<br>0 = CVRSRC/3 |                  |                                        |                  |                              |                  |                |

| bit 4           | CVRSS: Com                   | parator Voltag   | e Reference S                          | ource Selecti    | on bit <sup>(2)</sup>        |                  |                |

|                 |                              | 0                | erence source,<br>erence source,       | · ·              | ref+) – (AVss)<br>/dd – AVss |                  |                |

| bit 3-0         | CVR<3:0> Co                  | mparator Volt    | age Reference                          | Value Select     | ion $0 \leq CVR < 3$ :       | $0> \le 15$ bits |                |

|                 | When CVRR = CVREFIN = (CV    |                  | (CVRSRC)                               |                  |                              |                  |                |

|                 | When CVRR = CVREFIN = (CV    | = 0:             |                                        | $(\mathbf{C})$   |                              |                  |                |

## REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 27-1: DEVID: DEVICE ID REGISTER

|        | R = Read-Only bit |   |         | U = Unimplem          |   |   |        |

|--------|-------------------|---|---------|-----------------------|---|---|--------|

|        |                   |   |         |                       |   |   |        |

| bit 7  |                   |   |         |                       |   |   | bit 0  |

|        |                   |   | DEVID   | <7:0> <sup>(1)</sup>  |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

| bit 15 |                   |   |         |                       |   |   | bit 8  |

|        |                   |   | DEVID<  | :15:8> <sup>(1)</sup> |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

| bit 23 |                   |   |         |                       |   |   | bit 16 |

|        |                   |   | DEVID<2 | 23:16>(1)             |   |   |        |

| R      | R                 | R | R       | R                     | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

## **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R             | R | R      | R                      | R          | R | R      |

|-------------|---------------|---|--------|------------------------|------------|---|--------|

|             |               |   | DEVREV | <23:16> <sup>(1)</sup> |            |   |        |

| bit 23      |               |   |        |                        |            |   | bit 16 |

|             |               |   |        |                        |            |   |        |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVREV | <15:8>(1)              |            |   |        |

| bit 15      |               |   |        |                        |            |   | bit 8  |

| R           | R             | R | R      | R                      | R          | R | R      |

|             |               |   | DEVRE\ | /<7:0>(1)              |            |   |        |

| bit 7       |               |   |        |                        |            |   | bit 0  |

|             |               |   |        |                        |            |   |        |

| Legend: R = | Read-only bit |   |        | U = Unimplem           | nented bit |   |        |

## bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values. Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| #text               | Means literal defined by "text"                                                      |  |  |  |  |  |

| (text)              | Means "content of text"                                                              |  |  |  |  |  |

| [text]              | Means "the location addressed by text"                                               |  |  |  |  |  |

| {}                  | Optional field or operation                                                          |  |  |  |  |  |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |  |  |  |  |  |

| <n:m></n:m>         | Register bit field                                                                   |  |  |  |  |  |

| .b                  | Byte mode selection                                                                  |  |  |  |  |  |

| .d                  | Double-Word mode selection                                                           |  |  |  |  |  |

| .S                  | Shadow register select                                                               |  |  |  |  |  |

| .w                  | Word mode selection (default)                                                        |  |  |  |  |  |

| Acc                 | One of two accumulators {A, B}                                                       |  |  |  |  |  |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |  |  |  |  |  |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |  |  |  |  |  |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |  |  |  |  |  |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |  |  |  |  |  |

| f                   | File register address ∈ {0x00000x1FFF}                                               |  |  |  |  |  |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |  |  |  |  |  |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |  |  |  |  |  |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |  |  |  |  |  |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |  |  |  |  |  |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |  |  |  |  |  |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |  |  |  |  |  |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |  |  |  |  |  |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |  |  |  |  |  |

| None                | Field does not require an entry, can be blank                                        |  |  |  |  |  |

| OA, OB, SA, SB      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |  |  |  |  |  |

| PC                  | Program Counter                                                                      |  |  |  |  |  |

| Slit10              | 10-bit signed literal ∈ {-512511}                                                    |  |  |  |  |  |

| Slit16              | 16-bit signed literal ∈ {-3276832767}                                                |  |  |  |  |  |

| Slit6               | 6-bit signed literal ∈ {-1616}                                                       |  |  |  |  |  |

| Wb                  | Base W register ∈ {W0W15}                                                            |  |  |  |  |  |

| Wd                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |  |  |  |  |  |

| Wdo                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |  |  |  |  |  |

#### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| AC CHARACTERISTICS |        | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \mbox{(}^{(1)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array} $ |           |              |           |       |                                                         |

|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|-----------|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                                       | Min.      | Тур.         | Max.      | Units | Conditions                                              |

|                    |        | ADC A                                                                                                                                                                                                                                                                                                | ccuracy ( | 10-Bit N     | lode)     |       |                                                         |

| AD20b              | Nr     | Resolution                                                                                                                                                                                                                                                                                           | 10        | 10 Data Bits |           | bits  |                                                         |

| AD21b INL          | INL    | Integral Nonlinearity                                                                                                                                                                                                                                                                                | -0.625    |              | 0.625     | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |

|                    |        |                                                                                                                                                                                                                                                                                                      | -1.5      |              | 1.5       | LSb   | +85°C < TA ≤ +125°C (Note 2)                            |

| AD22b DNL          | DNL    | Differential Nonlinearity                                                                                                                                                                                                                                                                            | -0.25     | —            | 0.25      | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |

|                    |        |                                                                                                                                                                                                                                                                                                      | -0.25     | —            | 0.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD23b              | Gerr   | Gain Error                                                                                                                                                                                                                                                                                           | -2.5      | —            | 2.5       | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                   |

|                    |        |                                                                                                                                                                                                                                                                                                      | -2.5      |              | 2.5       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD24b              | EOFF   | Offset Error                                                                                                                                                                                                                                                                                         | -1.25     | —            | 1.25      | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C \text{ (Note 2)}$ |

|                    |        |                                                                                                                                                                                                                                                                                                      | -1.25     | —            | 1.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |

| AD25b              | —      | Monotonicity                                                                                                                                                                                                                                                                                         | _         |              | _         | —     | Guaranteed                                              |

|                    |        | Dynamic P                                                                                                                                                                                                                                                                                            | erforman  | ce (10-E     | Bit Mode) |       |                                                         |

| AD30b              | THD    | Total Harmonic Distortion <sup>(3)</sup>                                                                                                                                                                                                                                                             | _         | 64           |           | dB    |                                                         |

| AD31b              | SINAD  | Signal to Noise and Distortion <sup>(3)</sup>                                                                                                                                                                                                                                                        |           | 57           |           | dB    |                                                         |

| AD32b              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup>                                                                                                                                                                                                                                                        | —         | 72           | —         | dB    |                                                         |

| AD33b              | Fnyq   | Input Signal Bandwidth <sup>(3)</sup>                                                                                                                                                                                                                                                                |           | 550          | —         | kHz   |                                                         |

| AD34b              | ENOB   | Effective Number of Bits <sup>(3)</sup>                                                                                                                                                                                                                                                              | _         | 9.4          | —         | bits  |                                                         |

## TABLE 30-59: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

**3:** Parameters are characterized but not tested in manufacturing.

| DC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |      |      |      |       |                                                                    |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------|

| Param.             | Symbol | Characteristic                                                                                                                    | Min. | Тур. | Max. | Units | Conditions                                                         |

| HDO10              | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>                                                                          |      | —    | 0.4  | V     | IOL ≤ 5 mA, VDD = 3.3V<br>(Note 1)                                 |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>                                                                          | —    | —    | 0.4  | V     | IOL ≤ 8 mA, VDD = 3.3V<br>(Note 1)                                 |

| HDO20              | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup>                                                                       | 2.4  | —    | —    | V     | IOH ≥ -10 mA, VDD = 3.3V<br>(Note 1)                               |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup>                                                                       | 2.4  | —    | —    | V     | ІОн ≥ 15 mA, VDD = 3.3V<br>(Note 1)                                |

| HDO20A             | Voн1   | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup>                                                                       | 1.5  | —    | —    | V     | IOH ≥ -3.9 mA, VDD = 3.3V<br>(Note 1)                              |

|                    |        |                                                                                                                                   | 2.0  | —    | —    |       | $IOH \ge -3.7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$<br>(Note 1)  |

|                    |        |                                                                                                                                   | 3.0  | —    | —    |       | IOH ≥ -2 mA, VDD = 3.3V<br>(Note 1)                                |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup>                                                                       | 1.5  | _    | _    | V     | IOH ≥ -7.5 mA, VDD = 3.3V<br>(Note 1)                              |

|                    |        |                                                                                                                                   | 2.0  | _    | _    |       | $IOH \ge -6.8 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$<br>(Note 1) |

|                    |        |                                                                                                                                   | 3.0  | _    | —    |       | IOH ≥ -3 mA, VDD = 3.3V<br>(Note 1)                                |

## TABLE 31-8: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<15:7> and RC3

For 64-pin devices: RA4, RA9, RB<15:7>, RC3 and RC15

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |          |          |      |  |  |

|-------------------------|-------------|----------|----------|------|--|--|

| Dimension               | MIN         | NOM      | MAX      |      |  |  |

| Number of Pins          | N           | 44       |          |      |  |  |

| Pitch                   | е           |          | 0.65 BSC |      |  |  |

| Overall Height          | A           | 0.80     | 0.90     | 1.00 |  |  |

| Standoff                | A1          | 0.00     | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.20 REF |          |      |  |  |

| Overall Width           | E           | 8.00 BSC |          |      |  |  |

| Exposed Pad Width       | E2          | 6.25     | 6.45     | 6.60 |  |  |

| Overall Length          | D           | 8.00 BSC |          |      |  |  |

| Exposed Pad Length      | D2          | 6.25     | 6.45     | 6.60 |  |  |

| Terminal Width          | b           | 0.20     | 0.30     | 0.35 |  |  |

| Terminal Length         | L           | 0.30     | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | K           | 0.20     | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |            |      |      |  |

|--------------------------|------------------|------------|------|------|--|

| D                        | Dimension Limits |            |      | MAX  |  |

| Number of Leads          | N                | 64         |      |      |  |

| Lead Pitch               | е                | 0.50 BSC   |      |      |  |

| Overall Height           | А                | -          | -    | 1.20 |  |

| Molded Package Thickness | A2               | 0.95       | 1.00 | 1.05 |  |