Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc204t-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | —           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | —           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

# 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

# 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

# 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

# 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

# 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

# 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0                                          | U-0                                                | U-0             | U-0              | U-0              | U-0              | U-0                | U-0   |  |  |

|----------------------------------------------|----------------------------------------------------|-----------------|------------------|------------------|------------------|--------------------|-------|--|--|

|                                              | —                                                  | _               | —                | —                | —                | —                  | _     |  |  |

| bit 15                                       |                                                    |                 |                  |                  |                  | •                  | bit 8 |  |  |

|                                              |                                                    |                 |                  |                  |                  |                    |       |  |  |

| U-0                                          | U-0                                                | R/W-0           | R/W-0            | U-0              | U-0              | U-0                | U-0   |  |  |

| —                                            | —                                                  | DAE             | DOOVR            | —                | —                | —                  | —     |  |  |

| bit 7                                        |                                                    |                 |                  |                  |                  |                    | bit 0 |  |  |

|                                              |                                                    |                 |                  |                  |                  |                    |       |  |  |

| Legend:                                      |                                                    |                 |                  |                  |                  |                    |       |  |  |

| R = Readab                                   | le bit                                             | W = Writable    | bit              | U = Unimplei     | mented bit, read | as '0'             |       |  |  |

| -n = Value a                                 | It POR                                             | '1' = Bit is se | t                | '0' = Bit is cle | eared            | x = Bit is unknown |       |  |  |

|                                              |                                                    |                 |                  |                  |                  |                    |       |  |  |

| bit 15-6                                     | Unimplemen                                         | ted: Read as    | '0'              |                  |                  |                    |       |  |  |

| bit 5                                        | DAE: DMA A                                         | ddress Error S  | Soft Trap Status | s bit            |                  |                    |       |  |  |

| 1 = DMA address error soft trap has occurred |                                                    |                 |                  |                  |                  |                    |       |  |  |

|                                              | 0 = DMA address error soft trap has not occurred   |                 |                  |                  |                  |                    |       |  |  |

| bit 4                                        | it 4 DOOVR: DO Stack Overflow Soft Trap Status bit |                 |                  |                  |                  |                    |       |  |  |

| 1 = DO stack overflow soft trap has occurred |                                                    |                 |                  |                  |                  |                    |       |  |  |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

# REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | —   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                                 |                  |                        |                                    |  |  |  |  |

|-----------------------------------|------------------|------------------------|------------------------------------|--|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |  |

|                                   |                  |                        |                                    |  |  |  |  |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

# REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                                                                    |                      |                    |  |  |

|-------------------|--------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | e Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                   | '0' = Bit is cleared | x = Bit is unknown |  |  |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

# REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------|---------------|--------------------|-------|--|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                       | >             |                    |       |  |  |

| bit 15             |                                            |                                                 |                                            |                                    |               |                    | bit 8 |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                                | U-0           | U-0                | U-0   |  |  |

| _                  |                                            |                                                 | —                                          |                                    |               | <u> </u>           | _     |  |  |

| bit 7              |                                            |                                                 |                                            |                                    |               |                    | bit 0 |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| Legend:            |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplemented bit, read as '0' |               |                    |       |  |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is cleared               |               | x = Bit is unknown |       |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                    |       |  |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                                    |               |                    |       |  |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers)        | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                                    | the Correspon | ding RPn Pin b     | its   |  |  |

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |

### TABLE 12-1: TIMER MODE SETTINGS

# FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

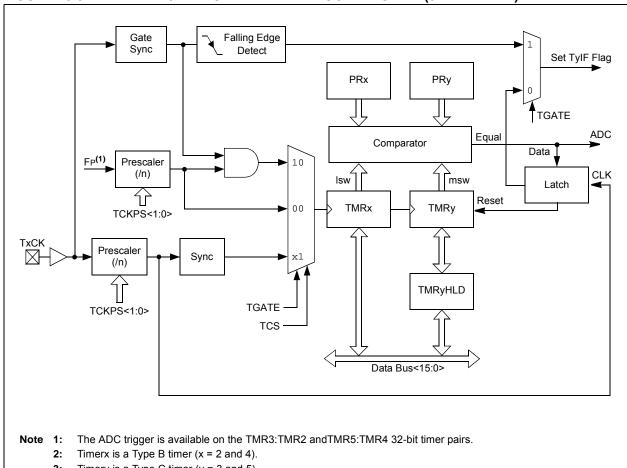

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0                                | U-0        | U-0            | U-0                                     | U-0                                | U-0                     | U-0                     | U-0         |

|------------------------------------|------------|----------------|-----------------------------------------|------------------------------------|-------------------------|-------------------------|-------------|

| —                                  | —          | —              | _                                       | —                                  | —                       | —                       | _           |

| bit 15                             |            |                |                                         |                                    |                         |                         | bit 8       |

|                                    |            |                |                                         |                                    |                         |                         |             |

| U-0                                | U-0        | U-0            | U-0                                     | U-0                                | R/W-0                   | R/W-0                   | R/W-0       |

| —                                  | —          | —              | _                                       | —                                  | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |

| bit 7                              |            |                |                                         |                                    |                         |                         | bit 0       |

|                                    |            |                |                                         |                                    |                         |                         |             |

| Legend:                            |            |                |                                         |                                    |                         |                         |             |

| R = Readable                       | bit        | W = Writable   | bit                                     | U = Unimplemented bit, read as '0' |                         |                         |             |

| -n = Value at POR '1' = Bit is set |            |                | '0' = Bit is cleared x = Bit is unknown |                                    |                         | own                     |             |

|                                    |            |                |                                         |                                    |                         |                         |             |

| bit 15-3                           | Unimplemen | ted: Read as ' | י'                                      |                                    |                         |                         |             |

### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

| R/W-0         | R/W-0    | R/W-0            | U-0             | R/W-0, HC                               | R/W-0                | R-0   | R-1   |

|---------------|----------|------------------|-----------------|-----------------------------------------|----------------------|-------|-------|

| UTXISEL1      | UTXINV   | UTXISEL0         | —               | UTXBRK                                  | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15        |          |                  |                 |                                         |                      |       | bit 8 |

|               |          |                  |                 |                                         |                      |       |       |

| R/W-0         | R/W-0    | R/W-0            | R-1             | R-0                                     | R-0                  | R/C-0 | R-0   |

| URXISEL1      | URXISEL0 | ADDEN            | RIDLE           | PERR                                    | FERR                 | OERR  | URXDA |

| bit 7         |          |                  |                 |                                         |                      |       | bit C |

|               |          |                  |                 |                                         |                      |       |       |

| Legend:       |          | HC = Hardward    | e Clearable bit | C = Clearable                           | e bit                |       |       |

| R = Readable  | e bit    | W = Writable b   | bit             | U = Unimplemented bit, read as '0'      |                      |       |       |

| -n = Value at | POR      | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unknown |                      |       | nown  |

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- <u>If IREN = 0:</u> 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup> 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

# REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | —   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

|        |     |     |     |          |          |          |          |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 15-12 Unimplemented: Read as '0'

| DIL 10-12 | Uninpienienieu. Reau as 0                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18                                                                                                                                                                                   |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved                                                                                                                                                                |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

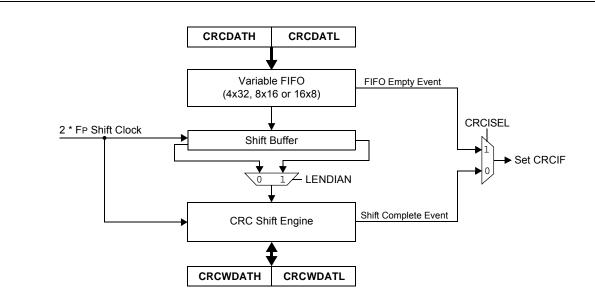

# 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

# FIGURE 26-1: CRC BLOCK DIAGRAM

NOTES:

| DC CHARACTERISTICS |                       |                                                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                                                                |  |

|--------------------|-----------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol Characteristic |                                                     | Min.                                                                                                                                                                                                 | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |

|                    |                       | Program Flash Memory                                |                                                                                                                                                                                                      |                     |      |       |                                                                |  |

| D130               | Eр                    | Cell Endurance                                      | 10,000                                                                                                                                                                                               | —                   | _    | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr                   | VDD for Read                                        | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D132b              | VPEW                  | VDD for Self-Timed Write                            | 3.0                                                                                                                                                                                                  | —                   | 3.6  | V     |                                                                |  |

| D134               | TRETD                 | Characteristic Retention                            | 20                                                                                                                                                                                                   | —                   |      | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP                  | Supply Current during<br>Programming <sup>(2)</sup> | —                                                                                                                                                                                                    | 10                  |      | mA    |                                                                |  |

| D136               | IPEAK                 | Instantaneous Peak Current<br>During Start-up       | —                                                                                                                                                                                                    | —                   | 150  | mA    |                                                                |  |

| D137a              | Тре                   | Page Erase Time                                     | 17.7                                                                                                                                                                                                 | —                   | 22.9 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>     |  |

| D137b              | Тре                   | Page Erase Time                                     | 17.5                                                                                                                                                                                                 | —                   | 23.1 | ms    | TPE = 146893 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>    |  |

| D138a              | Tww                   | Word Write Cycle Time                               | 41.7                                                                                                                                                                                                 | —                   | 53.8 | μs    | Tww = 346 FRC cycles,<br>TA = +85°C (See <b>Note 3)</b>        |  |

| D138b              | Tww                   | Word Write Cycle Time                               | 41.2                                                                                                                                                                                                 | —                   | 54.4 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C (See <b>Note 3)</b>       |  |

### TABLE 30-14: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Parameter characterized but not tested in manufacturing.

3: Other conditions: FRC = 7.37 MHz, TUN<5:0> = 011111 (for Minimum), TUN<5:0> = 100000 (for Maximum). This parameter depends on the FRC accuracy (see Table 30-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). For complete details on calculating the Minimum and Maximum time, see Section 5.3 "Programming Operations".

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

# TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |           |                                                              |                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                                  |

|--------------------|-----------|--------------------------------------------------------------|-----------------------------|-------------------------------------------------------|------|------|-------|----------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                |                             | Min.                                                  | Тур. | Max. | Units | Conditions                       |

| TQ10               | TtQH      | TQCK High<br>Time                                            | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        |      |      | ns    | Must also meet<br>Parameter TQ15 |

| TQ11               | TtQL      | TQCK Low<br>Time                                             | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        | —    | _    | ns    | Must also meet<br>Parameter TQ15 |

| TQ15               | TtQP      | TQCP Input<br>Period                                         | Synchronous, with prescaler | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50            | —    | _    | ns    |                                  |

| TQ20               | TCKEXTMRL | Delay from External TQCK<br>Clock Edge to Timer<br>Increment |                             | _                                                     | 1    | Тсү  | —     |                                  |

Note 1: These parameters are characterized but not tested in manufacturing.

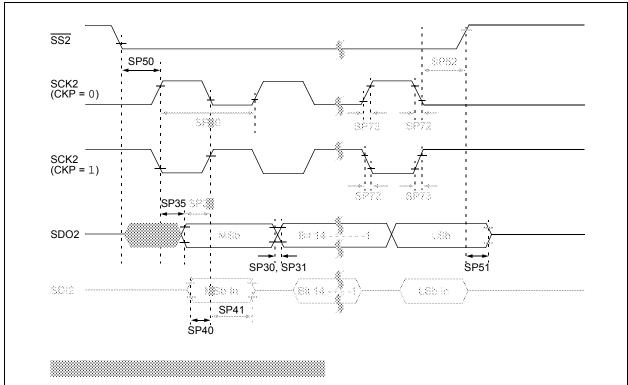

# FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

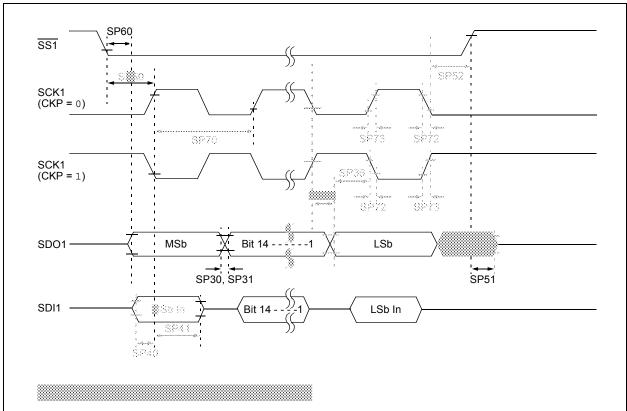

### FIGURE 30-27: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

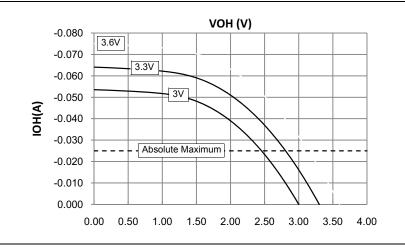

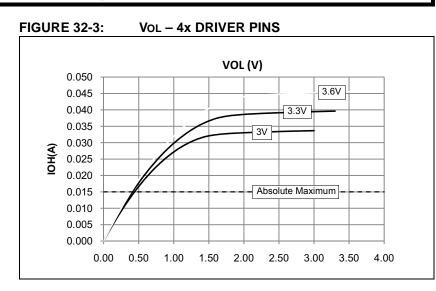

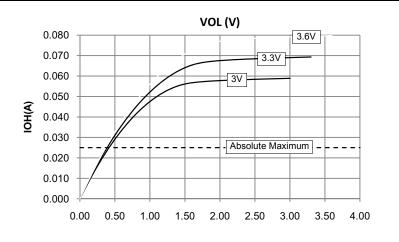

# 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

**FIGURE 32-1: VOH – 4x DRIVER PINS** VOH (V) -0.050 -0.045 3.6V -0.040 3.3V -0.035 3V -0.030 IOH(A) -0.025 -0.020 Absolute Maximum -0.015 -0.010 -0.005 0.000 0.50 1.00 2.00 2.50 3.00 3.50 0.00 1.50 4.00

# FIGURE 32-2: VOH – 8x DRIVER PINS

# FIGURE 32-4: Vol – 8x DRIVER PINS

NOTES: