Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-UFQFN Exposed Pad                                                            |

| Supplier Device Package    | 48-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc204t-i-mv |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

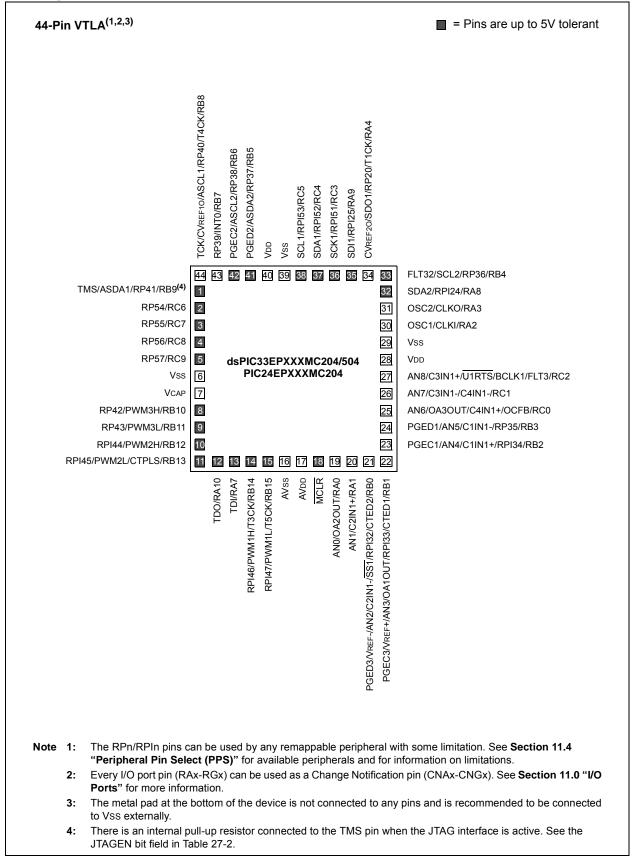

#### Pin Diagrams (Continued)

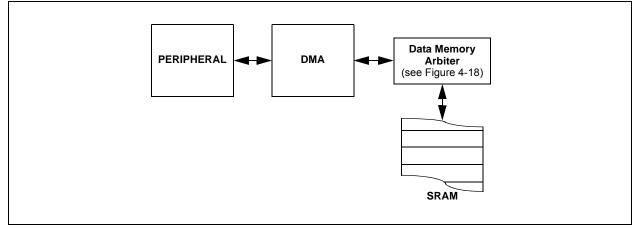

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: DMA CONTROLLER MODULE

| REGISTER     | <u>R 10-2: PMD</u> 2                       | 2: PERIPHER                                                                                                 | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |  |

|--------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| U-0          | U-0                                        | U-0                                                                                                         | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

| _            |                                            | —                                                                                                           |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |

| bit 15       |                                            |                                                                                                             |                 |                   |                 |                 | bit   |  |  |  |  |

| U-0          | U-0                                        | U-0                                                                                                         | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                            |                                                                                                             |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |

| bit 7        |                                            |                                                                                                             |                 |                   |                 |                 | bit   |  |  |  |  |

|              |                                            |                                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

| Legend:      | 1.1.1                                      |                                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

| R = Readab   |                                            | W = Writable b                                                                                              | Dit             | •                 | nented bit, rea |                 |       |  |  |  |  |

| -n = Value a | at POR                                     | '1' = Bit is set                                                                                            |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |

| bit 15-12    | Unimplemen                                 | ted: Read as '0                                                                                             | ,               |                   |                 |                 |       |  |  |  |  |

| bit 11       | -                                          |                                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

|              | •                                          | IC4MD: Input Capture 4 Module Disable bit<br>1 = Input Capture 4 module is disabled                         |                 |                   |                 |                 |       |  |  |  |  |

|              | 0 = Input Cap                              | oture 4 module is                                                                                           | s enabled       |                   |                 |                 |       |  |  |  |  |

| bit 10       | IC3MD: Input Capture 3 Module Disable bit  |                                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

|              |                                            | 1 = Input Capture 3 module is disabled                                                                      |                 |                   |                 |                 |       |  |  |  |  |

|              |                                            | oture 3 module is                                                                                           |                 |                   |                 |                 |       |  |  |  |  |

| bit 9        |                                            | t Capture 2 Mod                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

|              |                                            | oture 2 module is<br>oture 2 module is                                                                      |                 |                   |                 |                 |       |  |  |  |  |

| bit 8        | IC1MD: Input                               | t Capture 1 Mod                                                                                             | ule Disable bit |                   |                 |                 |       |  |  |  |  |

|              | 1 = Input Cap                              | oture 1 module is<br>oture 1 module is                                                                      | s disabled      |                   |                 |                 |       |  |  |  |  |

| bit 7-4      |                                            | ted: Read as '0                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

| bit 3        | OC4MD: Out                                 | put Compare 4                                                                                               | Module Disable  | e bit             |                 |                 |       |  |  |  |  |

|              |                                            | 1 = Output Compare 4 module is disabled                                                                     |                 |                   |                 |                 |       |  |  |  |  |

|              | -                                          | ompare 4 modu                                                                                               |                 |                   |                 |                 |       |  |  |  |  |

| bit 2        | OC3MD: Output Compare 3 Module Disable bit |                                                                                                             |                 |                   |                 |                 |       |  |  |  |  |

|              | •                                          | <ul> <li>1 = Output Compare 3 module is disabled</li> <li>0 = Output Compare 3 module is enabled</li> </ul> |                 |                   |                 |                 |       |  |  |  |  |

| L:1 4        | -                                          | -                                                                                                           |                 | . h.:4            |                 |                 |       |  |  |  |  |

| bit 1        |                                            | put Compare 2                                                                                               |                 |                   |                 |                 |       |  |  |  |  |

|              | $\perp$ – Output Co                        | ompare 2 modu                                                                                               |                 |                   |                 |                 |       |  |  |  |  |

|              | 0 = Output Co                              | ompare 2 modul                                                                                              | le is enabled   |                   |                 |                 |       |  |  |  |  |

| bit 0        |                                            | ompare 2 modul<br>put Compare 1                                                                             |                 | e bit             |                 |                 |       |  |  |  |  |

| bit 0        | OC1MD: Out                                 | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul                                                         | Module Disable  | e bit             |                 |                 |       |  |  |  |  |

#### ~

### 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-----|-------|-------------|-------|-------|-------|-------|--|--|--|

| —      | —   |       | RP118R<5:0> |       |       |       |       |  |  |  |

| bit 15 |     |       |             |       |       |       | bit 8 |  |  |  |

|        |     |       |             |       |       |       |       |  |  |  |

| U-0    | U-0 | U-0   | U-0         | U-0   | U-0   | U-0   | U-0   |  |  |  |

| —      | —   |       | —           | _     | _     | —     | _     |  |  |  |

| bit 7  |     |       |             |       |       |       | bit 0 |  |  |  |

|        |     |       |             |       |       |       |       |  |  |  |

| Legend:           |                                                                  |                      |                    |  |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------------|-------|-------|-------|-------|-------|--|--|

| —     | —   | RP120R<5:0> |       |       |       |       |       |  |  |

| bit 7 |     |             |       |       |       |       | bit 0 |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

# 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

#### 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

| U-0       R/W-0       R/W       R/W       R/W </th <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>R/W-0</th> <th>U-0</th> <th>U-0</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0         | R/W-0                                                                                                                                        | R/W-0                             | R/W-0                            | R/W-0                   | R/W-0            | U-0               | U-0           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|-------------------------|------------------|-------------------|---------------|--|

| U-0       U-0       RW-0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PHR           | PHF                                                                                                                                          | PLR                               | PLF                              | FLTLEBEN                | CLLEBEN          | —                 | _             |  |

| -         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPH         BPHL         BPLH         BE         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 15        |                                                                                                                                              |                                   |                                  |                         |                  |                   | bit           |  |

| bit 7       t         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking is applied to selected Fault input       1 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected current-limit input       0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is applied to selected Current-limit input       0 = Leading-Edge Blanking is applied to sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0           | U-0                                                                                                                                          | R/W-0                             | R/W-0                            | R/W-0                   | R/W-0            | R/W-0             | R/W-0         |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>nn = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 PHR: PWMxH Rising Edge Trigger Enable bit<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxH<br>1 = Falling edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxH<br>1 = Rising edge of PWMxH will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Rising edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores rising edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Falling edge of PWMxL will trigget Leading-Edge Blanking counter<br>0 = Leading-Edge Blanking ignores falling edge of PWMxL<br>1 = Leading-Edge Blanking is applied to selected Fault input<br>0 = Leading-Edge Blanking is applied to selected Fault input<br>1 = Leading-Edge Blanking is applied to selected Current-limit input<br>1 = Leading-Edge Blanking is not applied to selected current-limit input<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high<br>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low<br>0 = No blanking when selected blanking signal Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when Selected blanking signal is low<br>0 = No blanking when PWMxH dupt is high<br>0 = No blanking when PWMxH dupt signals) when PWMxH output is high<br>0 = No blanking when PWMxH tow Enable bit<br>1 = State blanking (of current-limit and/ | _             | _                                                                                                                                            | BCH <sup>(1)</sup>                | BCL <sup>(1)</sup>               | BPHH                    | BPHL             | BPLH              | BPLL          |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit       1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PWMxH         bit 13       PLR: PWMxL Rising Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PWMxL         bit 13       PLR: PWMxL Falling Edge Trigger Enable bit       1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking is not applied to selected Fault input         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking is not applied to selected current-limit input         bit 9-6       Unimplemented: Read as '0'       1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking signal is high       1 = State blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7         |                                                                                                                                              |                                   |                                  |                         |                  |                   | bit           |  |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxH       11 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxH       11 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores fising edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit       1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL       0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input       0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking signal Figh Enable bit         1 = State blanking in Selected Blanking Singal High Enable bit <sup>(1)</sup> 1 = State blanking in Sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:       |                                                                                                                                              |                                   |                                  |                         |                  |                   |               |  |

| <ul> <li>PHR: PWMxH Rising Edge Trigger Enable bit         <ol> <li>Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R = Readabl   | e bit                                                                                                                                        | W = Writable                      | bit                              | U = Unimpler            | mented bit, read | as '0'            |               |  |

| <ul> <li>1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxH</li> <li>PHF: PWMxH Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>PLR: PVMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>Det Leading-Edge Blanking ignores ralling edge of PWMxL</li> <li>D = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit</li> <li>1 = Leading-Edge Blanking Signal Liph Enable bit<sup>(1)</sup></li> <li>1 = State blanking (or current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No b</li></ul>                                                                                                                                                                | -n = Value at | POR                                                                                                                                          | '1' = Bit is set                  | :                                | '0' = Bit is cle        | ared             | x = Bit is unkr   | nown          |  |

| <ul> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>bit 13 PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL. will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 12 FLTLEBEN: Fault Input Leading-Edge Blanking Counter</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH output is nigh</li> <li>0 = No bla</li></ul>                                                                                                                                                                 | bit 15        | 1 = Rising ed                                                                                                                                | ge of PWMxH                       | will trigger Le                  | ading-Edge Bla          |                  |                   |               |  |

| <ul> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>pLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11</li> <li>FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking when selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when PWMxH dutput is high</li> <li>0 = No blanking when PWMxH Low Enable bit</li> <li>1 = State blanking (of</li></ul>                                                                                                                                                         | bit 14        | 1 = Falling ed                                                                                                                               | lge of PWMxH                      | will trigger Le                  | eading-Edge Bla         | 0                |                   |               |  |

| bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit         1 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = Leading-Edge Blanking is ont applied to selected current-limit input         0 = No blanking when selected Blanking signal Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         0 = No blanking when P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 13        | 1 = Rising ed                                                                                                                                | ge of PWMxL                       | will trigger Le                  | ading-Edge Bla          |                  |                   |               |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li></ul>                                                                                                                                                             | bit 12        | 1 = Falling ed                                                                                                                               | lge of PWMxL                      | will trigger Le                  | ading-Edge Bla          |                  |                   |               |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>bit 9-6</li> <li>Unimplemented: Read as '0'</li> <li>bit 5</li> <li>BCH: Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>bit 4</li> <li>BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxL output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL Ligh Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>0 = No blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL Low Enable bit</li> <li>1 = State blanking in PWMxL output is high</li> </ul>                                                                                                                                                                                                 | bit 11        | 1 = Leading-E                                                                                                                                | Edge Blanking                     | is applied to                    | selected Fault in       | nput             |                   |               |  |

| bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         0 = No blanking when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       State blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxL output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 10        | 1 = Leading-E                                                                                                                                | Edge Blanking                     | is applied to                    | selected current        | t-limit input    |                   |               |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 9-6       | Unimplemen                                                                                                                                   | ted: Read as '                    | 0'                               |                         |                  |                   |               |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>BPHH: Blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 5         | 1 = State blar                                                                                                                               | nking (of currer                  | nt-limit and/or                  | Fault input sigr        |                  | cted blanking s   | ignal is high |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 4         | 1 = State blar                                                                                                                               | nking (of currer                  | nt-limit and/or                  | Fault input sigr        |                  | cted blanking s   | ignal is low  |  |

| 1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 3         | <b>BPHH:</b> Blanking in PWMxH High Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high |                                   |                                  |                         |                  |                   |               |  |

| bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         0 = No blanking when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 2         | <b>BPHL:</b> Blanking in PWMxH Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low   |                                   |                                  |                         |                  |                   |               |  |

| bit 0 <b>BPLL:</b> Blanking in PWMxL Low Enable bit<br>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 1         | <b>BPLH:</b> Blanki<br>1 = State blar                                                                                                        | ing in PWMxL<br>hking (of currer  | High Enable I<br>nt-limit and/or | bit<br>Fault input sigr | nals) when PWN   | /IxL output is hi | gh            |  |