Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

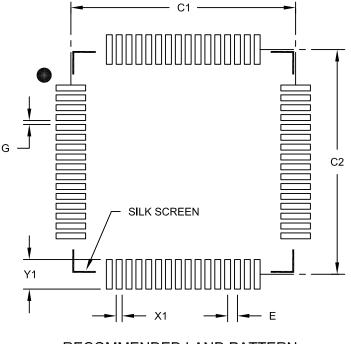

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc206-h-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup> Pin Buffer Type Type PPS |                     |                         | PPS              | Description                                                                                                                                                                        |

|--------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                         | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                             | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                             | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                             | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                             | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                          | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                          | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                          | <br> <br>           | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                             | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                     |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                                | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                         | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                   | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                    | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                        | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                         | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                          | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                             | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                     |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                             |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                             | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                            | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                            | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                            | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                            | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                            | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                             |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                    | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip   | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

# TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      | -          | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

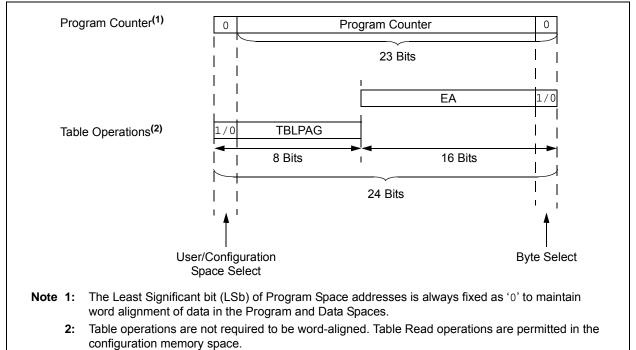

# 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address |            |               |               |     |  |  |  |

|------------------------|---------------|-----------------------|------------|---------------|---------------|-----|--|--|--|

| Access Type            | Space         | <23>                  | <22:16>    | <15>          | <14:1>        | <0> |  |  |  |

| Instruction Access     | User          | 0                     | 0 PC<22:1> |               |               |     |  |  |  |

| (Code Execution)       |               |                       | 0xx xxxx x | x xxxx xxx0   |               |     |  |  |  |

| TBLRD/TBLWT            | User          | TB                    | LPAG<7:0>  |               | Data EA<15:0> |     |  |  |  |

| (Byte/Word Read/Write) |               | 0                     | xxx xxxx   | XXXX XXX      | ***           |     |  |  |  |

|                        | Configuration | TB                    | LPAG<7:0>  | Data EA<15:0> |               |     |  |  |  |

|                        |               | 1                     | xxx xxxx   | XXXX XX       | ***           |     |  |  |  |

## FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 |       | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

# **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0          | U-0                                          | U-0             | U-0              | U-0                                     | U-0              | U-0    | U-0   |  |  |  |

|--------------|----------------------------------------------|-----------------|------------------|-----------------------------------------|------------------|--------|-------|--|--|--|

|              | —                                            | _               | —                | —                                       | —                | —      | _     |  |  |  |

| bit 15       |                                              |                 |                  |                                         |                  | •      | bit 8 |  |  |  |

|              |                                              |                 |                  |                                         |                  |        |       |  |  |  |

| U-0          | U-0                                          | R/W-0           | R/W-0            | U-0                                     | U-0              | U-0    | U-0   |  |  |  |

| —            | —                                            | DAE             | DOOVR            | —                                       | —                | —      | —     |  |  |  |

| bit 7        |                                              |                 |                  |                                         |                  |        | bit 0 |  |  |  |

|              |                                              |                 |                  |                                         |                  |        |       |  |  |  |

| Legend:      |                                              |                 |                  |                                         |                  |        |       |  |  |  |

| R = Readab   | le bit                                       | W = Writable    | bit              | U = Unimplei                            | mented bit, read | as '0' |       |  |  |  |

| -n = Value a | It POR                                       | '1' = Bit is se | t                | '0' = Bit is cleared x = Bit is unknown |                  |        |       |  |  |  |

|              |                                              |                 |                  |                                         |                  |        |       |  |  |  |

| bit 15-6     | Unimplemen                                   | ted: Read as    | '0'              |                                         |                  |        |       |  |  |  |

| bit 5        | DAE: DMA A                                   | ddress Error S  | Soft Trap Status | s bit                                   |                  |        |       |  |  |  |

|              | 1 = DMA add                                  | ress error soft | trap has occur   | red                                     |                  |        |       |  |  |  |

|              | 0 = DMA add                                  | ress error soft | trap has not o   | ccurred                                 |                  |        |       |  |  |  |

| bit 4        | DOOVR: DO                                    | Stack Overflov  | v Soft Trap Sta  | tus bit                                 |                  |        |       |  |  |  |

|              | 1 = DO stack overflow soft trap has occurred |                 |                  |                                         |                  |        |       |  |  |  |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | _   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

# 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

## REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

# 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

| R/W-0        | R/W-0                                                                                                    | R/W-0                              | R/W-0          | U-0               | U-0                | U-0              | U-0          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-------------------|--------------------|------------------|--------------|--|--|--|--|

|              | TRGDIV<3:0>                                                                                              |                                    |                | —                 |                    | —                | _            |  |  |  |  |

| bit 15       |                                                                                                          |                                    |                |                   |                    |                  | bit 8        |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |  |  |

| U-0          | U-0                                                                                                      | R/W-0                              | R/W-0          | R/W-0             | R/W-0              | R/W-0            | R/W-0        |  |  |  |  |

| _            |                                                                                                          |                                    |                | TRGSTF            | RT<5:0> <b>(1)</b> |                  |              |  |  |  |  |

| bit 7        |                                                                                                          |                                    |                |                   |                    |                  | bit          |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |  |  |

| Legend:      | 1. 1.4                                                                                                   |                                    |                |                   |                    | (0)              |              |  |  |  |  |

| R = Readab   |                                                                                                          | W = Writable                       |                | •                 | nented bit, read   |                  |              |  |  |  |  |

| -n = Value a | t POR                                                                                                    | '1' = Bit is set                   |                | '0' = Bit is clea | ared               | x = Bit is unkn  | own          |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |  |  |

| bit 15-12    |                                                                                                          | <b>)&gt;:</b> Trigger # Ou         | -              |                   |                    |                  |              |  |  |  |  |

|              | 1111 = Trigger output for every 16th trigger event                                                       |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 1110 = Trigger output for every 15th trigger event                                                       |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 1101 = Trigger output for every 14th trigger event                                                       |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 1100 = Trigger output for every 13th trigger event<br>1011 = Trigger output for every 12th trigger event |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 1010 = Trigger output for every 11th trigger event                                                       |                                    |                |                   |                    |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                    |                  |              |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                   |                    |                  |              |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                   |                    |                  |              |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                    |                  |              |  |  |  |  |

|              | 0101 = Trigger output for every 6th trigger event                                                        |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 0100 = Trigg                                                                                             | ger output for ev                  | ery 5th trigge | r event           |                    |                  |              |  |  |  |  |

|              | 0011 = Trigger output for every 4th trigger event                                                        |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 0010 = Trigger output for every 3rd trigger event                                                        |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 0001 = Trigger output for every 2nd trigger event                                                        |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 0000 = Trigg                                                                                             | ger output for ev                  | ery trigger ev | ent               |                    |                  |              |  |  |  |  |

| bit 11-6     | -                                                                                                        | nted: Read as '                    |                |                   |                    |                  |              |  |  |  |  |

| bit 5-0      | TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits <sup>(1)</sup>                                 |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | 111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled       |                                    |                |                   |                    |                  |              |  |  |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |  |  |

|              | •                                                                                                        |                                    |                | ·                 |                    |                  |              |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                 |                    |                  |              |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                 |                    |                  |              |  |  |  |  |

|              | •<br>•<br>•                                                                                              | aits 2 PW/M ava                    | les hefore co  | nerating the fire | t trigger event :  | after the module | a is anabled |  |  |  |  |

|              |                                                                                                          | /aits 2 PWM cyc<br>/aits 1 PWM cyc |                |                   |                    |                  |              |  |  |  |  |

# REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

| R/W-1           | R/W-1                                                       | R/W-0                                                                                                                                                | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |  |  |  |

|-----------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|--|--|--|

| PENH            | PENL                                                        | POLH                                                                                                                                                 | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |  |  |  |

| bit 15          |                                                             | •                                                                                                                                                    |                            |                      |                           |                 | bit    |  |  |  |

| R/W-0           | R/W-0                                                       | R/W-0                                                                                                                                                | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |  |  |  |

| -               | -                                                           | -                                                                                                                                                    |                            | -                    | -                         | -               | R/W-0  |  |  |  |

| OVRDAT1         | OVRDAT0                                                     | FLTDAT1                                                                                                                                              | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |  |  |  |

| bit 7           |                                                             |                                                                                                                                                      |                            |                      |                           |                 | bit    |  |  |  |

| Legend:         |                                                             |                                                                                                                                                      |                            |                      |                           |                 |        |  |  |  |

| R = Readable    | bit                                                         | W = Writable                                                                                                                                         | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |  |  |  |

| -n = Value at F | POR                                                         | '1' = Bit is set                                                                                                                                     |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |  |  |  |

| bit 15          |                                                             | xH Output Pin                                                                                                                                        | Ownorship hit              |                      |                           |                 |        |  |  |  |

| bit 15          |                                                             | odule controls                                                                                                                                       | •                          |                      |                           |                 |        |  |  |  |

|                 |                                                             | dule controls F                                                                                                                                      |                            |                      |                           |                 |        |  |  |  |

| bit 14          |                                                             |                                                                                                                                                      | •                          |                      |                           |                 |        |  |  |  |

|                 | 1 = PWMx mo                                                 | PENL: PWMxL Output Pin Ownership bit<br>1 = PWMx module controls PWMxL pin                                                                           |                            |                      |                           |                 |        |  |  |  |

|                 | 0 = GPIO mo                                                 | dule controls F                                                                                                                                      | WMxL pin                   |                      |                           |                 |        |  |  |  |

| bit 13          | POLH: PWM                                                   | xH Output Pin                                                                                                                                        | Polarity bit               |                      |                           |                 |        |  |  |  |

|                 | 1 = PWMxH pin is active-low<br>0 = PWMxH pin is active-high |                                                                                                                                                      |                            |                      |                           |                 |        |  |  |  |

|                 |                                                             | -                                                                                                                                                    | •                          |                      |                           |                 |        |  |  |  |

| bit 12          |                                                             | POLL: PWMxL Output Pin Polarity bit<br>_ = PWMxL pin is active-low                                                                                   |                            |                      |                           |                 |        |  |  |  |

|                 |                                                             | in is active-low                                                                                                                                     |                            |                      |                           |                 |        |  |  |  |

| bit 11-10       | PMOD<1:0>:                                                  | PWMx # I/O F                                                                                                                                         | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |  |  |  |

|                 | 11 = Reserve                                                | ,                                                                                                                                                    |                            |                      |                           |                 |        |  |  |  |

|                 |                                                             | /O pin pair is ir<br>/O pin pair is ir                                                                                                               |                            |                      |                           |                 |        |  |  |  |

|                 |                                                             | O pin pair is in<br>O pin pair is ir                                                                                                                 |                            |                      |                           |                 |        |  |  |  |

| bit 9           |                                                             | verride Enable                                                                                                                                       | •                          |                      |                           |                 |        |  |  |  |

|                 |                                                             | <1> controls or                                                                                                                                      |                            |                      |                           |                 |        |  |  |  |

|                 |                                                             | nerator contro                                                                                                                                       | •                          | •                    |                           |                 |        |  |  |  |

| bit 8           | OVRENL: Ov                                                  | erride Enable                                                                                                                                        | for PWMxL Pir              | n bit                |                           |                 |        |  |  |  |

|                 | 1 = OVRDAT<0> controls output on PWMxL pin                  |                                                                                                                                                      |                            |                      |                           |                 |        |  |  |  |

|                 | •                                                           | nerator contro                                                                                                                                       |                            |                      |                           |                 |        |  |  |  |

| bit 7-6         |                                                             | OVRDAT<1:0>: Data for PWMxH, PWMxL Pins if Override is Enabled bits                                                                                  |                            |                      |                           |                 |        |  |  |  |

|                 |                                                             |                                                                                                                                                      |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |  |  |  |

| bit 5-4         | FLTDAT<1:0                                                  | OVERENL = 1, PWMxL is driven to the state specified by OVRDAT<0>.<br><b>TDAT&lt;1:0&gt;:</b> Data for PWMxH and PWMxL Pins if FLTMOD is Enabled bits |                            |                      |                           |                 |        |  |  |  |

|                 | If Fault is active                                          | ve, PWMxH is                                                                                                                                         | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |  |  |  |

|                 | If Fault is active                                          | ve, PWMxL is                                                                                                                                         | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |  |  |  |

| bit 3-2         | CLDAT<1:0>                                                  | : Data for PWN                                                                                                                                       | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |  |  |  |

|                 |                                                             |                                                                                                                                                      |                            | •                    | ecified by CLDA           |                 |        |  |  |  |

|                 |                                                             | IS AULIVE. F VVI                                                                                                                                     |                            |                      |                           |                 |        |  |  |  |

| Note 1: The     |                                                             |                                                                                                                                                      |                            |                      | enabled (PTEN             |                 |        |  |  |  |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

|                                                                                                                                                                                        | D MALO                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|