Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512mc206-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

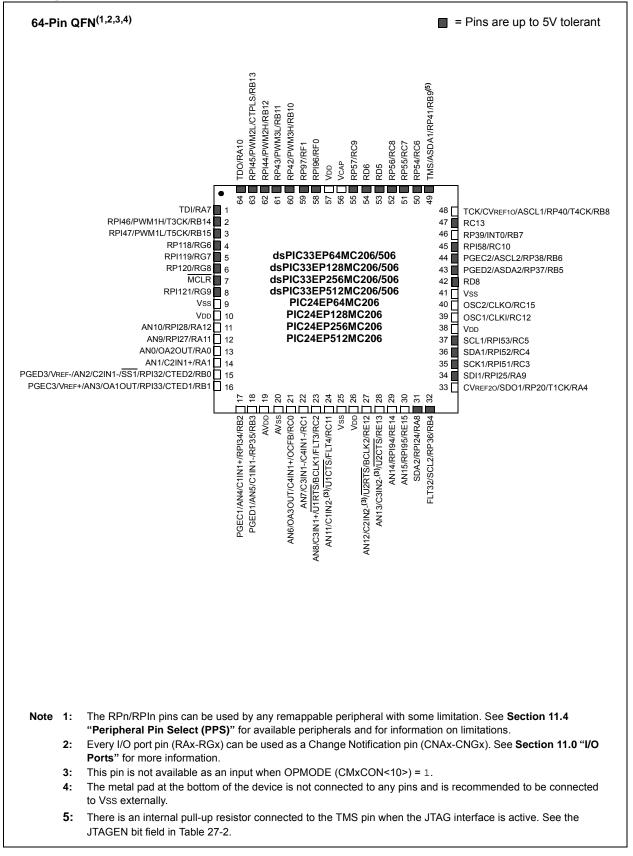

## Pin Diagrams (Continued)

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

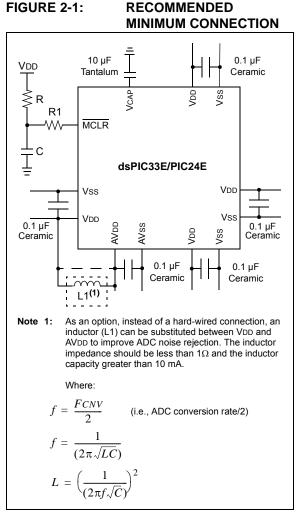

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

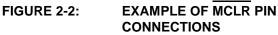

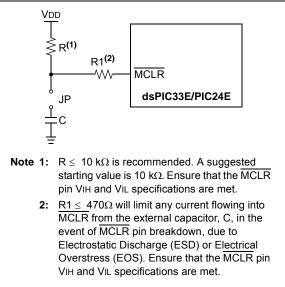

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

## 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

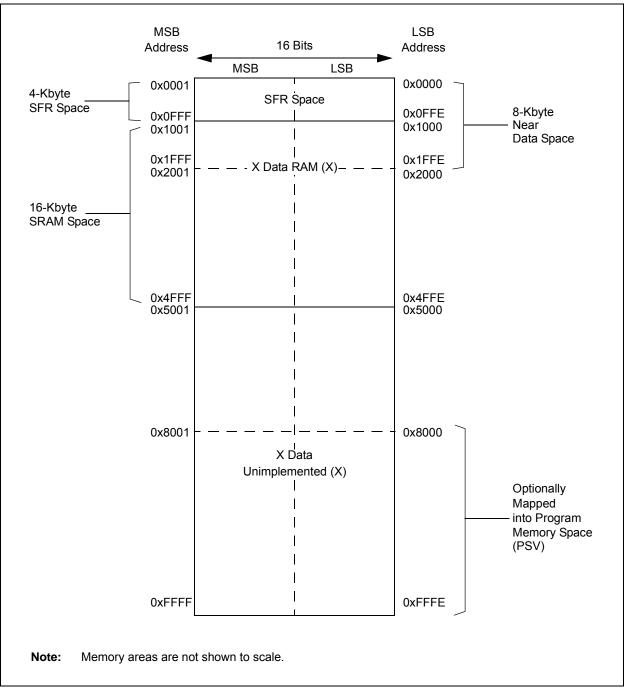

## 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

## 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

## 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

| IABLE 4   | -10.  | 001    |        | JMPARE   |        |           | OUIFU  |       | ARE 4       | REGIS       |              | <u>٢</u> |        |          |           |          |       |               |

|-----------|-------|--------|--------|----------|--------|-----------|--------|-------|-------------|-------------|--------------|----------|--------|----------|-----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5    | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

| OC1CON1   | 0900  | —      | -      | OCSIDL   | C      | CTSEL<2:0 | )>     | —     | ENFLTB      | ENFLTA      | —            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC1RS     | 0904  |        |        |          |        |           |        | Outp  | out Compare | e 1 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC1R      | 0906  |        |        |          |        |           |        |       | Output Co   | mpare 1 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC1TMR    | 0908  |        |        |          |        |           |        |       | Timer V     | alue 1 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC2CON1   | 090A  | _      | —      | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2   | 090C  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC2RS     | 090E  |        |        |          |        |           |        | Outp  | out Compare | e 2 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC2R      | 0910  |        |        |          |        |           |        |       | Output Co   | mpare 2 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC2TMR    | 0912  |        |        |          |        |           |        |       | Timer V     | alue 2 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC3CON1   | 0914  | _      | —      | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS     | 0918  |        |        |          |        |           |        | Outp  | out Compare | e 3 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC3R      | 091A  |        |        |          |        |           |        |       | Output Co   | mpare 3 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC3TMR    | 091C  |        |        |          |        |           |        |       | Timer V     | alue 3 Regi | ster         |          |        |          |           |          |       | xxxx          |

| OC4CON1   | 091E  | _      | —      | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC4RS     | 0922  |        |        |          |        |           |        | Outp  | out Compare | e 4 Seconda | ary Register |          |        |          |           |          |       | xxxx          |

| OC4R      | 0924  |        |        |          |        |           |        |       | Output Co   | mpare 4 Re  | gister       |          |        |          |           |          |       | xxxx          |

| OC4TMR    | 0926  |        |        |          |        |           |        |       | Timer V     | alue 4 Regi | ster         |          |        |          |           |          |       | xxxx          |

## TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | _      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | _      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | _      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | _      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | _      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | _      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | U-0              | U-0   | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

| —               | -     | —                | —     |                   | LEB             | <11:8>          |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | LEE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

## REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x            | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | Ву    | /te 3             |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x            | R/W-x           | R/W-x |

|                 |       |                  | Ву    | /te 2             |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | В     | yte 5            |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  |       | yte 4            |                 |                 |       |

| bit 7           |       |                  |       | -                |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | oit   | W = Writable     | bit   | U = Unimplen     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

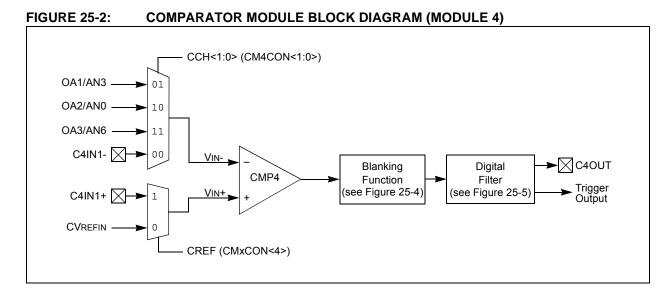

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          |         | ADC Channel |         |

|----------------|---------|-------------|---------|

| value          | CH1     | CH2         | CH3     |

| 1 <b>(2)</b>   | OA1/AN3 | OA2/AN0     | OA3/AN6 |

| 0 <b>(1,2)</b> | OA2/AN0 | AN1         | AN2     |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                                | Description                                       | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected        |

|--------------------|----------------------|--------|----------------------------------------------------------------|---------------------------------------------------|---------------|-------------------------------|---------------------------------|

| 53                 | NEG                  | NEG    | <sub>Acc</sub> (1)                                             | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

|                    |                      | NEG    | f                                                              | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | f,WREG                                                         | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG    | Ws,Wd                                                          | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z                     |

| 54                 | NOP                  | NOP    | · · · · · · · · · · · · · · · · · · ·                          | No Operation                                      | 1             | 1                             | None                            |

|                    |                      | NOPR   |                                                                | No Operation                                      | 1             | 1                             | None                            |

| 55                 | POP                  | POP    | f                                                              | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                            |

|                    |                      | POP    | Wdo                                                            | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                            |

|                    |                      | POP.D  | Wnd                                                            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2                             | None                            |

|                    |                      | POP.S  |                                                                | Pop Shadow Registers                              | 1             | 1                             | All                             |

| 56                 | PUSH                 | PUSH   | f                                                              | Push f to Top-of-Stack (TOS)                      | 1             | 1                             | None                            |

|                    |                      | PUSH   | Wso                                                            | Push Wso to Top-of-Stack (TOS)                    | 1             | 1                             | None                            |

|                    |                      | PUSH.D | Wns                                                            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2                             | None                            |

|                    |                      | PUSH.S |                                                                | Push Shadow Registers                             | 1             | 1                             | None                            |

| 57                 | PWRSAV               | PWRSAV | #lit1                                                          | Go into Sleep or Idle mode                        | 1             | 1                             | WDTO,Sleep                      |

| 58                 | RCALL                | RCALL  | Expr                                                           | Relative Call                                     | 1             | 4                             | SFA                             |

|                    |                      | RCALL  | Wn                                                             | Computed Call                                     | 1             | 4                             | SFA                             |

| 59                 | REPEAT               | REPEAT | #lit15                                                         | Repeat Next Instruction lit15 + 1 times           | 1             | 1                             | None                            |

|                    |                      | REPEAT | Wn                                                             | Repeat Next Instruction (Wn) + 1 times            | 1             | 1                             | None                            |

| 60                 | RESET                | RESET  |                                                                | Software device Reset                             | 1             | 1                             | None                            |

| 61                 | RETFIE               | RETFIE |                                                                | Return from interrupt                             | 1             | 6 (5)                         | SFA                             |

| 62                 | RETLW                | RETLW  | #lit10,Wn                                                      | Return with literal in Wn                         | 1             | 6 (5)                         | SFA                             |

| 63                 | RETURN               | RETURN |                                                                | Return from Subroutine                            | 1             | 6 (5)                         | SFA                             |

| 64                 | RLC                  | RLC    | f                                                              | f = Rotate Left through Carry f                   | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | f,WREG                                                         | WREG = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC    | Ws,Wd                                                          | Wd = Rotate Left through Carry Ws                 | 1             | 1                             | C,N,Z                           |

| 65                 | RLNC                 | RLNC   | f                                                              | f = Rotate Left (No Carry) f                      | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | f,WREG                                                         | WREG = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                             |

|                    |                      | RLNC   | Ws,Wd                                                          | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                             | N,Z                             |

| 66                 | RRC                  | RRC    | f                                                              | f = Rotate Right through Carry f                  | 1             | 1                             | C,N,Z                           |

|                    |                      | RRC    | f,WREG                                                         | WREG = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                           |

| 07                 |                      | RRC    | Ws,Wd                                                          | Wd = Rotate Right through Carry Ws                | 1             | 1                             | C,N,Z                           |

| 67                 | RRNC                 | RRNC   | f                                                              | f = Rotate Right (No Carry) f                     | 1             | 1                             | N,Z                             |

|                    |                      | RRNC   | f,WREG                                                         | WREG = Rotate Right (No Carry) f                  | 1             | 1                             | N,Z                             |

| <u></u>            | ~~~~                 | RRNC   | Ws,Wd                                                          | Wd = Rotate Right (No Carry) Ws                   | 1             | 1                             | N,Z                             |

| 68                 | SAC                  | SAC    | Acc,#Slit4,Wdo <sup>(1)</sup><br>Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                 | 1             | 1                             | None                            |

| 60                 | CE                   | SAC.R  |                                                                | Store Rounded Accumulator                         | 1             | 1                             | None                            |

| 69<br>70           | SE                   | SE     | Ws,Wnd                                                         | Wnd = sign-extended Ws<br>f = 0xFFFF              | 1             | 1                             | C,N,Z<br>None                   |

| 10                 | SETM                 | SETM   | f                                                              |                                                   | -             | 1                             |                                 |

|                    |                      | SETM   | WREG                                                           | WREG = 0xFFFF<br>Ws = 0xFFFF                      | 1             | 1                             | None                            |

| 71                 | SFTAC                | SETM   | Ws<br>Acc, Wn <sup>(1)</sup>                                   | Arithmetic Shift Accumulator by (Wn)              | 1             | 1                             | None<br>OA,OB,OAB,<br>SA,SB,SAB |

|                    |                      | SFTAC  | Acc,#Slit6 <sup>(1)</sup>                                      | Arithmetic Shift Accumulator by Slit6             | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

## TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTERISTICS |      |      | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |            |       |  |  |  |

|--------------------|------|------|----------------------------------------------------------|------------|-------|--|--|--|

| Parameter No.      | Тур. | Max. | Units                                                    | Conditions |       |  |  |  |

| DC61d              | 8    |      | μΑ                                                       | -40°C      |       |  |  |  |

| DC61a              | 10   | —    | μA                                                       | +25°C      | 2.21/ |  |  |  |

| DC61b              | 12   | —    | μA                                                       | +85°C      | 3.3V  |  |  |  |

| DC61c              | 13   | —    | μA                                                       | +125°C     |       |  |  |  |

## TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |    |               |       |            |       |                |  |

|-------------------------|-------------------------------------------------------|----|---------------|-------|------------|-------|----------------|--|

| Parameter No. Typ. Max. |                                                       |    | Doze<br>Ratio | Units | Conditions |       |                |  |

| Doze Current (IDC       | oze) <sup>(1)</sup>                                   |    |               |       |            |       |                |  |

| DC73a <sup>(2)</sup>    | 35                                                    |    | 1:2           | mA    | -40°C      | 3.3V  | Fosc = 140 MHz |  |

| DC73g                   | 20                                                    | 30 | 1:128         | mA    | -40 C      |       |                |  |

| DC70a <sup>(2)</sup>    | 35                                                    | _  | 1:2           | mA    | +25°C      | 3.3V  | Fosc = 140 MHz |  |

| DC70g                   | 20                                                    | 30 | 1:128         | mA    | +25 C      |       | FUSC = 140 WHZ |  |

| DC71a <sup>(2)</sup>    | 35                                                    | —  | 1:2           | mA    | 195%       | 2 2)/ |                |  |

| DC71g                   | 20                                                    | 30 | 1:128         | mA    | +85°C      | 3.3V  | Fosc = 140 MHz |  |

| DC72a <sup>(2)</sup>    | 28                                                    | —  | 1:2           | mA    | +125°C     | 3.3V  | Fosc = 120 MHz |  |

| DC72g                   | 15                                                    | 30 | 1:128         | mA    | +125 C     |       | FUSC = 120 MHZ |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

## FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

### TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |           |                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                                |      |      |       |                                  |

|--------------------|-----------|--------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------|------|------|-------|----------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                |                                                       | Min.                                           | Тур. | Max. | Units | Conditions                       |

| TQ10               | TtQH      | TQCK High<br>Time                                            | Synchronous, with prescaler                           | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 |      |      | ns    | Must also meet<br>Parameter TQ15 |

| TQ11               | TtQL      | TQCK Low<br>Time                                             | Synchronous, with prescaler                           | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 | —    | _    | ns    | Must also meet<br>Parameter TQ15 |

| TQ15               | TtQP      | TQCP Input<br>Period                                         | Synchronous, with prescaler                           | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50     | —    | _    | ns    |                                  |

| TQ20               | TCKEXTMRL | Delay from External TQCK<br>Clock Edge to Timer<br>Increment |                                                       | _                                              | 1    | Тсү  | —     |                                  |

Note 1: These parameters are characterized but not tested in manufacturing.

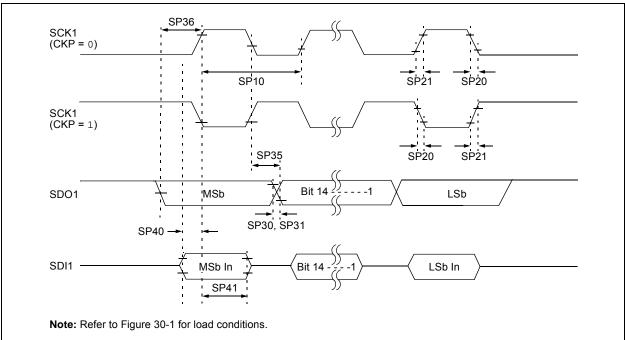

#### FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-43:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                             |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |

|--------------------|---------------------------------------------|-----------------------------------------------|------------------------------------------------------|---------------------|------|-------|-----------------------------|--|

| Param.             | Param. Symbol Characteristic <sup>(1)</sup> |                                               |                                                      | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |  |

| SP10               | FscP                                        | Maximum SCK1 Frequency                        | _                                                    | —                   | 10   | MHz   | (Note 3)                    |  |

| SP20               | TscF                                        | SCK1 Output Fall Time                         | —                                                    | —                   |      | ns    | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                                        | SCK1 Output Rise Time                         | —                                                    | —                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                                        | SDO1 Data Output Fall Time                    | —                                                    | —                   | _    | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                                        | SDO1 Data Output Rise Time                    | —                                                    | _                   | _    | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV                       | SDO1 Data Output Valid after<br>SCK1 Edge     | —                                                    | 6                   | 20   | ns    |                             |  |

| SP36               | TdoV2sc,<br>TdoV2scL                        | SDO1 Data Output Setup to<br>First SCK1 Edge  | 30                                                   | —                   | _    | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL                       | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 30                                                   | —                   | _    | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL                       | Hold Time of SDI1 Data Input to SCK1 Edge     | 30                                                   |                     |      | ns    |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI1 pins.

| DC CHARACTERISTICS  |                                    |                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions:3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |       |      |       |                                   |  |  |

|---------------------|------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-----------------------------------|--|--|

| Param<br>No.        | <sup>1</sup> Symbol Characteristic |                                                     |                                                                                                                                                                                                                                                                                        | Тур.  | Max. | Units | Conditions                        |  |  |

| CTMU Current Source |                                    |                                                     |                                                                                                                                                                                                                                                                                        |       |      |       |                                   |  |  |

| CTMUI1              | Ιουτ1                              | Base Range <sup>(1)</sup>                           | 0.29                                                                                                                                                                                                                                                                                   |       | 0.77 | μA    | CTMUICON<9:8> = 01                |  |  |

| CTMUI2              | IOUT2                              | 10x Range <sup>(1)</sup>                            | 3.85                                                                                                                                                                                                                                                                                   |       | 7.7  | μA    | CTMUICON<9:8> = 10                |  |  |

| CTMUI3              | Ιουτ3                              | 100x Range <sup>(1)</sup>                           | 38.5                                                                                                                                                                                                                                                                                   | _     | 77   | μA    | CTMUICON<9:8> = 11                |  |  |

| CTMUI4              | IOUT4                              | 1000x Range <sup>(1)</sup>                          | 385                                                                                                                                                                                                                                                                                    | _     | 770  | μA    | CTMUICON<9:8> = 00                |  |  |

| CTMUFV1             | VF                                 | Temperature Diode Forward Voltage <sup>(1,2)</sup>  | _                                                                                                                                                                                                                                                                                      | 0.598 | _    | V     | TA = +25°C,<br>CTMUICON<9:8> = 01 |  |  |

|                     |                                    |                                                     | _                                                                                                                                                                                                                                                                                      | 0.658 | _    | V     | TA = +25°C,<br>CTMUICON<9:8> = 10 |  |  |

|                     |                                    |                                                     | _                                                                                                                                                                                                                                                                                      | 0.721 | _    | V     | TA = +25°C,<br>CTMUICON<9:8> = 11 |  |  |

| CTMUFV2             | VFVR                               | Temperature Diode Rate of Change <sup>(1,2,3)</sup> | _                                                                                                                                                                                                                                                                                      | -1.92 | _    | mV/ºC | CTMUICON<9:8> = 01                |  |  |

|                     |                                    |                                                     | _                                                                                                                                                                                                                                                                                      | -1.74 | _    | mV/ºC | CTMUICON<9:8> = 10                |  |  |

|                     |                                    |                                                     |                                                                                                                                                                                                                                                                                        | -1.56 | _    | mV/ºC | CTMUICON<9:8> = 11                |  |  |

## TABLE 30-56: CTMU CURRENT SOURCE SPECIFICATIONS

Note 1: Nominal value at center point of current trim range (CTMUICON<15:10> = 000000).

2: Parameters are characterized but not tested in manufacturing.

**3:** Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC configured for 10-bit mode

- ADC module configured for conversion speed of 500 ksps

- All PMDx bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL