# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 70 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp202-i-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

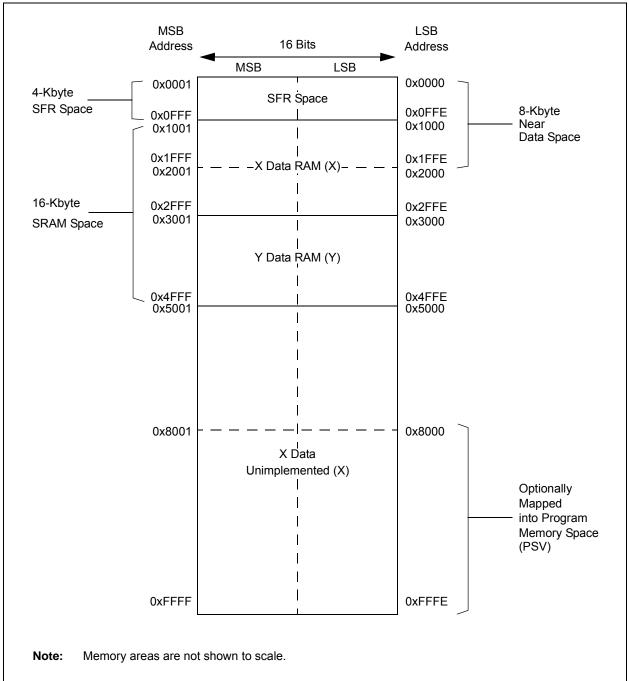

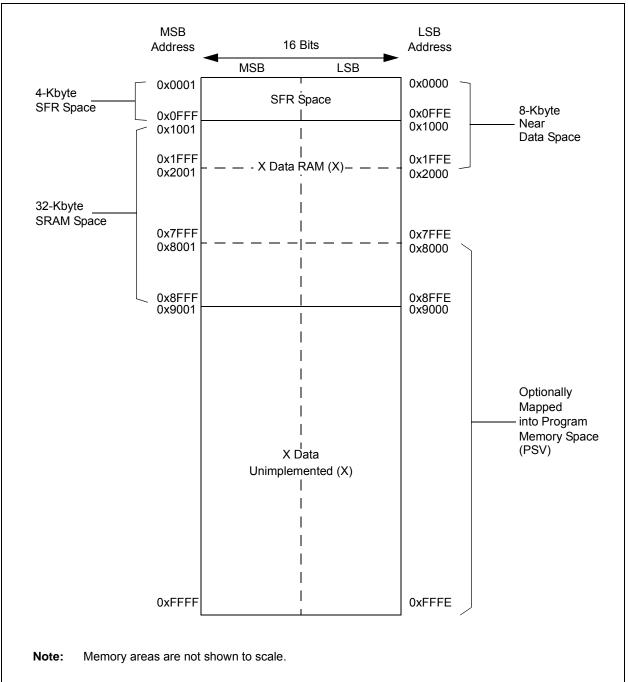

### FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

| TABLE 4   | -12:                                                                           | PWM RI                     | EGISTE                                                                               | R MAP  | FOR de | sPIC33E | PXXXN  | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE | S ONI | _Y    |       |       |               |

|-----------|--------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------|--------|--------|---------|--------|----------|----------|---------|-------|--------|--------|-------|-------|-------|-------|---------------|

| File Name | Addr.                                                                          | Bit 15                     | Bit 14                                                                               | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| PTCON     | 0C00                                                                           | PTEN                       | PTEN - PTSIDL SESTAT SEIEN EIPU SYNCPOL SYNCOEN SYNCEN SYNCSRC<2:0> SEVTPS<3:0> 0000 |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

| PTCON2    | 0C02                                                                           | _                          | PCLKDIV<2:0> 000                                                                     |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

| PTPER     | 0C04                                                                           | PTPER<15:0> 00F8           |                                                                                      |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

| SEVTCMP   | 0C06                                                                           |                            |                                                                                      |        |        |         |        |          | SEVTCMP< | 5:0>    |       |        |        |       |       |       |       | 0000          |

| MDC       | 0C0A                                                                           |                            |                                                                                      |        |        |         |        |          | MDC<15:  | )>      |       |        |        |       |       |       |       | 0000          |

| CHOP      | 0C1A                                                                           | CHPCLKEN CHOPCLK<9:0> 0000 |                                                                                      |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

| PWMKEY    | 0C1E                                                                           | PWMKEY<15:0> 0000          |                                                                                      |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

| Legend: - | Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                            |                                                                                      |        |        |         |        |          |          |         |       |        |        |       |       |       |       |               |

#### TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |                                           |                                                       |          | I OIT U |        |          |          |        | 1102-  |        |       |          |       |       |               |

|-----------|-------|---------|--------|-------------------------------------------|-------------------------------------------------------|----------|---------|--------|----------|----------|--------|--------|--------|-------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13                                    | Bit 12                                                | Bit 11   | Bit 10  | Bit 9  | Bit 8    | Bit 7    | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT                                   | FLTIEN                                                | CLIEN    | TRGIEN  | ITB    | MDCS     | DTC<     | :1:0>  | DTCP   | _      | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON1    | 0C22  | PENH    | PENL   | POLH                                      | POLL                                                  | PMOD     | <1:0>   | OVRENH | OVRENL   | OVRDA    | T<1:0> | FLTDA  | T<1:0> | CLDA  | T<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON1   | 0C24  | _       |        | (                                         | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |          |         |        |          |          |        | D<1:0> | 0000   |       |          |       |       |               |

| PDC1      | 0C26  |         |        |                                           | PDC1<15:0>                                            |          |         |        |          |          |        | FFF8   |        |       |          |       |       |               |

| PHASE1    | 0C28  |         |        |                                           | PHASE1<15:0>                                          |          |         |        |          |          |        | 0000   |        |       |          |       |       |               |

| DTR1      | 0C2A  | _       | _      |                                           |                                                       |          |         |        |          | DTR1<13: | 0>     |        |        |       |          |       |       | 0000          |

| ALTDTR1   | 0C2C  | _       | _      |                                           |                                                       |          |         |        | А        | LTDTR1<1 | 3:0>   |        |        |       |          |       |       | 0000          |

| TRIG1     | 0C32  |         |        |                                           |                                                       |          |         |        | TRGCMP<1 | 5:0>     |        |        |        |       |          |       |       | 0000          |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>                                    |                                                       | _        | _       | _      | _        | _        | _      |        |        | TRG   | STRT<5:0 | >     |       | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR                                       | PLF                                                   | FLTLEBEN | CLLEBEN | _      | _        | _        | _      | BCH    | BCL    | BPHH  | BPHL     | BPLH  | BPLL  | 0000          |

| LEBDLY1   | 0C3C  | _       | _      | —                                         | —                                                     |          |         |        |          |          | LEB<11 | :0>    |        |       |          |       |       | 0000          |

| AUXCON1   | 0C3E  | —       | —      | BLANKSEL<3:0> CHOPSEL<3:0> CHOPHEN CHOPLE |                                                       |          |         |        |          | CHOPLEN  | 0000   |        |        |       |          |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN $(C1CTRL1<0>) = 0$ OR 1 FOR dsp |       |         |                                                 |         |         |                          |         |                                              |        | PIC33E               | PXXXIV    | IC/GP5 |         | ICES O           | NLY      |          |        |               |

|-------------------------------------------------------------------------|-------|---------|-------------------------------------------------|---------|---------|--------------------------|---------|----------------------------------------------|--------|----------------------|-----------|--------|---------|------------------|----------|----------|--------|---------------|

| File Name                                                               | Addr. | Bit 15  | Bit 14                                          | Bit 13  | Bit 12  | Bit 11                   | Bit 10  | Bit 9                                        | Bit 8  | Bit 7                | Bit 6     | Bit 5  | Bit 4   | Bit 3            | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1                                                                 | 0400  | _       | —                                               | CSIDL   | ABAT    | CANCKS                   | R       | EQOP<2:0                                     | >      | OPM                  | /IODE<2:0 | >      | —       | CANCAP           | —        | —        | WIN    | 0480          |

| C1CTRL2                                                                 | 0402  | _       | _                                               | —       | _       | _                        | _       | —                                            | _      | —                    | _         | _      |         | D                | NCNT<4:0 | >        |        | 0000          |

| C1VEC                                                                   | 0404  | _       | —                                               | —       |         | FILHIT<4:0>              |         |                                              | —      | ICODE<6:0>           |           |        |         |                  | 0040     |          |        |               |

| C1FCTRL                                                                 | 0406  | C       | DMABS<2:0                                       | >       |         | _                        | —       | —                                            | _      | _                    | _         | _      |         |                  | FSA<4:0> |          |        | 0000          |

| C1FIFO                                                                  | 0408  |         | —                                               |         |         | FBP<5:0>                 |         |                                              | —      | _                    | FNRB<5:0> |        |         |                  |          | 0000     |        |               |

| C1INTF                                                                  | 040A  |         | —                                               | TXBO    | TXBP    | RXBP                     | TXWAR   | RXWAR                                        | EWARN  | IVRIF                | WAKIF     | ERRIF  | _       | FIFOIF           | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE                                                                  | 040C  |         | —                                               | —       |         | _                        | —       | —                                            | _      | IVRIE                | WAKIE     | ERRIE  | _       | FIFOIE           | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC                                                                    | 040E  |         |                                                 |         | TERRCN  | T<7:0>                   |         |                                              |        | RERRCNT<7:0>         |           |        |         |                  |          | 0000     |        |               |

| C1CFG1                                                                  | 0410  | _       | _                                               | _       | _       | _                        | _       | _                                            | _      | SJW<1                | :0>       |        |         | BRP              | <5:0>    |          |        | 0000          |

| C1CFG2                                                                  | 0412  | _       | WAKFIL                                          | _       | _       | _                        | SI      | =G2PH<2:(                                    | )>     | SEG2PHTS             | SAM       | S      | EG1PH<2 | :0>              | P        | RSEG<2:0 | >      | 0000          |

| C1FEN1                                                                  | 0414  | FLTEN15 | FLTEN14                                         | FLTEN13 | FLTEN12 | FLTEN11                  | FLTEN10 | FLTEN9                                       | FLTEN8 | FLTEN7               | FLTEN6    | FLTEN5 | FLTEN4  | FLTEN3           | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1                                                              | 0418  | F7MSł   | <<1:0>                                          | F6MSł   | <<1:0>  | 0> F5MSK<1:0> F4MSK<1:0> |         |                                              |        | F3MSK<1:0> F2MSK<1:0 |           |        | K<1:0>  | <1:0> F1MSK<1:0> |          |          | <<1:0> | 0000          |

| C1FMSKSEL2                                                              | 041A  | F15MS   | F15MSK<1:0> F14MSK<1:0> F13MSK<1:0> F12MSK<1:0> |         |         | K<1:0>                   | F11MSK  | F11MSK<1:0> F10MSK<1:0> F9MSK<1:0> F8MSK<1:0 |        |                      | <<1:0>    | 0000   |         |                  |          |          |        |               |

#### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10                                                                    | Bit 9   | Bit 8         | Bit 7        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|---------|---------|---------|---------|---------------------------------------------------------------------------|---------|---------------|--------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         |         |         |         |         |                                                                           | S       | ee definition | when WIN     | = x     |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10                                                                   | RXFUL9  | RXFUL8        | RXFUL7       | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26                                                                   | RXFUL25 | RXFUL24       | RXFUL23      | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10                                                                   | RXOVF9  | RXOVF8        | RXOVF7       | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26                                                                   | RXOVF25 | RXOVF24       | RXOVF23      | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1  | TXLARB1 | TXERR1  | TXREQ1  | RTREN1                                                                    | TX1PF   | RI<1:0>       | TXEN0        | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3  | TXLARB3 | TXERR3  | TXREQ3  | RTREN3                                                                    | TX3PF   | RI<1:0>       | TXEN2        | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5  | TXLARB5 | TXERR5  | TXREQ5  | RTREN5                                                                    | TX5PF   | RI<1:0>       | TXEN4        | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7  | TXLARB7 | TXERR7  | TXREQ7  | RTREN7 TX7PRI<1:0> TXEN6 TXABAT6 TXLARB6 TXERR6 TXREQ6 RTREN6 TX6PRI<1:0> |         |               |              |         | RI<1:0> | xxxx    |         |         |         |         |               |

| C1RXD     | 0440          |         |         |         |         |         |                                                                           | E       | CAN1 Rece     | eive Data Wo | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         |         |         |         |         |                                                                           | E       | CAN1 Trans    | smit Data Wo | ord     |         |         |         |         |         |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

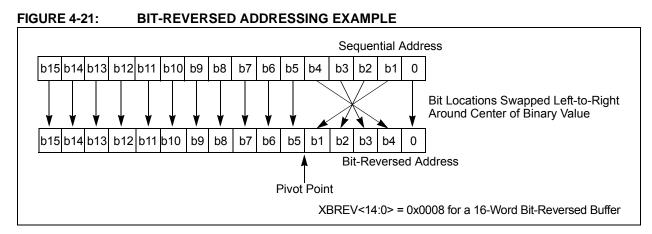

#### TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |  |  |  |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|--|--|--|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |  |  |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |  |  |  |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |  |  |  |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |  |  |  |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |  |  |  |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |  |  |  |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |  |  |  |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |  |  |  |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |  |  |  |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |  |  |  |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |  |  |  |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |  |  |  |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |  |  |  |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |  |  |  |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |  |  |  |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |  |  |  |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |  |  |  |

#### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 3 SPI1MD: SPI1 Module Disable bit 1 = SPI1 module is disabled

- 0 = SPI1 module is enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: ECAN1 Module Disable bit<sup>(2)</sup> 1 = ECAN1 module is disabled 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit 1 = ADC1 module is disabled 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

#### 13.2 Timer Control Registers

| R/W-0         | U-0                                   | R/W-0                              | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |

|---------------|---------------------------------------|------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| TON           |                                       | TSIDL                              | —              | _                |                 |                 | _     |  |  |  |

| bit 15        |                                       |                                    |                |                  |                 |                 | bit 8 |  |  |  |

|               |                                       |                                    |                |                  |                 |                 |       |  |  |  |

| U-0           | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |

| _             | TGATE                                 | TCKPS1                             | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |

| bit 7         |                                       |                                    |                |                  |                 |                 | bit ( |  |  |  |

| <u> </u>      |                                       |                                    |                |                  |                 |                 |       |  |  |  |

| Legend:       | - 1-:4                                |                                    |                | II II.           |                 |                 |       |  |  |  |

| R = Readable  |                                       | W = Writable                       |                | -                | nented bit, rea |                 |       |  |  |  |

| -n = Value at | PUR                                   | '1' = Bit is set                   |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |

| bit 15        | TON: Timerx                           | On hit                             |                |                  |                 |                 |       |  |  |  |

|               | When T32 = 2                          |                                    |                |                  |                 |                 |       |  |  |  |

|               | 1 = Starts 32-                        | bit Timerx/y                       |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 32-                         |                                    |                |                  |                 |                 |       |  |  |  |

|               | <u>When T32 = 0</u><br>1 = Starts 16- |                                    |                |                  |                 |                 |       |  |  |  |

|               | 0 = Stops 16-                         |                                    |                |                  |                 |                 |       |  |  |  |

| bit 14        | Unimplemented: Read as '0'            |                                    |                |                  |                 |                 |       |  |  |  |

| bit 13        | TSIDL: Timer                          | x Stop in Idle M                   | lode bit       |                  |                 |                 |       |  |  |  |

|               |                                       | ues module op                      |                |                  | dle mode        |                 |       |  |  |  |

|               |                                       | s module opera                     |                | ode              |                 |                 |       |  |  |  |

| bit 12-7      | -                                     | ted: Read as '                     |                |                  |                 |                 |       |  |  |  |

| bit 6         |                                       | erx Gated Time                     | Accumulation   | Enable bit       |                 |                 |       |  |  |  |

|               | When TCS =<br>This bit is igno        |                                    |                |                  |                 |                 |       |  |  |  |

|               | When TCS =                            |                                    |                |                  |                 |                 |       |  |  |  |

|               | 1 = Gated tim                         | e accumulatior                     |                |                  |                 |                 |       |  |  |  |

|               |                                       | e accumulation                     |                |                  |                 |                 |       |  |  |  |

| bit 5-4       |                                       | : Timerx Input                     | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |

|               | 11 = 1:256<br>10 = 1:64               |                                    |                |                  |                 |                 |       |  |  |  |

|               | 01 = 1:8                              |                                    |                |                  |                 |                 |       |  |  |  |

|               | 00 = 1:1                              |                                    |                |                  |                 |                 |       |  |  |  |

| bit 3         | T32: 32-Bit Ti                        | mer Mode Sele                      | ect bit        |                  |                 |                 |       |  |  |  |

|               |                                       | nd Timery form<br>nd Timery act as |                |                  |                 |                 |       |  |  |  |

| bit 2         | Unimplemen                            | ted: Read as '                     | )'             |                  |                 |                 |       |  |  |  |

| bit 1         | TCS: Timerx                           | Clock Source S                     | elect bit      |                  |                 |                 |       |  |  |  |

|               | 1 = External c<br>0 = Internal cl     | clock is from pir<br>lock (FP)     | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |

| bit 0         | Unimplomon                            | ted: Read as '                     | ı'             |                  |                 |                 |       |  |  |  |

### REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

| ; FLT32 pin must be pulled low externally in order to clear and disable the fault<br>; Writing to FCLCON1 register requires unlock sequence |                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre>                                    | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |  |  |  |  |  |  |

| -                                                                                                                                           | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |  |  |  |  |  |  |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>                                     | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |  |  |  |  |  |  |

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|-------------------------------------------------------------------------|-------|-------|-------|--------------|------------------|----------|-------|

|                                                                         |       |       | TRGC  | MP<15:8>     |                  |          |       |

| bit 15                                                                  |       |       |       |              |                  |          | bit 8 |

|                                                                         |       |       |       |              |                  |          |       |

| R/W-0                                                                   | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                                                         |       |       | TRGC  | MP<7:0>      |                  |          |       |

| bit 7                                                                   |       |       |       |              |                  |          | bit 0 |

| Legend:                                                                 |       |       |       |              |                  |          |       |

| R = Readable bit W = Writable bit                                       |       |       | oit   | U = Unimplem | nented bit, read | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkn |       |       | nown  |              |                  |          |       |

#### REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits <sup>(1)</sup>                     |

|---------|-----------------------------------------------------------------------------------------------------|

|         | 11111 = Open; use this selection with CTMU capacitive and time measurement                          |

|         | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP) |

|         | 11101 = Reserved                                                                                    |

|         | 11100 = Reserved                                                                                    |

|         | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>      |

|         | 11010 =  Channel 0 positive input is the output of OA3/AN0 <sup>(2)</sup>                           |

|         | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                            |

|         | 10110 = Reserved                                                                                    |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 10000 = Reserved                                                                                    |

|         | 01111 = Channel 0 positive input is AN15 <sup>(1,3)</sup>                                           |

|         | 01110 = Channel 0 positive input is AN14 <sup>(1,3)</sup>                                           |

|         | 01101 = Channel 0 positive input is AN13 <sup>(1,3)</sup>                                           |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 00010 = Channel 0 positive input is $AN2^{(1,3)}$                                                   |

|         | 00001 = Channel 0 positive input is $AN1^{(1,3)}$                                                   |

|         | 00000 = Channel 0 positive input is AN0 <sup>(1,3)</sup>                                            |

|         |                                                                                                     |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

#### 26.1 Overview

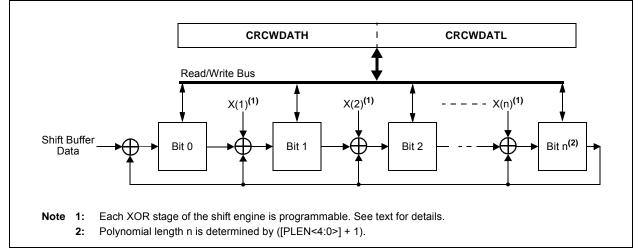

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation; functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit equation and the other a 32-bit equation:

$$\begin{array}{c} x16+x12+x5+1\\ \text{and}\\ x32+x26+x23+x22+x16+x12+x11+x10+x8+x7\\ +x5+x4+x2+x+1 \end{array}$$

To program these polynomials into the CRC generator, set the register bits as shown in Table 26-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCxOR register.

## TABLE 26-1:CRC SETUP EXAMPLES FOR16 AND 32-BIT POLYNOMIAL

| CRC Control | Bit Values             |                        |  |  |  |  |

|-------------|------------------------|------------------------|--|--|--|--|

| Bits        | 16-bit<br>Polynomial   | 32-bit<br>Polynomial   |  |  |  |  |

| PLEN<4:0>   | 01111                  | 11111                  |  |  |  |  |

| X<31:16>    | 0000 0000<br>0000 000x | 0000 0100<br>1100 0001 |  |  |  |  |

| X<15:0>     | 0001 0000<br>0010 000x | 0001 1101<br>1011 011x |  |  |  |  |

#### 26.2 Programmable CRC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 26.2.1 KEY RESOURCES

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                                                          | U-0                                         | U-0              | R/W-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|--------------------------------------------------------------|---------------------------------------------|------------------|-------------------------|------------------|------------------|-----------------|---------|

| _                                                            | —                                           | —                | DWIDTH4 DWIDTH3 DWIDTH2 |                  | DWIDTH2          | DWIDTH1         | DWIDTH0 |

| bit 15                                                       |                                             |                  |                         |                  |                  |                 | bit 8   |

|                                                              |                                             |                  |                         |                  |                  |                 |         |

| U-0                                                          | U-0                                         | U-0              | R/W-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| —                                                            | – – – PLEN4 PLEN3 PLEN2                     |                  |                         | PLEN2            | PLEN1            | PLEN0           |         |

| bit 7                                                        |                                             |                  |                         |                  |                  |                 | bit 0   |

|                                                              |                                             |                  |                         |                  |                  |                 |         |

| Legend:                                                      |                                             |                  |                         |                  |                  |                 |         |

| R = Readable                                                 | e bit                                       | W = Writable     | bit                     | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at                                                | POR                                         | '1' = Bit is set |                         | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                                                              |                                             |                  |                         |                  |                  |                 |         |

| bit 15-13                                                    | Unimplemen                                  | ted: Read as '   | 0'                      |                  |                  |                 |         |

| bit 12-8                                                     | it 12-8 DWIDTH<4:0>: Data Width Select bits |                  |                         |                  |                  |                 |         |

| These bits set the width of the data word (DWIDTH<4:0> + 1). |                                             |                  |                         |                  |                  |                 |         |

| bit 7-5                                                      | -5 Unimplemented: Read as '0'               |                  |                         |                  |                  |                 |         |

|                                                              |                                             |                  |                         |                  |                  |                 |         |

#### REGISTER 26-2: CRCCON2: CRC CONTROL REGISTER 2

bit 4-0 **PLEN<4:0>:** Polynomial Length Select bits

These bits set the length of the polynomial (Polynomial Length = PLEN<4:0> + 1).

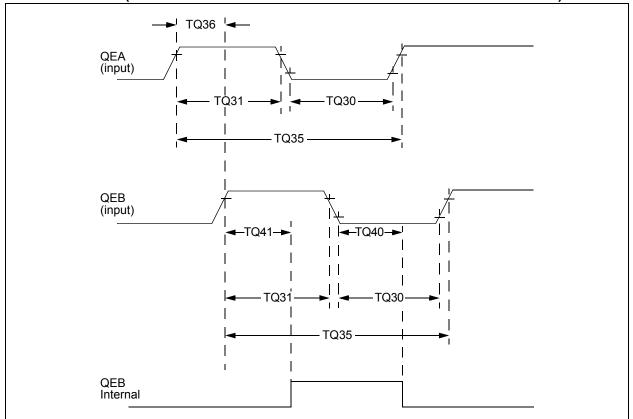

#### FIGURE 30-12: QEA/QEB INPUT CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-31: QUADRATURE DECODER TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                    | Standard Ope<br>(unless other<br>Operating tem | wise state | ed)<br>-40°C ≤ | <b>3.0V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended |

|--------------------|--------|----------------------------------------------------|------------------------------------------------|------------|----------------|----------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                      | Typ. <sup>(2)</sup>                            | Max.       | Units          | Conditions                                                                             |

| TQ30               | TQUL   | Quadrature Input Low Time                          | 6 Tcy                                          |            | ns             |                                                                                        |

| TQ31               | TQUH   | Quadrature Input High Time                         | 6 Tcy                                          | —          | ns             |                                                                                        |

| TQ35               | TQUIN  | Quadrature Input Period                            | 12 TCY                                         | _          | ns             |                                                                                        |

| TQ36               | TQUP   | Quadrature Phase Period                            | 3 TCY                                          | —          | ns             |                                                                                        |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter  | 3 * N * Tcy                                    | —          | ns             | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b>                                |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter | 3 * N * Tcy                                    | —          | ns             | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 3)</b>                                |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: N = Index Channel Digital Filter Clock Divide Select bits. Refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "*dsPIC33/PIC24 Family Reference Manual*". Please see the Microchip web site for the latest family reference manual sections.

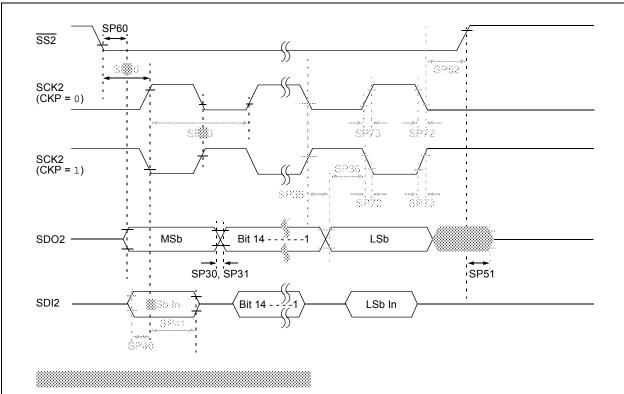

#### FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## TABLE 30-47:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | Standard Op<br>(unless othe<br>Operating te | erwise st           | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------|---------------------|------------------------|----------|-----------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                        | Typ. <sup>(2)</sup> | Max.                   | Units    | Conditions                                                      |

| SP70               | FscP                  | Maximum SCK1 Input Frequency                 | —                                           | —                   | 15                     | MHz      | (Note 3)                                                        |

| SP72               | TscF                  | SCK1 Input Fall Time                         | —                                           | —                   | _                      | ns       | See Parameter DO32 (Note 4)                                     |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                           | —                   | _                      | ns       | See Parameter DO31 (Note 4)                                     |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | —                                           | _                   | _                      | ns       | See Parameter DO32 (Note 4)                                     |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                           | —                   | _                      | ns       | See Parameter DO31 (Note 4)                                     |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                           | 6                   | 20                     | ns       |                                                                 |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                          | —                   | _                      | ns       |                                                                 |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                          | —                   | _                      | ns       |                                                                 |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                          | —                   | _                      | ns       |                                                                 |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                         | —                   | _                      | ns       |                                                                 |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                          | —                   | 50                     | ns       | (Note 4)                                                        |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1                                          | 1.5 Tcy + 40                                | —                   |                        | ns       | (Note 4)                                                        |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| AC CHARACTERISTICS                        |        |                           |              | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature-40°C $\leq$ TA $\leq$ +150°C |          |                   |                                                  |  |

|-------------------------------------------|--------|---------------------------|--------------|------------------------------------------------------------------------------------------------------------------------|----------|-------------------|--------------------------------------------------|--|

| Param<br>No.                              | Symbol | Characteristic            | Min Typ Max  |                                                                                                                        | Units    | Conditions        |                                                  |  |

| ADC Accuracy (12-Bit Mode) <sup>(1)</sup> |        |                           |              |                                                                                                                        |          |                   |                                                  |  |

| HAD20a                                    | Nr     | Resolution <sup>(3)</sup> | 12 Data Bits |                                                                                                                        | bits     |                   |                                                  |  |

| HAD21a                                    | INL    | Integral Nonlinearity     | -5.5         | _                                                                                                                      | 5.5      | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD22a                                    | DNL    | Differential Nonlinearity | -1           | _                                                                                                                      | 1        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD23a                                    | Gerr   | Gain Error                | -10          |                                                                                                                        | 10       | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| HAD24a                                    | EOFF   | Offset Error              | -5           | —                                                                                                                      | 5        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

|                                           |        | Dynamic I                 | Performa     | nce (12-                                                                                                               | Bit Mode | e) <sup>(2)</sup> |                                                  |  |

| HAD33a                                    | Fnyq   | Input Signal Bandwidth    | _            | _                                                                                                                      | 200      | kHz               |                                                  |  |

#### TABLE 31-12: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

#### TABLE 31-13: ADC MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS |        |                           |             | otherwi   | ise stated           | d)                | : <b>3.0V to 3.6V</b><br>TA ≤ +150°C             |

|--------------------|--------|---------------------------|-------------|-----------|----------------------|-------------------|--------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic            | Min Typ Max |           | Units                | Conditions        |                                                  |

|                    |        | ADC A                     | ccuracy     | (10-Bit I | Mode) <sup>(1)</sup> |                   |                                                  |

| HAD20b             | Nr     | Resolution <sup>(3)</sup> | 10          | ) Data B  | its                  | bits              |                                                  |

| HAD21b             | INL    | Integral Nonlinearity     | -1.5        | _         | 1.5                  | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD22b             | DNL    | Differential Nonlinearity | -0.25       | -         | 0.25                 | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD23b             | Gerr   | Gain Error                | -2.5        |           | 2.5                  | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| HAD24b             | EOFF   | Offset Error              | -1.25       | _         | 1.25                 | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

|                    |        | Dynamic P                 | erforma     | nce (10-  | Bit Mode             | e) <sup>(2)</sup> |                                                  |

| HAD33b             | Fnyq   | Input Signal Bandwidth    | _           | _         | 400                  | kHz               |                                                  |

Note 1: These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

#### 33.0 PACKAGING INFORMATION

#### 33.1 Package Marking Information

#### 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

#### Example

#### Example

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>of or customer-specific information.                                                                                                                                                                                              |

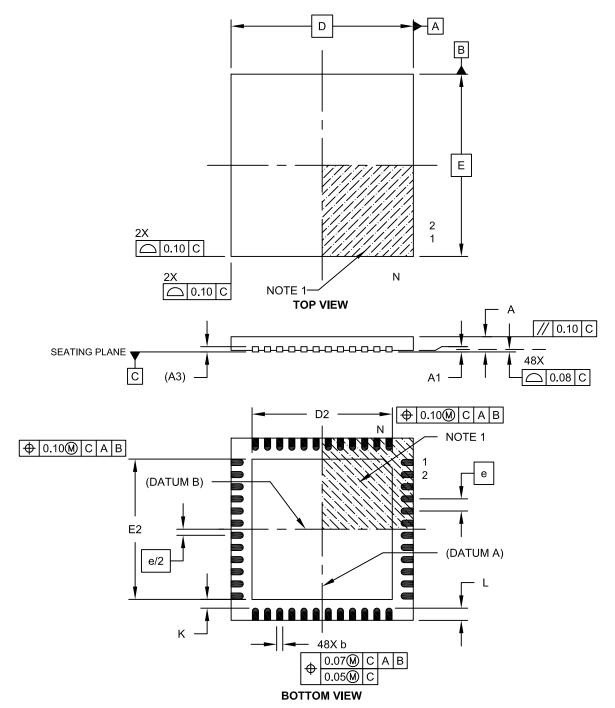

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2