Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp202t-i-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

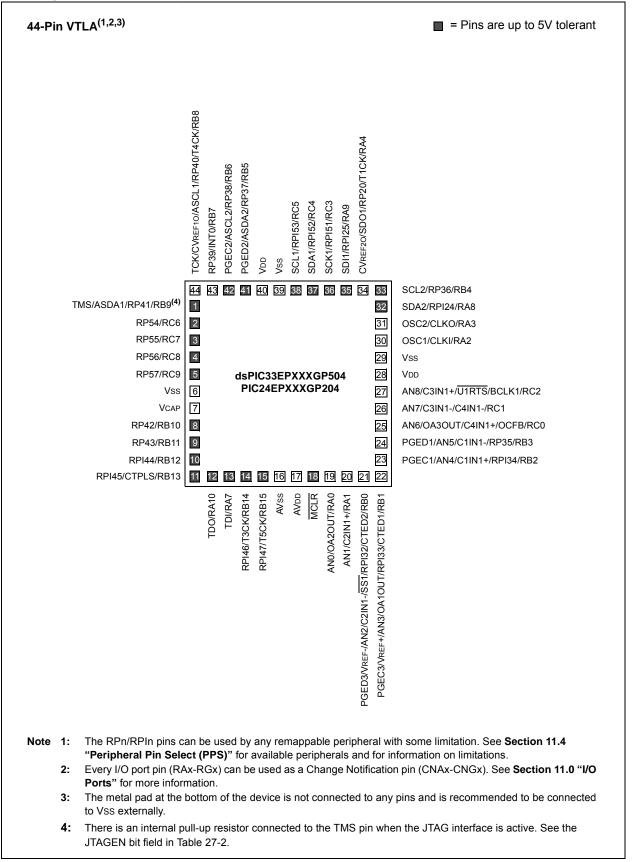

#### **Pin Diagrams (Continued)**

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

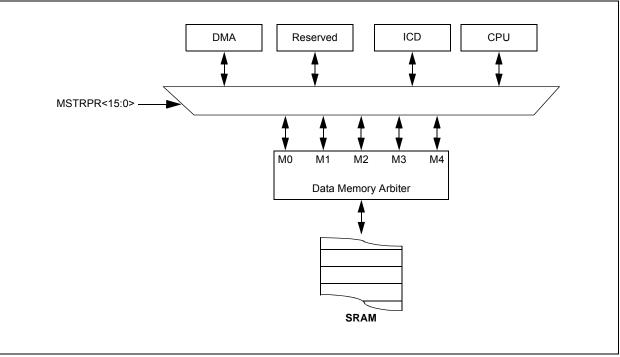

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

## FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

#### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           | 101 0101                                         | —                | _              |

| 010 1001                                         | I/O              | RP41           | 101 0110                                         | —                | —              |

| 010 1010                                         | I/O              | RP42           | 101 0111                                         | —                | —              |

| 010 1011                                         | I/O              | RP43           | 101 1000                                         |                  | —              |

| 010 1100                                         | I                | RPI44          | 101 1001                                         |                  | —              |

| 101 1010                                         | —                | _              | 110 1101                                         | —                | _              |

| 101 1011                                         | —                | —              | 110 1110                                         |                  | —              |

| 101 1100                                         | —                | —              | 110 1111                                         |                  | —              |

| 101 1101                                         | —                | _              | 111 0000                                         | —                | _              |

| 101 1110                                         | 1                | RPI94          | 111 0001                                         | —                | _              |

| 101 1111                                         | I                | RP195          | 111 0010                                         |                  | —              |

| 110 0000                                         | I                | RPI96          | 111 0011                                         | —                | —              |

| 110 0001                                         | I/O              | RP97           | 111 0100                                         |                  | —              |

| 110 0010                                         | —                | —              | 111 0101                                         |                  | —              |

| 110 0011                                         | —                | —              | 111 0110                                         | I/O              | RP118          |

| 110 0100                                         | —                | —              | 111 0111                                         | Ι                | RPI119         |

| 110 0101                                         | —                | —              | 111 1000                                         | I/O              | RP120          |

| 110 0110                                         | _                |                | 111 1001                                         | I                | RPI121         |

| 110 0111                                         |                  |                | 111 1010                                         | —                |                |

| 110 1000                                         | —                | _              | 111 1011                                         | —                | _              |

| 110 1001                                         | —                |                | 111 1100                                         | —                |                |

| 110 1010                                         |                  |                | 111 1101                                         | —                |                |

| 110 1011                                         | —                | _              | 111 1110                                         | —                |                |

| 110 1100                                         | —                | _              | 111 1111                                         | _                |                |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

## 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

NOTES:

#### 12.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

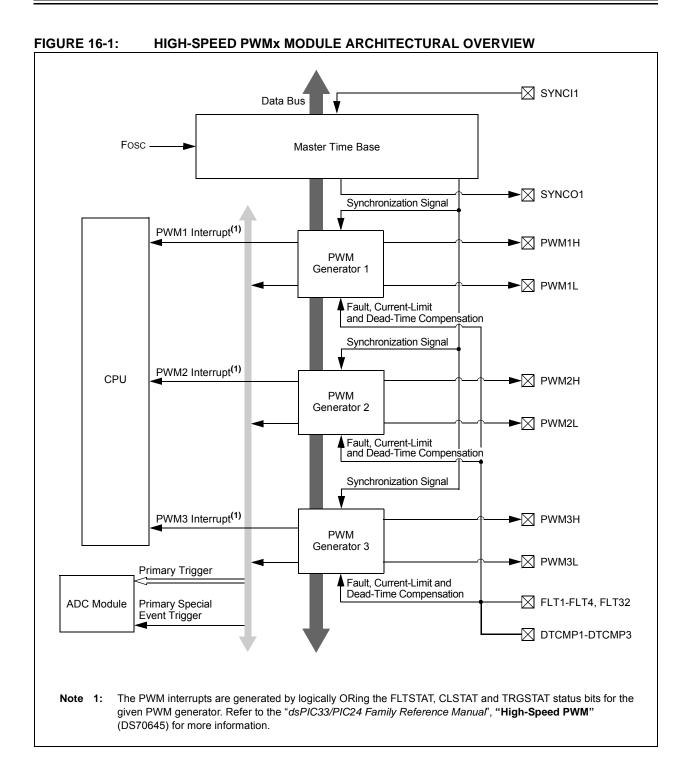

## 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

## 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

#### REGISTER 16-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                   |       |                  | PDC   | <15:8>                                  |       |       |       |

| bit 15            |       |                  |       |                                         |       |       | bit 8 |

|                   |       |                  |       |                                         |       |       |       |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                   |       |                  | PDC   | x<7:0>                                  |       |       |       |

| bit 7             |       |                  |       |                                         |       |       | bit 0 |

|                   |       |                  |       |                                         |       |       |       |

| Legend:           |       |                  |       |                                         |       |       |       |

| R = Readable      | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 **PDCx<15:0>:** PWMx Generator # Duty Cycle Value bits

#### REGISTER 16-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | PHAS  | Ex<15:8>                                |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | PHAS  | SEx<7:0>                                |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | pit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

Note 1: If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

| U-0             | U-0   | R/W-0            | R/W-0      | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |  |  |

|-----------------|-------|------------------|------------|-----------------------------------------|-----------------|----------|-------|--|--|--|--|

| —               | —     |                  | DTRx<13:8> |                                         |                 |          |       |  |  |  |  |

| bit 15          |       |                  |            |                                         |                 |          | bit 8 |  |  |  |  |

|                 |       |                  |            |                                         |                 |          |       |  |  |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0      | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |  |  |

|                 |       |                  | DTR        | x<7:0>                                  |                 |          |       |  |  |  |  |

| bit 7           |       |                  |            |                                         |                 |          | bit 0 |  |  |  |  |

|                 |       |                  |            |                                         |                 |          |       |  |  |  |  |

| Legend:         |       |                  |            |                                         |                 |          |       |  |  |  |  |

| R = Readable    | bit   | W = Writable b   | bit        | U = Unimpler                            | nented bit, rea | d as '0' |       |  |  |  |  |

| -n = Value at F | POR   | '1' = Bit is set |            | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |  |  |  |

## REGISTER 16-10: DTRx: PWMx DEAD-TIME REGISTER

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-11: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0             | U-0   | R/W-0            | R/W-0                                  | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-----------------|-------|------------------|----------------------------------------|-----------------------------------------|-------|-------|-------|--|--|--|

| _               | _     |                  | ALTDTRx<13:8>                          |                                         |       |       |       |  |  |  |

| bit 15          |       |                  | bit 8                                  |                                         |       |       |       |  |  |  |

|                 |       |                  |                                        |                                         |       |       |       |  |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                  | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                 |       |                  | ALTDT                                  | Rx<7:0>                                 |       |       |       |  |  |  |

| bit 7           |       |                  |                                        |                                         |       |       | bit 0 |  |  |  |

|                 |       |                  |                                        |                                         |       |       |       |  |  |  |

| Legend:         |       |                  |                                        |                                         |       |       |       |  |  |  |

| R = Readable    | bit   | W = Writable b   | bit U = Unimplemented bit, read as '0' |                                         |       |       |       |  |  |  |

| -n = Value at F | POR   | '1' = Bit is set |                                        | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                                                                      |       |                  | TRGC  | MP<15:8>                                |       |       |       |

| bit 15                                                               |       |                  |       |                                         |       |       | bit 8 |

|                                                                      |       |                  |       |                                         |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |                  | TRGC  | MP<7:0>                                 |       |       |       |

| bit 7                                                                |       |                  |       |                                         |       |       | bit 0 |

| Legend:                                                              |       |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       | d as '0'                                |       |       |       |

| -n = Value at P                                                      | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

## REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|              | ( •                                                            | ,_, ., ., .,                     | -,-,-,                         |                  |                  |                 |                 |  |  |  |  |

|--------------|----------------------------------------------------------------|----------------------------------|--------------------------------|------------------|------------------|-----------------|-----------------|--|--|--|--|

| R/W-0        | R-0                                                            | R-0                              | R-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENn        | TXABTn                                                         | TXLARBn                          | TXERRn                         | TXREQn           | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |  |

| bit 15       |                                                                |                                  |                                |                  |                  |                 | bit 8           |  |  |  |  |

| R/W-0        | R-0                                                            | R-0                              | R-0                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |

| TXENm        | TXABTm <sup>(1)</sup>                                          | TXLARBm <sup>(1)</sup>           | TXERRm <sup>(1)</sup>          | TXREQm           | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |  |

| bit 7        |                                                                |                                  | •                              |                  |                  |                 | bit 0           |  |  |  |  |

| Legend:      |                                                                |                                  |                                |                  |                  |                 |                 |  |  |  |  |

| R = Readab   | le bit                                                         | W = Writable                     | bit                            | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |  |

| -n = Value a | t POR                                                          | '1' = Bit is set                 |                                | '0' = Bit is cle | ared             | x = Bit is unki | nown            |  |  |  |  |

| bit 15-8     | See Definitio                                                  | n for bits<7:0>,                 | Controls Buffe                 | ar n             |                  |                 |                 |  |  |  |  |

| bit 7        |                                                                | RX Buffer Sele                   |                                | 51 TI            |                  |                 |                 |  |  |  |  |

|              |                                                                | Ren is a transm                  |                                |                  |                  |                 |                 |  |  |  |  |

|              |                                                                | RBn is a receive                 |                                |                  |                  |                 |                 |  |  |  |  |

| bit 6        | TXABTm: M                                                      | essage Aborteo                   | d bit <sup>(1)</sup>           |                  |                  |                 |                 |  |  |  |  |

|              |                                                                | 1 = Message was aborted          |                                |                  |                  |                 |                 |  |  |  |  |

|              | 0 = Message                                                    | completed tran                   | nsmission succ                 | essfully         |                  |                 |                 |  |  |  |  |

| bit 5        | TXLARBm: N                                                     | Message Lost A                   | Arbitration bit <sup>(1)</sup> | )                |                  |                 |                 |  |  |  |  |

|              |                                                                | lost arbitration did not lose ar |                                |                  |                  |                 |                 |  |  |  |  |

| bit 4        | •                                                              | ror Detected D                   |                                | •                |                  |                 |                 |  |  |  |  |

|              |                                                                | or occurred wh                   |                                |                  | sent             |                 |                 |  |  |  |  |

|              | 0 = A bus error did not occur while the message was being sent |                                  |                                |                  |                  |                 |                 |  |  |  |  |

| bit 3        | TXREQm: M                                                      | essage Send R                    | Request bit                    |                  |                  |                 |                 |  |  |  |  |

|              | sent                                                           |                                  | -                              |                  | ally clears wher | n the message   | is successfully |  |  |  |  |

|              | •                                                              | the bit to '0' wh                | •                              | •                | abort            |                 |                 |  |  |  |  |

| bit 2        |                                                                | uto-Remote Tra                   |                                |                  |                  |                 |                 |  |  |  |  |

|              |                                                                | emote transmit<br>emote transmit |                                |                  |                  |                 |                 |  |  |  |  |

| bit 1-0      | TXmPRI<1:0                                                     | >: Message Tra                   | ansmission Pri                 | ority bits       |                  |                 |                 |  |  |  |  |

|              | -                                                              | message prior                    | •                              |                  |                  |                 |                 |  |  |  |  |

|              | 0                                                              | ermediate mes                    |                                |                  |                  |                 |                 |  |  |  |  |

|              |                                                                | ermediate mess<br>message priori |                                |                  |                  |                 |                 |  |  |  |  |

| <b>.</b> –   |                                                                |                                  | -                              |                  |                  |                 |                 |  |  |  |  |

| Note 1: ⊤    | his bit is cleared                                             | when IXREQ                       | s set.                         |                  |                  |                 |                 |  |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0              | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|---------------|---------------------------|------------------|---------------|------------------|------------------|-----------------|-------|

|               | —                         |                  | SID10         | SID9             | SID8             | SID7            | SID6  |

| bit 15        |                           |                  |               |                  |                  |                 | bit 8 |

| R/W-x         | R/W-x                     | R/W-x            | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| SID5          | SID4                      | SID3             | SID2          | SID1             | SID0             | SRR             | IDE   |

| bit 7         |                           | •                |               |                  |                  |                 | bit 0 |

| Legend:       |                           |                  |               |                  |                  |                 |       |

| R = Readabl   | e bit                     | W = Writable     | bit           | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at | POR                       | '1' = Bit is set |               | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |                           |                  |               |                  |                  |                 |       |

| bit 15-13     | Unimplemen                | ted: Read as '   | כי            |                  |                  |                 |       |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | tandard Identifi | ier bits      |                  |                  |                 |       |

| bit 1         | SRR: Substitu             | ute Remote Re    | quest bit     |                  |                  |                 |       |

|               | When IDE =                | ):               |               |                  |                  |                 |       |

|               | 1 = Message               | will request rer | note transmis | ssion            |                  |                 |       |

|               | 0 = Normal m              | lessage          |               |                  |                  |                 |       |

|               | When IDE = 1              | L:               |               |                  |                  |                 |       |

|               | The SRR bit r             | must be set to ' | 1'.           |                  |                  |                 |       |

| bit 0         | IDE: Extende              | d Identifier bit |               |                  |                  |                 |       |

|               | 1 = Message               | will transmit Ex | tended Ident  | ifier            |                  |                 |       |

|               |                           | will transmit St |               |                  |                  |                 |       |

|               |                           |                  |               |                  |                  |                 |       |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                               | U-0   | U-0              | U-0   | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

| —                                 | —     | —                |       | EID17                              | EID16 | EID15              | EID14 |  |

| bit 15                            |       |                  |       |                                    |       |                    | bit 8 |  |

|                                   |       |                  |       |                                    |       |                    |       |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

| EID13                             | EID12 | EID11            | EID10 | EID9                               | EID8  | EID7               | EID6  |  |

| bit 7                             |       |                  |       |                                    |       |                    | bit 0 |  |

|                                   |       |                  |       |                                    |       |                    |       |  |

| Legend:                           |       |                  |       |                                    |       |                    |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR                 |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |

| L                                 |       |                  |       |                                    |       |                    |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

## REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|----------------------------------------------------------------------|-------|-------|-------|-------------------|-------|-----------------|-------|

|                                                                      |       |       | PTGA  | DJ<15:8>          |       |                 |       |

| bit 15                                                               |       |       |       |                   |       |                 | bit 8 |

|                                                                      |       |       |       |                   |       |                 |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                                                      |       |       | PTGA  | DJ<7:0>           |       |                 |       |

| bit 7                                                                |       |       |       |                   |       |                 | bit 0 |

|                                                                      |       |       |       |                   |       |                 |       |

| Legend:                                                              |       |       |       |                   |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |                   |       |                 |       |

| -n = Value at POR '1' = Bit is set                                   |       |       |       | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

## REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PTGL0<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15      |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0      | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|----------|-------|-------|-------|-------|-------|-------|--|--|

| PTGL0<7:0> |          |       |       |       |       |       |       |  |  |

| bit 7      | bit 7 bi |       |       |       |       |       |       |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 15-0 PTGL0<15:0>: PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

NOTES:

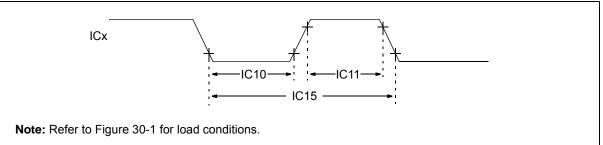

#### FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                  |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                                |      |       |                                  |                                  |  |

|-----------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No. Symbol Characteristics <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                       | Min.                                           | Max. | Units | Conditions                       |                                  |  |

| IC10                                                | TccL | ICx Input Low Time                                                                                                                                                                                                                                                                    | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 |      | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11                                                | ТссН | ICx Input High Time                                                                                                                                                                                                                                                                   | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15                                                | TccP | ICx Input Period                                                                                                                                                                                                                                                                      | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50  | _    | ns    |                                  |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

| AC CHARA             | CTERISTICS                     |             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|--------------------------------|-------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Transmit Only Transmit/Receive |             | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-42                    | _           | _                                                     | 0,1 | 0,1 | 0,1 |  |

| 10 MHz               | _                              | Table 30-43 | —                                                     | 1   | 0,1 | 1   |  |

| 10 MHz               | —                              | Table 30-44 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                              | —           | Table 30-45                                           | 1   | 0   | 0   |  |

| 11 MHz               | —                              | —           | Table 30-46                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                              | —           | Table 30-47                                           | 0   | 1   | 0   |  |

| 11 MHz               | _                              | _           | Table 30-48                                           | 0   | 0   | 0   |  |

#### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

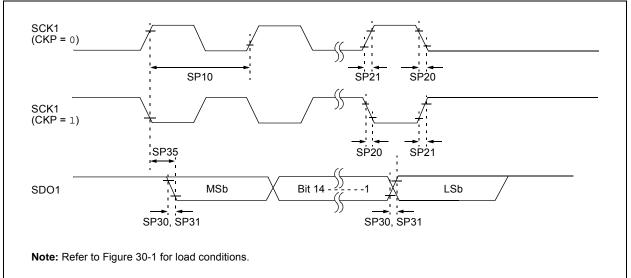

#### FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS