#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp202t-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   | <i>•</i>                       | (se                           |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

#### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

| File Name  | Addr          | Bit 15    | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7      | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|-----------|--------|--------|--------|--------|--------|--------|------------|------------|----------|--------|-------|-------|-------|--------|--------|---------------|

|            | 0400-<br>041E |           |        |        |        |        |        |        | See defini | ion when W | 'IN = x  |        |       |       |       |        |        |               |

| C1BUFPNT1  | 0420          |           | F3BF   | P<3:0> |        |        | F2BI   | ><3:0> |            |            | F1BP     | <3:0>  |       |       | F0BP  | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |           | F7BF   | ><3:0> |        |        | F6BI   | ><3:0> |            |            | F5BP     | <3:0>  |       |       | F4BP  | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |           | F11B   | P<3:0> |        |        | F10B   | P<3:0> |            |            | F9BP     | <3:0>  |       |       | F8BP  | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |           | F15B   | P<3:0> |        |        | F14B   | P<3:0> |            |            | F13B     | D<3:0> |       |       | F12BF | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | MIDE  | _     | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXM1SID  | 0434          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | MIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXM2SID  | 0438          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | MIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF0SID  | 0440          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       | -      |        | xxxx          |

| C1RXF1SID  | 0444          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF2SID  | 0448          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF3SID  | 044C          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF4SID  | 0450          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF5SID  | 0454          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF6SID  | 0458          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF7SID  | 045C          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |           |        |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF8SID  | 0460          | SID<10:3> |        |        |        |        |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          | EID<15:8> |        |        |        |        |        |        |            |            |          |        | EID<  | -     |       |        |        | xxxx          |

| C1RXF9SID  | 0464          |           |        |        |        | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |           |        |        |        | :15:8> |        |        |            |            |          |        | EID<  |       |       |        |        | xxxx          |

| C1RXF10SID | 0468          |           |        |        |        | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |           |        |        |        | :15:8> |        |        |            |            |          |        | EID<  | -     |       |        |        | xxxx          |

| C1RXF11SID | 046C          |           |        |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | -     | EID<   | 17:16> | xxxx          |

#### TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | —      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | —      |        | _      | —      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

#### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | _      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       | •     | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | _      | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

#### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

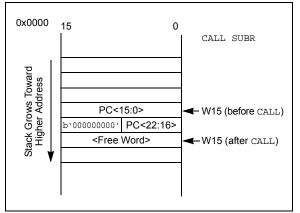

#### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

### 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

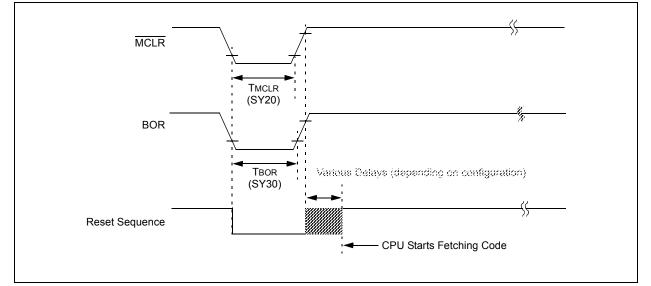

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                       | U-0              | U-0             | U-0             | U-0              | U-0      | R/W-0   |

|-----------------|-------------------------------------------|------------------|-----------------|-----------------|------------------|----------|---------|

| _               | —                                         | —                |                 | —               | —                | —        | PLLDIV8 |

| bit 15          |                                           |                  |                 |                 |                  |          | bit 8   |

|                 |                                           |                  |                 |                 |                  |          |         |

| R/W-0           | R/W-0                                     | R/W-1            | R/W-1           | R/W-0           | R/W-0            | R/W-0    | R/W-0   |

| PLLDIV7         | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3         | PLLDIV2          | PLLDIV1  | PLLDIV0 |

| bit 7           |                                           |                  |                 |                 |                  |          | bit 0   |

|                 |                                           |                  |                 |                 |                  |          |         |

| Legend:         |                                           |                  |                 |                 |                  |          |         |

| R = Readable    | bit                                       | W = Writable     | bit             | U = Unimpler    | mented bit, read | as '0'   |         |

| -n = Value at P | OR                                        | '1' = Bit is set | ared            | x = Bit is unkr | nown             |          |         |

|                 |                                           |                  |                 |                 |                  |          |         |

| bit 15-9        | Unimplemen                                | ted: Read as '   | 0'              |                 |                  |          |         |

| bit 8-0         | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted   | as 'M', PLL mul  | tiplier) |         |

|                 | 111111111 =                               | = 513            |                 |                 |                  |          |         |

|                 | •                                         |                  |                 |                 |                  |          |         |

|                 | •                                         |                  |                 |                 |                  |          |         |

|                 | •                                         |                  |                 |                 |                  |          |         |

|                 | 000110000 =                               | = 50 (default)   |                 |                 |                  |          |         |

|                 |                                           |                  |                 |                 |                  |          |         |

|                 | •                                         |                  |                 |                 |                  |          |         |

|                 | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                 |                  |          |         |

|                 |                                           |                  |                 |                 |                  |          |         |

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|--|

| —     | —   |       | RP120R<5:0> |       |       |       |       |  |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### 18.3 SPIx Control Registers

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 SPIEN SPISIDL SPIBEC<2:0> \_\_\_\_\_ bit 15 R/W-0 R/W-0 R/W-0 R/C-0, HS R/W-0 R/W-0 R-0, HS, HC R-0, HS, HC SRMPT SPIROV SRXMPT SISEL2 SISEL1 SISEL0 SPITBF SPIRBF bit 7 Legend: C = Clearable bit HS = Hardware Settable bit HC = Hardware Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables the module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables the module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues the module operation when device enters Idle mode 0 = Continues the module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPIx transfers that are pending. Slave mode: Number of SPIx transfers that are unread. SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) bit 7 1 = SPIx Shift register is empty and Ready-To-Send or receive the data 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit

#### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register 0 = No overflow has occurred SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

- 1 = RX FIFO is empty

- 0 = RX FIFO is not empty

#### bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

- 111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

- 110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

- 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

- 100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

- 011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

- 010 = Interrupt when the SPIx receive buffer is 3/4 or more full

- 001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

- 000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

bit 5

bit 8

bit 0

| U-0                 | U-0                                                                                                                 | U-0             | R/W-0                                 | R/W-0            | R/W-0                                   | R/W-0           | R/W-0                |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------|------------------|-----------------------------------------|-----------------|----------------------|--|--|--|

| —                   | —                                                                                                                   | _               | DISSCK                                | DISSDO           | MODE16                                  | SMP             | CKE <sup>(1)</sup>   |  |  |  |

| bit 15              |                                                                                                                     |                 |                                       |                  |                                         |                 | bit                  |  |  |  |

|                     |                                                                                                                     |                 |                                       |                  |                                         |                 |                      |  |  |  |

| R/W-0               | R/W-0                                                                                                               | R/W-0           | R/W-0                                 | R/W-0            | R/W-0                                   | R/W-0           | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup> | N <sup>(2)</sup> CKP MSTEN SPRE2 <sup>(3)</sup> SPRE1 <sup>(3)</sup> SPRE0 <sup>(3)</sup> PPRE1 <sup>(3)</sup> PPRE |                 |                                       |                  |                                         |                 |                      |  |  |  |

| bit 7               |                                                                                                                     |                 |                                       |                  |                                         |                 | bit                  |  |  |  |

| Legend:             |                                                                                                                     |                 |                                       |                  |                                         |                 |                      |  |  |  |

| R = Readabl         | e bit                                                                                                               | W = Writable    | bit                                   | U = Unimpler     | mented bit, read                        | l as '0'        |                      |  |  |  |

| -n = Value at       | POR                                                                                                                 | '1' = Bit is se | t                                     | '0' = Bit is cle | ared                                    | x = Bit is unkr | nown                 |  |  |  |

|                     |                                                                                                                     |                 |                                       |                  |                                         |                 |                      |  |  |  |

| bit 15-13           | Unimplemen                                                                                                          | ted: Read as    | ʻ0'                                   |                  |                                         |                 |                      |  |  |  |

| bit 12              | DISSCK: Disa                                                                                                        | able SCKx Pin   | bit (SPIx Mas                         | ter modes only   | /)                                      |                 |                      |  |  |  |

|                     | 1 = Internal S                                                                                                      | Plx clock is di | sabled, pin fun                       | ctions as I/O    | -                                       |                 |                      |  |  |  |

|                     | 0 = Internal S                                                                                                      | PIx clock is er | nabled                                |                  |                                         |                 |                      |  |  |  |

| bit 11              | DISSDO: Dis                                                                                                         | able SDOx Pir   | n bit                                 |                  |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     |                 | y the module; p                       | oin functions as | s I/O                                   |                 |                      |  |  |  |

|                     |                                                                                                                     | is controlled b | •                                     |                  |                                         |                 |                      |  |  |  |

| bit 10              |                                                                                                                     | ,               | nunication Sele                       | ect bit          |                                         |                 |                      |  |  |  |

|                     | <ol> <li>1 = Communication is word-wide (16 bits)</li> <li>0 = Communication is byte-wide (8 bits)</li> </ol>       |                 |                                       |                  |                                         |                 |                      |  |  |  |

| bit 9               |                                                                                                                     | ata Input Sam   | . ,                                   |                  |                                         |                 |                      |  |  |  |

|                     | Master mode                                                                                                         |                 | pie i nase bit                        |                  |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     | -               | t end of data o                       | utput time       |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     |                 | t middle of data                      |                  |                                         |                 |                      |  |  |  |

|                     | Slave mode:                                                                                                         |                 |                                       |                  |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     |                 | SPIx is used i                        | n Slave mode.    |                                         |                 |                      |  |  |  |

| bit 8               |                                                                                                                     | lock Edge Sele  |                                       |                  |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     |                 |                                       |                  | clock state to lo<br>ock state to activ |                 |                      |  |  |  |

| bit 7               |                                                                                                                     |                 | bit (Slave mo                         |                  |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     | s used for Slav |                                       |                  |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     |                 |                                       | is controlled b  | by port function                        |                 |                      |  |  |  |

| bit 6               |                                                                                                                     | Polarity Select |                                       |                  |                                         |                 |                      |  |  |  |

|                     |                                                                                                                     |                 | nigh level; activ<br>ow level; active |                  |                                         |                 |                      |  |  |  |

| bit 5               |                                                                                                                     | ter Mode Enal   |                                       | C                |                                         |                 |                      |  |  |  |

|                     | 1 = Master m                                                                                                        | ode             |                                       |                  |                                         |                 |                      |  |  |  |

|                     | 0 = Slave mo                                                                                                        | de              |                                       |                  |                                         |                 |                      |  |  |  |

| Note 1: T           | he CKE bit is not                                                                                                   | used in Frame   | d SPI modes I                         | Program this hi  | it to '0' for Fram                      | ed SPI modes (  | FRMEN = <sup>-</sup> |  |  |  |

|                     | his bit must be cl                                                                                                  |                 |                                       |                  |                                         |                 |                      |  |  |  |

| <u> </u>            |                                                                                                                     |                 |                                       |                  |                                         |                 |                      |  |  |  |

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | U-0                                                                                      | U-0                                                                                            | R/W-0                        | R/W-0                 | R/W-0                                                          | R/W-0                 | R/W-0                 |  |  |  |  |

|------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------|-----------------------|----------------------------------------------------------------|-----------------------|-----------------------|--|--|--|--|

| CH0NB      | _                                                                                        | —                                                                                              | CH0SB4 <sup>(1)</sup>        | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>                                          | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |  |

| bit 15     | •                                                                                        |                                                                                                |                              | •                     |                                                                |                       | bit 8                 |  |  |  |  |

|            |                                                                                          |                                                                                                |                              |                       |                                                                |                       |                       |  |  |  |  |

| R/W-0      | U-0                                                                                      | U-0                                                                                            | R/W-0                        | R/W-0                 | R/W-0                                                          | R/W-0                 | R/W-0                 |  |  |  |  |

| CH0NA      |                                                                                          |                                                                                                | CH0SA4 <sup>(1)</sup>        | CH0SA3 <sup>(1)</sup> | <sup>(1)</sup> CH0SA2 <sup>(1)</sup> CH0SA1 <sup>(1)</sup> CH0 |                       |                       |  |  |  |  |

| bit 7      |                                                                                          |                                                                                                |                              |                       |                                                                |                       | bit (                 |  |  |  |  |

|            |                                                                                          |                                                                                                |                              |                       |                                                                |                       |                       |  |  |  |  |

| Legend:    |                                                                                          |                                                                                                |                              |                       |                                                                |                       |                       |  |  |  |  |

| R = Read   |                                                                                          | W = Writable                                                                                   |                              | •                     | nented bit, read                                               |                       |                       |  |  |  |  |

| -n = Value | e at POR                                                                                 | '1' = Bit is set                                                                               |                              | '0' = Bit is cle      | ared                                                           | x = Bit is unkr       | lown                  |  |  |  |  |

| bit 15     |                                                                                          | nannel 0 Negative                                                                              | Input Soloot fo              | r Samala MUV          | 'D hit                                                         |                       |                       |  |  |  |  |

| DIL 15     |                                                                                          | el 0 negative input                                                                            |                              |                       |                                                                |                       |                       |  |  |  |  |

|            |                                                                                          | el 0 negative input                                                                            |                              |                       |                                                                |                       |                       |  |  |  |  |

| bit 14-13  | Unimplem                                                                                 | ented: Read as 'o                                                                              | )'                           |                       |                                                                |                       |                       |  |  |  |  |

| bit 12-8   | CH0SB<4:                                                                                 | 0>: Channel 0 Po                                                                               | sitive Input Sele            | ect for Sample        | MUXB bits <sup>(1)</sup>                                       |                       |                       |  |  |  |  |

|            |                                                                                          | pen; use this sele                                                                             |                              |                       |                                                                | ement                 |                       |  |  |  |  |

|            | 11110 <b>= C</b>                                                                         | nannel 0 positive in                                                                           | put is connected             | to the CTMU te        | emperature mea                                                 | surement diode        | (CTMU TEMF            |  |  |  |  |

|            |                                                                                          | 11101 = Reserved                                                                               |                              |                       |                                                                |                       |                       |  |  |  |  |

|            |                                                                                          | 11100 = Reserved                                                                               |                              |                       |                                                                |                       |                       |  |  |  |  |

|            |                                                                                          | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup> |                              |                       |                                                                |                       |                       |  |  |  |  |

|            |                                                                                          | hannel 0 positive                                                                              |                              |                       |                                                                |                       |                       |  |  |  |  |

|            | 11000 <b>= C</b>                                                                         | hannel 0 positive                                                                              | input is the outp            | out of OA1/AN3        | <sub>3</sub> (2)                                               |                       |                       |  |  |  |  |

|            | 10111 <b>= R</b>                                                                         | eserved                                                                                        |                              |                       |                                                                |                       |                       |  |  |  |  |

|            | •                                                                                        |                                                                                                |                              |                       |                                                                |                       |                       |  |  |  |  |

|            | •                                                                                        |                                                                                                |                              |                       |                                                                |                       |                       |  |  |  |  |

|            | 10000 <b>= R</b>                                                                         | eserved                                                                                        |                              |                       |                                                                |                       |                       |  |  |  |  |

|            | 01111 <b>= C</b>                                                                         | hannel 0 positive                                                                              | input is AN15 <sup>(3)</sup> |                       |                                                                |                       |                       |  |  |  |  |

|            | 01110 = C                                                                                | hannel 0 positive                                                                              | input is AN14 <sup>(3)</sup> |                       |                                                                |                       |                       |  |  |  |  |

|            | 01101 = C                                                                                | hannel 0 positive                                                                              | Input is AN130               |                       |                                                                |                       |                       |  |  |  |  |

|            | •                                                                                        |                                                                                                |                              |                       |                                                                |                       |                       |  |  |  |  |

|            | •                                                                                        |                                                                                                |                              |                       |                                                                |                       |                       |  |  |  |  |

|            | 00010 <b>= C</b>                                                                         | hannel 0 positive                                                                              | input is AN2 <sup>(3)</sup>  |                       |                                                                |                       |                       |  |  |  |  |

|            |                                                                                          | hannel 0 positive<br>hannel 0 positive                                                         |                              |                       |                                                                |                       |                       |  |  |  |  |