Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 25                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 8x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 36-VFTLA Exposed Pad                                                          |

| Supplier Device Package    | 36-VTLA (5x5)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp203-e-tl |

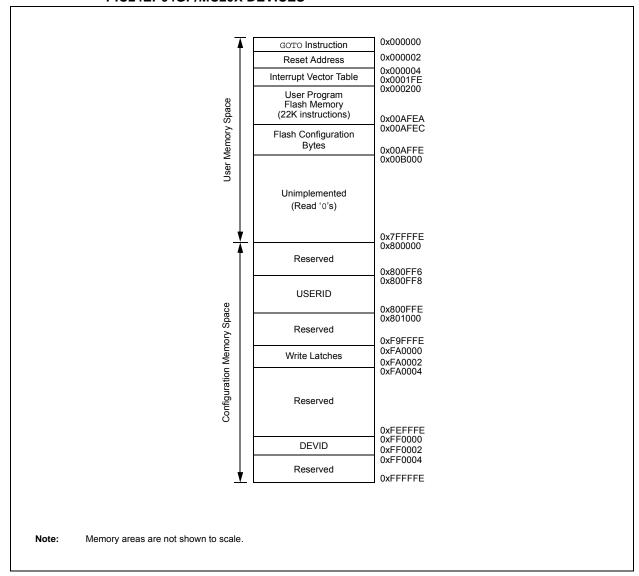

FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

DS70000657H-page 77

## TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

| File Name | Addr. | Bit 15                                                                   | Bit 14                    | Bit 13   | Bit 12 | Bit 11    | Bit 10       | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5  | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

|-----------|-------|--------------------------------------------------------------------------|---------------------------|----------|--------|-----------|--------------|-------|-------------|-------------|--------------|--------|--------|----------|-----------|----------|-------|---------------|

| OC1CON1   | 0900  | _                                                                        | _                         | OCSIDL   | 0      | CTSEL<2:0 | <b> &gt;</b> | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902  | FLTMD                                                                    | FLTOUT                    | FLTTRIEN | OCINV  | _         | _            | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYI      | NCSEL<4:0 | >        |       | 000C          |

| OC1RS     | 0904  |                                                                          |                           |          |        |           |              | Outp  | out Compare | e 1 Seconda | ary Register |        |        |          |           |          |       | xxxx          |

| OC1R      | 0906  |                                                                          |                           |          |        |           |              |       | Output Co   | mpare 1 Re  | gister       |        |        |          |           |          |       | xxxx          |

| OC1TMR    | 0908  |                                                                          |                           |          |        |           |              |       | Timer V     | alue 1 Regi | ster         |        |        |          |           |          |       | xxxx          |

| OC2CON1   | 090A  | _                                                                        | _                         | OCSIDL   | 0      | CTSEL<2:0 | )>           | 1     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2   | 090C  | FLTMD FLTOUT FLTTRIEN OCINV — — OC32 OCTRIG TRIGSTAT OCTRIS SYNCSEL<4:0> |                           |          |        |           |              | 000C  |             |             |              |        |        |          |           |          |       |               |

| OC2RS     | 090E  | Output Compare 2 Secondary Register                                      |                           |          |        |           |              |       |             |             |              | xxxx   |        |          |           |          |       |               |

| OC2R      | 0910  | Output Compare 2 Register                                                |                           |          |        |           |              |       |             |             | xxxx         |        |        |          |           |          |       |               |

| OC2TMR    | 0912  | Timer Value 2 Register                                                   |                           |          |        |           |              |       |             |             | xxxx         |        |        |          |           |          |       |               |

| OC3CON1   | 0914  | _                                                                        | _                         | OCSIDL   | 0      | CTSEL<2:0 | )>           | 1     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916  | FLTMD                                                                    | FLTOUT                    | FLTTRIEN | OCINV  | _         | _            | 1     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYI      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS     | 0918  |                                                                          |                           |          |        |           |              | Outp  | out Compare | e 3 Seconda | ary Register |        |        |          |           |          |       | xxxx          |

| OC3R      | 091A  |                                                                          |                           |          |        |           |              |       | Output Co   | mpare 3 Re  | gister       |        |        |          |           |          |       | xxxx          |

| OC3TMR    | 091C  |                                                                          |                           |          |        |           |              |       | Timer V     | alue 3 Regi | ster         |        |        |          |           |          |       | xxxx          |

| OC4CON1   | 091E  | _                                                                        | _                         | OCSIDL   | 0      | CTSEL<2:0 | )>           | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920  | FLTMD                                                                    | FLTOUT                    | FLTTRIEN | OCINV  | _         | _            | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYI      | NCSEL<4:0 | >        |       | 000C          |

| OC4RS     | 0922  | •                                                                        | •                         |          | •      |           |              | Outp  | out Compare | e 4 Seconda | ary Register | •      | •      |          |           |          | •     | xxxx          |

| OC4R      | 0924  |                                                                          | Output Compare 4 Register |          |        |           |              |       |             |             |              | xxxx   |        |          |           |          |       |               |

| OC4TMR    | 0926  |                                                                          |                           |          |        |           |              |       | Timer V     | alue 4 Regi | ster         |        |        |          |           |          |       | xxxx          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 7-1: SR: CPU STATUS REGISTER(1)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/C-0 | R/C-0 | R-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-----|-------|

| OA     | ОВ    | SA    | SB    | OAB   | SAB   | DA  | DC    |

| bit 15 |       |       |       |       |       |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|-------------------------|----------------------|-----|-------|-------|-------|-------|

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA  | N     | OV    | Z     | С     |

| bit 7                |                         |                      | •   |       | •     | •     | bit 0 |

| Legend:           | C = Clearable bit                                      |                      |                    |

|-------------------|--------------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | it W = Writable bit U = Unimplemented bit, read as '0' |                      | l as '0'           |

| -n = Value at POR | '1'= Bit is set                                        | '0' = Bit is cleared | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

110 = CPU Interrupt Priority Level is 6 (14)

101 = CPU Interrupt Priority Level is 5 (13)

100 = CPU Interrupt Priority Level is 4 (12)

011 = CPU Interrupt Priority Level is 3 (11)

010 = CPU Interrupt Priority Level is 2 (10)

001 = CPU Interrupt Priority Level is 1 (9)

000 = CPU Interrupt Priority Level is 0 (8)

Note 1: For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- · Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- · Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 0000000                              | _                                                       |                                                        |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | _                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | _                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | _                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | _                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | _                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | _                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | _                                                       | _                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | _                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | _                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        | _                                                      |

| UART2TX – UART2 Transmitter   | 00011111                             | _                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | _                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | _                                                      |

## 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | _   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0       | R/W-0  | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |  |  |

|-------------|--------|------|-----|-------------------|-----|-----|-------|--|--|

| CLKLOCK     | IOLOCK | LOCK | _   | CF <sup>(3)</sup> | _   | _   | OSWEN |  |  |

| bit 7 bit 0 |        |      |     |                   |     |     |       |  |  |

| Legend:           | y = Value set from Configu | y = Value set from Configuration bits on POR |                    |  |  |  |  |  |

|-------------------|----------------------------|----------------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0'           |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |  |  |

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits (read-only)

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 11 **Unimplemented:** Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

111 = Fast RC Oscillator (FRC) with Divide-by-n

110 = Fast RC Oscillator (FRC) with Divide-by-16

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 7 CLKLOCK: Clock Lock Enable bit

1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified

0 = Clock and PLL selections are not locked, configurations may be modified

bit 6 IOLOCK: I/O Lock Enable bit

1 = I/O lock is active

0 = I/O lock is not active

bit 5 **LOCK:** PLL Lock Status bit (read-only)

1 = Indicates that PLL is in lock or PLL start-up timer is satisfied

0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

**Note 1:** Writes to this register require an unlock sequence. Refer to "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual" (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

### 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{\,\text{TM}}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

# 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

# REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-------|------------|-------|-------|-------|-------|-------|--|--|

| _      |       | QEB1R<6:0> |       |       |       |       |       |  |  |

| bit 15 |       |            |       |       |       |       | bit 8 |  |  |

| U-0   | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-------|------------|-------|-------|-------|-------|-------|--|--|

| _     |       | QEA1R<6:0> |       |       |       |       |       |  |  |

| bit 7 |       |            |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 QEB1R<6:0>: Assign B (QEB) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 Unimplemented: Read as '0'

bit 6-0 **QEA1R<6:0>:** Assign A (QEA) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

### **REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8**

| U-0    | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-----|-------|-------------|-------|-------|-------|-------|--|--|--|

| _      | _   |       | RP118R<5:0> |       |       |       |       |  |  |  |

| bit 15 |     |       |             |       |       |       | bit 8 |  |  |  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP118R<5:0>: Peripheral Output Function is Assigned to RP118 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-0 **Unimplemented:** Read as '0'

### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| _     | _   |       |       | RP120 | OR<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 RP120R<5:0>: Peripheral Output Function is Assigned to RP120 Output Pin bits

(see Table 11-3 for peripheral function numbers)

### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

bit 6-4

SYNCSRC<2:0>: Synchronous Source Selection bits<sup>(1)</sup>

111 = Reserved

100 = Reserved

011 = PTGO17<sup>(2)</sup>

010 = PTGO16<sup>(2)</sup>

001 = Reserved

000 = SYNCI1 input from PPS

bit 3-0

SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits<sup>(1)</sup>

1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event

0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

0000 = 1:1 Postscaler generates Special Event Trigger on every compare match event

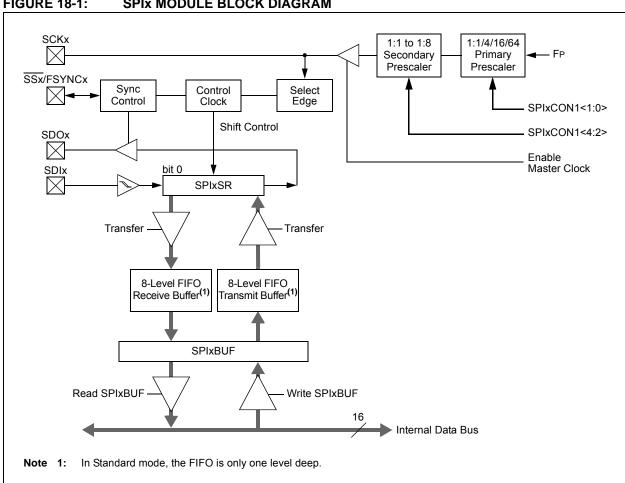

**FIGURE 18-1:** SPIX MODULE BLOCK DIAGRAM

### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| _      | _   | _   | _   | _   | _   | AMSK9 | AMSK8 |

| bit 15 |     |     |     |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-0 AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

#### REGISTER 21-3: **CXVEC: ECANX INTERRUPT CODE REGISTER**

| U-0    | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     | R-0     |

|--------|-----|-----|---------|---------|---------|---------|---------|

| _      | _   | _   | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | R-1    | R-0    | R-0    | R-0    | R-0    | R-0    | R-0    |

|-------|--------|--------|--------|--------|--------|--------|--------|

| _     | ICODE6 | ICODE5 | ICODE4 | ICODE3 | ICODE2 | ICODE1 | ICODE0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12-8 FILHIT<4:0>: Filter Hit Number bits

10000-11111 = Reserved

01111 = Filter 15

00001 = Filter 1

00000 = Filter 0

bit 7 Unimplemented: Read as '0'

bit 6-0 ICODE<6:0>: Interrupt Flag Code bits

1000101-1111111 = Reserved

1000100 = FIFO almost full interrupt

1000011 = Receiver overflow interrupt

1000010 = Wake-up interrupt

1000001 = Error interrupt

1000000 **= No interrupt**

0010000-0111111 = Reserved

0001111 = RB15 buffer interrupt

0001001 = RB9 buffer interrupt

0001000 = RB8 buffer interrupt

0000111 = TRB7 buffer interrupt

0000110 = TRB6 buffer interrupt

0000101 = TRB5 buffer interrupt

0000100 = TRB4 buffer interrupt

0000011 = TRB3 buffer interrupt

0000010 = TRB2 buffer interrupt

0000001 = TRB1 buffer interrupt

0000000 = TRB0 buffer interrupt

# REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | EXIDE | _   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 SID<10:0>: Standard Identifier bits

1 = Message address bit, SIDx, must be '1' to match filter 0 = Message address bit, SIDx, must be '0' to match filter

bit 4 Unimplemented: Read as '0'

bit 3 **EXIDE:** Extended Identifier Enable bit

If MIDE = 1:

1 = Matches only messages with Extended Identifier addresses0 = Matches only messages with Standard Identifier addresses

If MIDE = 0:

Ignores EXIDE bit.

bit 2 Unimplemented: Read as '0'

bit 1-0 **EID<17:16>:** Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter 0 = Message address bit, EIDx, must be '0' to match filter

### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | Byt   | te 3  |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | Byt   | e 2   |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Byte 3<15:8>:** ECAN Message Byte 3 bits bit 7-0 **Byte 2<7:0>:** ECAN Message Byte 2 bits

### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | Byt   | te 5  |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | Byt   | e 4   |       |       |       |

| bit 7 |       |       |       |       | bit 0 |       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Byte 5<15:8>:** ECAN Message Byte 5 bits bit 7-0 **Byte 4<7:0>:** ECAN Message Byte 4 bits

| dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

# 31.1 High-Temperature DC Characteristics

TABLE 31-1: OPERATING MIPS VS. VOLTAGE

|                |                                     |                              | Max MIPS                                                              |  |

|----------------|-------------------------------------|------------------------------|-----------------------------------------------------------------------|--|

| Characteristic | V <sub>DD</sub> Range<br>(in Volts) | Temperature Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |  |

| HDC5           | 3.0 to 3.6V <sup>(1)</sup>          | -40°C to +150°C              | 40                                                                    |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules, such as the ADC, may have degraded performance. Device functionality is tested but not characterized.

### **TABLE 31-2: THERMAL OPERATING CONDITIONS**

| Rating                                                                                                                                                                                       | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High-Temperature Devices                                                                                                                                                                     |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                         | TJ     | -40 | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                          | TA     | -40 | _           | +150 | °C   |

| Power Dissipation: Internal Chip Power Dissipation: $PINT = VDD \ x \ (IDD - \Sigma \ IOH)$ I/O Pin Power Dissipation: $I/O = \Sigma \ (\{VDD - VOH\} \ x \ IOH) + \Sigma \ (VOL \ x \ IOL)$ |        | į   | PINT + PI/0 | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                            |        | (   | TJ – TA)/θJ | Α    | W    |

### TABLE 31-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| .,                 | ·              |                |                                                                                                                                                          | _ 00. |     |   |                 |

|--------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|---|-----------------|

| DC CHARACTERISTICS |                |                | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ |       |     |   |                 |

| Parameter No.      | Symbol         | Characteristic | Min Typ Max Units Conditions                                                                                                                             |       |     |   | Conditions      |

| Operating Voltage  |                |                |                                                                                                                                                          |       |     |   |                 |

| HDC10              | Supply Voltage |                |                                                                                                                                                          |       |     |   |                 |

|                    | VDD            | _              | 3.0                                                                                                                                                      | 3.3   | 3.6 | V | -40°C to +150°C |

## 33.1 Package Marking Information (Continued)

36-Lead VTLA (TLA)

Example

44-Lead VTLA (TLA)

Example

44-Lead TQFP

Example

44-Lead QFN (8x8x0.9 mm)

Example

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | N        | ILLIMETER | S    |  |

|-------------------------|--------|----------|-----------|------|--|

| Dimension               | Limits | MIN      | NOM       | MAX  |  |

| Number of Pins          | Ν      |          | 28        |      |  |

| Pitch                   | е      | 0.65 BSC |           |      |  |

| Overall Height          | Α      | 0.80     | 0.90      | 1.00 |  |

| Standoff                | A1     | 0.00     | 0.02      | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF |           |      |  |

| Overall Width           | Е      | 6.00 BSC |           |      |  |

| Exposed Pad Width       | E2     | 3.65     | 3.70      | 4.70 |  |

| Overall Length          | D      | 6.00 BSC |           |      |  |

| Exposed Pad Length      | D2     | 3.65     | 3.70      | 4.70 |  |

| Terminal Width          | b      | 0.23     | 0.30      | 0.35 |  |

| Terminal Length         | L      | 0.30     | 0.40      | 0.50 |  |

| Terminal-to-Exposed Pad | K      | 0.20     | -         | -    |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2

## 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | N    | <b>IILLIMETER</b> | S    |  |  |

|------------------------|--------|------|-------------------|------|--|--|

| Dimension              | Limits | MIN  | NOM               | MAX  |  |  |

| Number of Pins         |        |      | 48                |      |  |  |

| Pitch                  | е      |      | 0.40 BSC          |      |  |  |

| Overall Height         | Α      | 0.45 | 0.50              | 0.55 |  |  |

| Standoff               | A1     | 0.00 | 0.02              | 0.05 |  |  |

| Contact Thickness      | A3     |      | 0.127 REF         |      |  |  |

| Overall Width          | Е      |      | 6.00 BSC          |      |  |  |

| Exposed Pad Width      | E2     | 4.45 | 4.60              | 4.75 |  |  |

| Overall Length         | D      |      | 6.00 BSC          |      |  |  |

| Exposed Pad Length     | D2     | 4.45 | 4.60              | 4.75 |  |  |

| Contact Width          | b      | 0.15 | 0.20              | 0.25 |  |  |

| Contact Length         | Г      | 0.30 | 0.40              | 0.50 |  |  |

| Contact-to-Exposed Pad | K      | 0.20 | -                 | -    |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2

TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 16.0 "High-Speed<br>PWM Module<br>(dsPIC33EPXXXMC20X/50X<br>and PIC24EPXXXMC20X<br>Devices Only)" | Updated the High-Speed PWM Module Register Interconnection Diagram (see Figure 16-2).  Added the TRGCONx and TRIGx registers (see Register 16-12 and Register 16-14, respectively).                                                                                                                                                                                                                                                                                      |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                   | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                                                                                                                                                                                        |

| Section 22.0 "Charge Time Measurement Unit (CTMU)"                                                        | Updated the IRNG<1:0> bit value definitions and added Note 2 in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                                                                                                                                                                   |

| Section 25.0 "Op amp/<br>Comparator Module"                                                               | Updated the Op amp/Comparator I/O Operating Modes Diagram (see Figure 25-1).  Updated the User-programmable Blanking Function Block Diagram (see Figure 25-3).  Updated the Digital Filter Interconnect Block Diagram (see Figure 25-4).  Added Section 25.1 "Op amp Application Considerations".  Added Note 2 to the Comparator Control Register (see Register 25-2).  Updated the bit definitions in the Comparator Mask Gating Control Register (see Register 25-5). |

| Section 27.0 "Special Features"                                                                           | Updated the FICD Configuration Register, updated Note 1, and added Note 3 in the Configuration Byte Register Map (see Table 27-1).  Added Section 27.2 "User ID Words".                                                                                                                                                                                                                                                                                                  |

| Section 30.0 "Electrical Characteristics"                                                                 | Updated the following Absolute Maximum Ratings:  • Maximum current out of Vss pin  • Maximum current into VDD pin  Added Note 1 to the Operating MIPS vs. Voltage (see Table 30-1).                                                                                                                                                                                                                                                                                      |

|                                                                                                           | Updated all Idle Current (IIDLE) Typical and Maximum DC Characteristics values (see Table 30-7).                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                           | Updated all Doze Current (IDOZE) Typical and Maximum DC Characteristics values (see Table 30-9).                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                           | Added Note 2, removed Parameter CM24, updated the Typical values Parameters CM10, CM20, CM21, CM32, CM41, CM44, and CM45, and updated the Minimum values for CM40 and CM41, and the Maximum value for CM40 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                                                                                                                                                                            |

|                                                                                                           | Updated Note 2 and the Typical value for Parameter VR310 in the Op amp/<br>Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                                                                                                                                                                                                                                                                  |

|                                                                                                           | Added Note 1, removed Parameter VRD312, and added Parameter VRD314 to the Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                                                                                                                                                                                                                                                       |

|                                                                                                           | Updated the Minimum, Typical, and Maximum values for Internal LPRC Accuracy (see Table 30-22).                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                           | Updated the Minimum, Typical, and Maximum values for Parameter SY37 in the Reset, Watchdog Timer, Oscillator Start-up Timer, Power-up Timer Timing Requirements (see Table 30-24).                                                                                                                                                                                                                                                                                       |

|                                                                                                           | The Maximum Data Rate values were updated for the SPI2 Maximum Data/Clock Rate Summary (see Table 30-35)                                                                                                                                                                                                                                                                                                                                                                 |