Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp204-e-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                                                    |     |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             |     |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           |     |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

|       | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     |     |

|       | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) |     |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                                                 |     |

|       | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    |     |

|       | Charge Time Measurement Unit (CTMU)                                                                |     |

|       | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    |     |

|       | Peripheral Trigger Generator (PTG) Module                                                          |     |

| 25.0  | Op Amp/Comparator Module                                                                           |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                                               |     |

| 27.0  |                                                                                                    |     |

|       |                                                                                                    |     |

| 29.0  | Development Support                                                                                |     |

|       | Electrical Characteristics                                                                         |     |

|       | High-Temperature Electrical Characteristics                                                        |     |

|       | DC and AC Device Characteristics Graphs                                                            |     |

|       | Packaging Information                                                                              |     |

|       | ndix A: Revision History                                                                           |     |

|       | (                                                                                                  |     |

|       | Vicrochip Web Site                                                                                 |     |

|       | omer Change Notification Service                                                                   |     |

|       | omer Support                                                                                       |     |

| Produ | uct Identification System                                                                          | 527 |

## TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14         | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8  | Bit 7      | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|----------------|--------|--------|--------|--------|--------------|--------|------------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE           | DIR    | HALF   | NULLW  |        | _            | _      | _          | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _              | _      |        | _      | _      | _            | _      |            |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |                |        |        |        |        |              | STA<15 | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _              | _      | _      | _      | _      | _            | _      |            |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |                |        |        |        |        |              | STB<1  | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —              | _      | _      | _      | —      | —            | —      |            |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |                |        |        |        |        |              | PAD<1  | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _              |        |        |        |        |              |        | CNT<1      | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE           | DIR    | HALF   | NULLW  | —      | —            | —      | _          | —     | AMOD  | E<1:0> | —       | —      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _              | _      |        | _      | _      | _            | _      |            |       | •     | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |                |        |        |        |        |              | STA<15 | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —              | _      | _      | _      | —      | —            | —      |            |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |                |        |        |        |        |              | STB<1  | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | —              | _      | _      |        | _      | _            | _      | STB<23:16> |       |       |        |         | 0000   |        |        |               |

| DMA1PAD   | 0B1C  |        | PAD<15:0> 0000 |        |        |        |        |              |        | 0000       |       |       |        |         |        |        |        |               |

| DMA1CNT   | 0B1E  | _      | —              |        |        |        |        |              |        | CNT<13:0>  |       |       |        |         | 0000   |        |        |               |

| DMA2CON   | 0B20  | CHEN   | SIZE           | DIR    | HALF   | NULLW  | _      | _            | _      | _          | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _              | _      |        | _      | _      | _            | _      |            |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |                |        |        |        |        |              | STA<18 | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _              | _      | _      | _      | _      | _            | _      |            |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |                |        |        |        |        | STB<15:0> 00 |        |            |       |       |        | 0000    |        |        |        |               |

| DMA2STBH  | 0B2A  | _      | _              | _      | _      | _      | _      | _            | _      |            |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |                |        |        |        |        |              | PAD<1  | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _              |        |        |        |        |              |        | CNT<1      | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE           | DIR    | HALF   | NULLW  | _      | _            | _      | _          | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _              | _      | _      | _      | _      | _            | _      |            |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |                |        |        |        |        |              | STA<18 | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _              | _      | _      | _      | _      | _            | _      |            |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |                |        |        |        |        |              | STB<1  | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _              | _      | _      | _      | _      | _            | _      |            |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |                |        |        |        |        |              | PAD<1  | 5:0>       |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _              |        |        |        |        |              |        | CNT<1      | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | —      | —              | —      | —      | —      | —      |              | _      | —          | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —              | _      | _      | _      | _      | _            | _      | _          | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —              | _      | _      | _      | _      | _            | _      | _          | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _              | _      | _      | _      | _      | _            | _      | _          | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |                |        |        |        |        |              | DSADR< | 15:0>      |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —              | —      | —      | —      | —      | —            | —      |            |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

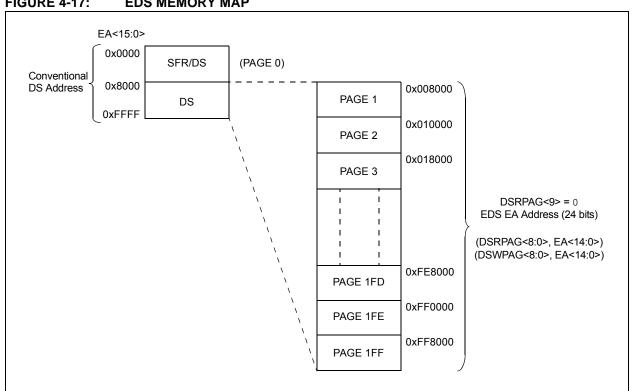

## 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

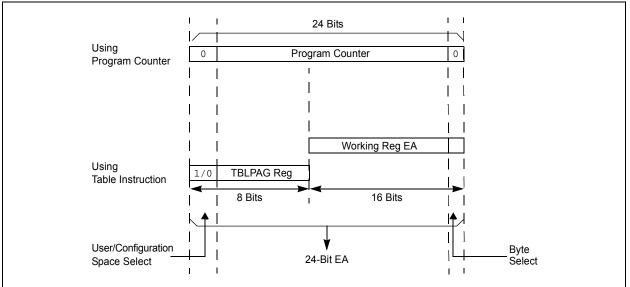

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| R/W-1             | R/W-0                                                                | R/W-0                                             | U-0          | U-0              | U-0              | U-0             | U-0    |  |  |  |  |

|-------------------|----------------------------------------------------------------------|---------------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|--|--|

| GIE               | DISI                                                                 | SWTRAP                                            |              |                  |                  | _               |        |  |  |  |  |

| bit 15            |                                                                      |                                                   |              |                  |                  |                 | bit 8  |  |  |  |  |

|                   |                                                                      |                                                   |              |                  |                  |                 |        |  |  |  |  |

| U-0               | U-0                                                                  | U-0                                               | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|                   | —                                                                    |                                                   |              |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |

| bit 7             |                                                                      |                                                   |              |                  |                  |                 | bit C  |  |  |  |  |

| Legend:           |                                                                      |                                                   |              |                  |                  |                 |        |  |  |  |  |

| R = Readab        | le bit                                                               | W = Writable                                      | bit          | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value at POR |                                                                      | '1' = Bit is set                                  |              | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |

|                   |                                                                      |                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 15            | GIE: Global                                                          | Interrupt Enable                                  | e bit        |                  |                  |                 |        |  |  |  |  |

|                   | 1 = Interrupt                                                        | 1 = Interrupts and associated IE bits are enabled |              |                  |                  |                 |        |  |  |  |  |

|                   | 0 = Interrupts are disabled, but traps are still enabled             |                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 14            | DISI: DISI Instruction Status bit                                    |                                                   |              |                  |                  |                 |        |  |  |  |  |

|                   | 1 = DISI instruction is active<br>0 = DISI instruction is not active |                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 13            | SWTRAP: Software Trap Status bit                                     |                                                   |              |                  |                  |                 |        |  |  |  |  |

|                   | 1 = Software trap is enabled<br>0 = Software trap is disabled        |                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 12-3          | Unimpleme                                                            | nted: Read as '                                   | 0'           |                  |                  |                 |        |  |  |  |  |

| bit 2             | INT2EP: Ext                                                          | ternal Interrupt 2                                | 2 Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|                   |                                                                      | on negative edg                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 1             | INT1EP: Ext                                                          | ternal Interrupt 1                                | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|                   | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge     |                                                   |              |                  |                  |                 |        |  |  |  |  |

| bit 0             | INTOEP: Ext                                                          | ternal Interrupt C                                | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|                   | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge     |                                                   |              |                  |                  |                 |        |  |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0                 | R/W-0                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                         | R/W-0                          | R/W-0            | U-0             | U-0             | U-0   |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| CHEN                  | SIZE                                                                                                                                | DIR                                                                                                                                                                                                                                                                           | HALF                           | NULLW            |                 |                 |       |  |  |  |  |  |

| bit 15                |                                                                                                                                     |                                                                                                                                                                                                                                                                               |                                |                  |                 |                 | bit   |  |  |  |  |  |

| U-0                   | U-0                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                         | R/W-0                          | U-0              | U-0             | R/W-0           | R/W-0 |  |  |  |  |  |

|                       | 0-0                                                                                                                                 | AMODE1                                                                                                                                                                                                                                                                        | AMODE0                         | 0-0              | 0-0             | MODE1           | MODE0 |  |  |  |  |  |

| bit 7                 |                                                                                                                                     | AWODET                                                                                                                                                                                                                                                                        | 7 WIODE0                       |                  |                 | MODET           | bit   |  |  |  |  |  |

| Lovende               |                                                                                                                                     |                                                                                                                                                                                                                                                                               |                                |                  |                 |                 |       |  |  |  |  |  |

| Legend:<br>R = Readab | lo hit                                                                                                                              | M - Mritabla                                                                                                                                                                                                                                                                  | hit.                           |                  | monted bit rec  | ud aa '0'       |       |  |  |  |  |  |

|                       |                                                                                                                                     | W = Writable                                                                                                                                                                                                                                                                  |                                | -                | mented bit, rea |                 |       |  |  |  |  |  |

| -n = Value a          | IT POR                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                              |                                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15                | CHEN: DMA                                                                                                                           | Channel Enabl                                                                                                                                                                                                                                                                 | e bit                          |                  |                 |                 |       |  |  |  |  |  |

|                       | 1 = Channel                                                                                                                         |                                                                                                                                                                                                                                                                               |                                |                  |                 |                 |       |  |  |  |  |  |

| bit 14                |                                                                                                                                     | <ul> <li>0 = Channel is disabled</li> <li>SIZE: DMA Data Transfer Size bit</li> </ul>                                                                                                                                                                                         |                                |                  |                 |                 |       |  |  |  |  |  |

|                       |                                                                                                                                     | 1 = Byte                                                                                                                                                                                                                                                                      |                                |                  |                 |                 |       |  |  |  |  |  |

|                       | 0 = Word                                                                                                                            |                                                                                                                                                                                                                                                                               |                                |                  |                 |                 |       |  |  |  |  |  |

| bit 13                | DIR: DMA Transfer Direction bit (source/destination bus select)                                                                     |                                                                                                                                                                                                                                                                               |                                |                  |                 |                 |       |  |  |  |  |  |

|                       |                                                                                                                                     | om RAM addre<br>om peripheral a                                                                                                                                                                                                                                               |                                | •                |                 |                 |       |  |  |  |  |  |

| bit 12                | <ul> <li>0 = Reads from peripheral address, writes to RAM address</li> <li>HALF: DMA Block Transfer Interrupt Select bit</li> </ul> |                                                                                                                                                                                                                                                                               |                                |                  |                 |                 |       |  |  |  |  |  |

|                       | 1 = Initiates i                                                                                                                     | nterrupt when                                                                                                                                                                                                                                                                 | half of the data               | a has been mo    |                 |                 |       |  |  |  |  |  |

| bit 11                |                                                                                                                                     | <ul> <li>0 = Initiates interrupt when all of the data has been moved</li> <li>NULLW: Null Data Peripheral Write Mode Select bit</li> </ul>                                                                                                                                    |                                |                  |                 |                 |       |  |  |  |  |  |

|                       |                                                                                                                                     | write to periph                                                                                                                                                                                                                                                               |                                |                  | e (DIR bit must | also be clear)  |       |  |  |  |  |  |

| bit 10-6              | Unimplemen                                                                                                                          | ted: Read as '                                                                                                                                                                                                                                                                | 0'                             |                  |                 |                 |       |  |  |  |  |  |

| bit 5-4               | AMODE<1:0                                                                                                                           | -: DMA Chann                                                                                                                                                                                                                                                                  | el Addressing                  | Mode Select b    | oits            |                 |       |  |  |  |  |  |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register                                                                                       |                                                                                                                                                                                                                                                                               | ressing mode<br>ut Post-Increm | nent mode        |                 |                 |       |  |  |  |  |  |

| bit 3-2               | Unimplemen                                                                                                                          | ted: Read as '                                                                                                                                                                                                                                                                | 0'                             |                  |                 |                 |       |  |  |  |  |  |

| bit 1-0               | -                                                                                                                                   | DMA Channel                                                                                                                                                                                                                                                                   |                                | de Select bits   |                 |                 |       |  |  |  |  |  |

|                       | 11 = One-Sho<br>10 = Continuo<br>01 = One-Sho                                                                                       | <ul> <li>11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)</li> <li>10 = Continuous, Ping-Pong modes are enabled</li> <li>01 = One-Shot, Ping-Pong modes are disabled</li> <li>00 = Continuous, Ping-Pong modes are disabled</li> </ul> |                                |                  |                 |                 |       |  |  |  |  |  |

## REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

| U-0              | U-0                                       | U-0              | U-0             | U-0                  | U-0              | U-0                | R/W-0   |  |

|------------------|-------------------------------------------|------------------|-----------------|----------------------|------------------|--------------------|---------|--|

| _                | —                                         | —                |                 | —                    | —                | —                  | PLLDIV8 |  |

| bit 15           |                                           |                  |                 |                      |                  |                    | bit 8   |  |

|                  |                                           |                  |                 |                      |                  |                    |         |  |

| R/W-0            | R/W-0                                     | R/W-1            | R/W-1           | R/W-0                | R/W-0            | R/W-0              | R/W-0   |  |

| PLLDIV7          | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3              | PLLDIV2          | PLLDIV1            | PLLDIV0 |  |

| bit 7            |                                           |                  |                 |                      |                  |                    | bit 0   |  |

|                  |                                           |                  |                 |                      |                  |                    |         |  |

| Legend:          |                                           |                  |                 |                      |                  |                    |         |  |

| R = Readable bit |                                           | W = Writable     | bit             | U = Unimpler         | mented bit, read | d as '0'           |         |  |

| -n = Value at P  | OR                                        | '1' = Bit is set |                 | '0' = Bit is cleared |                  | x = Bit is unknown |         |  |

|                  |                                           |                  |                 |                      |                  |                    |         |  |

| bit 15-9         | Unimplemen                                | ted: Read as '   | 0'              |                      |                  |                    |         |  |

| bit 8-0          | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted        | as 'M', PLL mul  | tiplier)           |         |  |

|                  | 111111111 =                               | = 513            |                 |                      |                  |                    |         |  |

|                  | •                                         |                  |                 |                      |                  |                    |         |  |

|                  | •                                         |                  |                 |                      |                  |                    |         |  |

|                  | •                                         |                  |                 |                      |                  |                    |         |  |

|                  | 000110000 =                               | = 50 (default)   |                 |                      |                  |                    |         |  |

|                  |                                           |                  |                 |                      |                  |                    |         |  |

|                  | •                                         |                  |                 |                      |                  |                    |         |  |

|                  | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                      |                  |                    |         |  |

|                  |                                           |                  |                 |                      |                  |                    |         |  |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

## 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                              | R/W-0         | R/W-0           | R/W-0 |  |  |

|-----------------|------------|-------------------------------------|-------|------------------------------------|---------------|-----------------|-------|--|--|

| —               | —          |                                     |       | RP57                               | R<5:0>        |                 |       |  |  |

| bit 15          |            |                                     |       |                                    |               |                 | bit 8 |  |  |

|                 |            |                                     |       |                                    |               |                 |       |  |  |

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                              | R/W-0         | R/W-0           | R/W-0 |  |  |

| _               | —          |                                     |       | RP56                               | R<5:0>        |                 |       |  |  |

| bit 7           |            |                                     |       |                                    |               |                 | bit 0 |  |  |

|                 |            |                                     |       |                                    |               |                 |       |  |  |

| Legend:         |            |                                     |       |                                    |               |                 |       |  |  |

| R = Readable I  | bit        | W = Writable                        | bit   | U = Unimplemented bit, read as '0' |               |                 |       |  |  |

| -n = Value at P | OR         | '1' = Bit is set                    | :     | '0' = Bit is clea                  | ared          | x = Bit is unkr | iown  |  |  |

|                 |            |                                     |       |                                    |               |                 |       |  |  |

| bit 15-14       | Unimplemen | ted: Read as '                      | 0'    |                                    |               |                 |       |  |  |

| bit 13-8        |            | : Peripheral Ou<br>-3 for periphera |       | is Assigned to<br>mbers)           | RP57 Output F | Pin bits        |       |  |  |

| bit 7-6         | Unimplemen | ted: Read as '                      | 0'    |                                    |               |                 |       |  |  |

## REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

## REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|--|--|

| —      | —   |       | RP97R<5:0> |       |       |       |       |  |  |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |  |  |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

## 13.2 Timer Control Registers

| R/W-0         | U-0                                                                                                                                     | R/W-0                                            | U-0            | U-0              | U-0             | U-0             | U-0   |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| TON           |                                                                                                                                         | TSIDL                                            | —              | _                |                 |                 | _     |  |  |  |  |  |

| bit 15        |                                                                                                                                         |                                                  |                |                  |                 |                 | bit 8 |  |  |  |  |  |

|               |                                                                                                                                         |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-0                                                                                                                                   | R/W-0                                            | R/W-0          | R/W-0            | U-0             | R/W-0           | U-0   |  |  |  |  |  |

| _             | TGATE                                                                                                                                   | TCKPS1                                           | TCKPS0         | T32              | _               | TCS             | _     |  |  |  |  |  |

| bit 7         |                                                                                                                                         |                                                  |                |                  |                 |                 | bit ( |  |  |  |  |  |

| <u> </u>      |                                                                                                                                         |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

| Legend:       | - 1-:4                                                                                                                                  |                                                  |                | II II.           |                 |                 |       |  |  |  |  |  |

| R = Readable  |                                                                                                                                         | W = Writable                                     |                | -                | nented bit, rea |                 |       |  |  |  |  |  |

| -n = Value at | PUR                                                                                                                                     | '1' = Bit is set                                 |                | '0' = Bit is cle | areo            | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15        | TON: Timerx                                                                                                                             | On hit                                           |                |                  |                 |                 |       |  |  |  |  |  |

|               | When T32 = 2                                                                                                                            |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Starts 32-                                                                                                                          | 1 = Starts 32-bit Timerx/y                       |                |                  |                 |                 |       |  |  |  |  |  |

|               | •                                                                                                                                       | 0 = Stops 32-bit Timerx/y                        |                |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                                         | <u>When T32 = 0:</u><br>1 = Starts 16-bit Timerx |                |                  |                 |                 |       |  |  |  |  |  |

|               | 0 = Stops 16-                                                                                                                           |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

| bit 14        | Unimplemen                                                                                                                              | Unimplemented: Read as '0'                       |                |                  |                 |                 |       |  |  |  |  |  |

| bit 13        | TSIDL: Timer                                                                                                                            | x Stop in Idle M                                 | lode bit       |                  |                 |                 |       |  |  |  |  |  |

|               | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                                         | -                                                |                | ode              |                 |                 |       |  |  |  |  |  |

| bit 12-7      | Unimplemented: Read as '0'                                                                                                              |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

| bit 6         | <b>TGATE:</b> Timerx Gated Time Accumulation Enable bit                                                                                 |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

|               | <u>When TCS = 1:</u><br>This bit is ignored.                                                                                            |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

|               | When TCS = $0$ :                                                                                                                        |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = Gated time accumulation is enabled                                                                                                  |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                                         | 0 = Gated time accumulation is disabled          |                |                  |                 |                 |       |  |  |  |  |  |

| bit 5-4       |                                                                                                                                         | : Timerx Input                                   | Clock Prescal  | e Select bits    |                 |                 |       |  |  |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                                                                                                                 | 11 = 1:256                                       |                |                  |                 |                 |       |  |  |  |  |  |

|               | 01 = 1:8                                                                                                                                |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

|               | 00 = 1:1                                                                                                                                |                                                  |                |                  |                 |                 |       |  |  |  |  |  |

| bit 3         | T32: 32-Bit Ti                                                                                                                          | T32: 32-Bit Timer Mode Select bit                |                |                  |                 |                 |       |  |  |  |  |  |

|               |                                                                                                                                         | nd Timery form<br>nd Timery act as               |                |                  |                 |                 |       |  |  |  |  |  |

| bit 2         | Unimplemen                                                                                                                              | ted: Read as '                                   | )'             |                  |                 |                 |       |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                                                                                             | Clock Source S                                   | elect bit      |                  |                 |                 |       |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                                                                                                       | clock is from pir<br>lock (FP)                   | n, TxCK (on th | ne rising edge)  |                 |                 |       |  |  |  |  |  |

| bit 0         | Unimplomon                                                                                                                              | ted: Read as '                                   | ı'             |                  |                 |                 |       |  |  |  |  |  |

# REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

## REGISTER 17-1: QEI1CON: QEI1 CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <pre>111 = 1:128 prescale value<br/>110 = 1:64 prescale value<br/>101 = 1:32 prescale value<br/>100 = 1:16 prescale value<br/>011 = 1:8 prescale value<br/>010 = 1:4 prescale value<br/>001 = 1:2 prescale value<br/>000 = 1:1 prescale value</pre>                                                                          |

| bit 3   | <b>CNTPOL:</b> Position and Index Counter/Timer Direction Select bit<br>1 = Counter direction is negative unless modified by external up/down signal                                                                                                                                                                         |

|         | <ul> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                                                                                                             |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                                     |

- 2: When CCM<1:0> = 00, and QEA and QEB values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset. QEA/QEB signals used for the index match have swap and polarity values applied, as determined by the SWPAB and QEAPOL/QEBPOL bits.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

## REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|----------------------------------------------------------------------------|-------|----------------|-------|--------------|-----------------|----------|-------|

|                                                                            |       |                | INTTM | R<31:24>     |                 |          |       |

| bit 15                                                                     |       |                |       |              |                 |          | bit 8 |

|                                                                            |       |                |       |              |                 |          |       |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                                                                            |       |                | INTTM | R<23:16>     |                 |          |       |

| bit 7                                                                      |       |                |       |              |                 |          | bit 0 |

|                                                                            |       |                |       |              |                 |          |       |

| Legend:                                                                    |       |                |       |              |                 |          |       |

| R = Readable                                                               | bit   | W = Writable b | oit   | U = Unimplem | nented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                |       |              |                 | nown     |       |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

## REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|----------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|

|                                                                      |       |       | INTTM | IR<15:8>                           |       |       |       |  |

| bit 15                                                               |       |       |       |                                    |       |       | bit 8 |  |

|                                                                      |       |       |       |                                    |       |       |       |  |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                                                      |       |       | INTT  | /IR<7:0>                           |       |       |       |  |

| bit 7                                                                |       |       |       |                                    |       |       | bit 0 |  |

|                                                                      |       |       |       |                                    |       |       |       |  |

| Legend:                                                              |       |       |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit                                    |       |       |       | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |       |       |       | x = Bit is unkr                    | nown  |       |       |  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

#### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

## Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

#### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

#### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

## 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

| FLTEN7  | FLTEN6  | FLTEN5  | FLTEN4  | FLTEN3  | FLTEN2  | FLTEN1 | FLTEN0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

|         |         |         |         |         |         |        |        |

| Legend: |         |         |         |         |         |        |        |

### REGISTER 21-11: CxFEN1: ECANx ACCEPTANCE FILTER ENABLE REGISTER 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits