Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp204-e-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

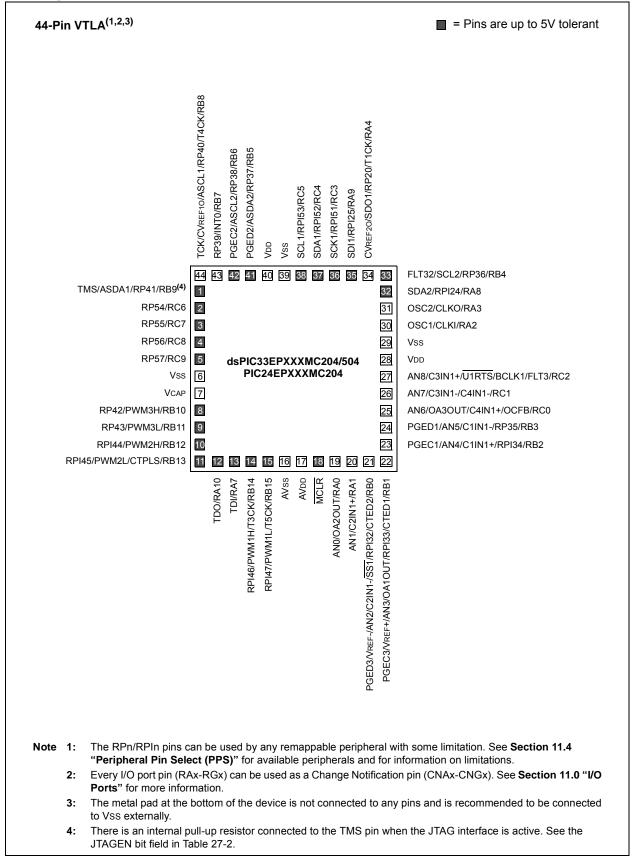

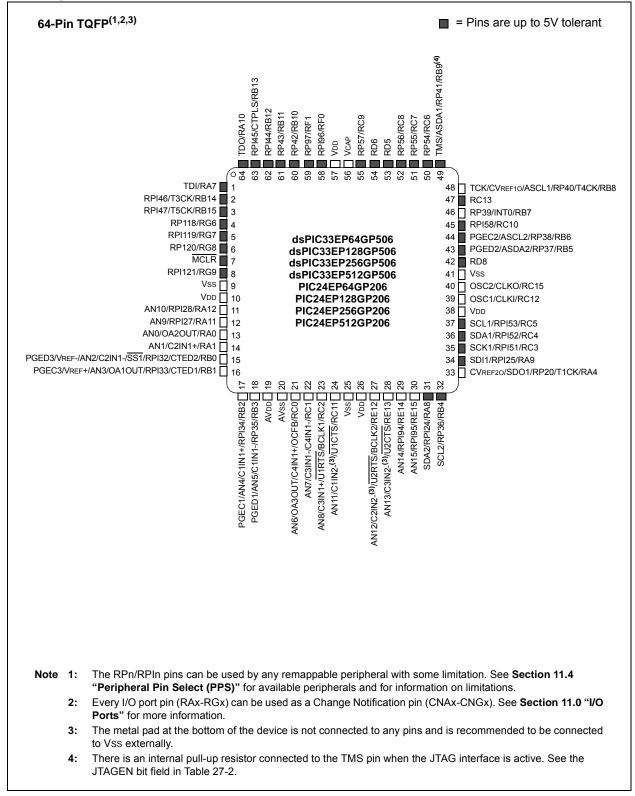

# Pin Diagrams (Continued)

# **Pin Diagrams (Continued)**

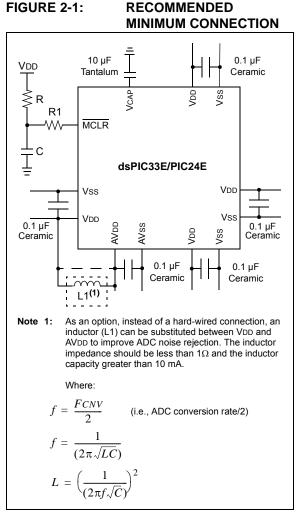

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

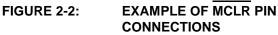

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

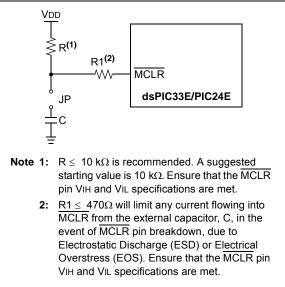

# FIGURE 2-7: INTERLEAVED PFC

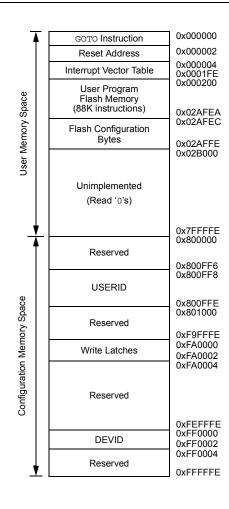

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

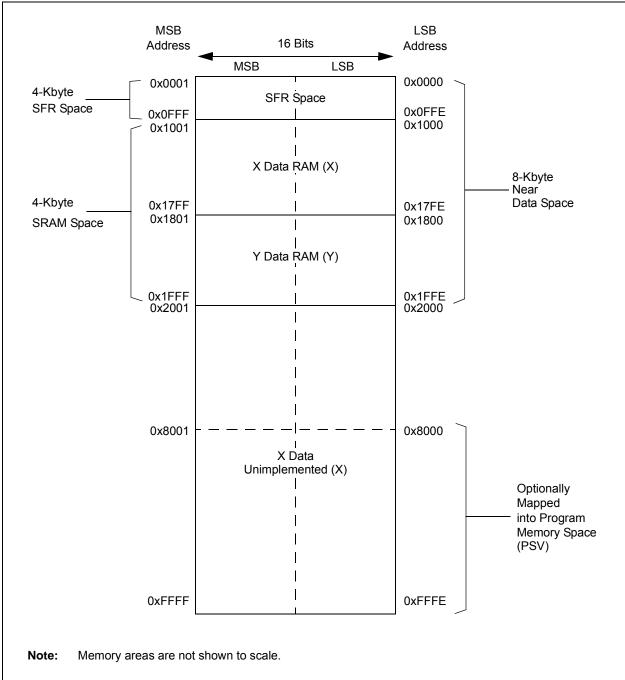

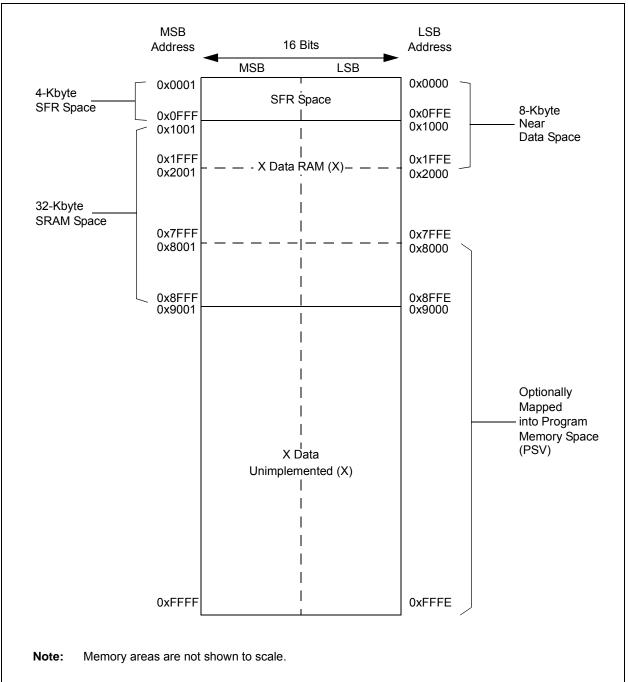

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

# 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

# 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

# REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

# 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | U-0                                                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|

|                                              | _                                                                                                                                                                            | _                                                                                                                                                                                                                            | _                                                                                                                                | _                                 | _                        | _                           | _    |

| bit 15                                       |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

|                                              |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | R/W-0                                                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |

| _                                            | -                                                                                                                                                                            | _                                                                                                                                                                                                                            | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup>                                 | PTGMD                             | _                        | _                           | _    |

| bit 7                                        |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                              | W = Writable<br>'1' = Bit is set                                                                                                                                                                                             |                                                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |

| bit 15-5<br>bit 4                            | DMA0MD: DN<br>1 = DMA0 mo<br>0 = DMA0 mo<br>DMA1MD: DN<br>1 = DMA1 mo<br>0 = DMA1 mo<br>DMA2MD: DN<br>1 = DMA2 mo<br>0 = DMA2 mo<br>DMA3MD: DN<br>1 = DMA3 mo<br>0 = DMA3 mo | ted: Read as '<br>MA0 Module Di<br>odule is disable<br>odule is enable<br>MA1 Module Di<br>odule is disable<br>MA2 Module Di<br>odule is disable<br>odule is enable<br>MA3 Module Di<br>odule is disable<br>odule is disable | sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d |                                   |                          |                             |      |

| bit 3                                        |                                                                                                                                                                              | Module Disat<br>ule is disabled<br>ule is enabled                                                                                                                                                                            | ole bit                                                                                                                          |                                   |                          |                             |      |

| bit 2-0                                      | Unimplement                                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                               | 0'                                                                                                                               |                                   |                          |                             |      |

| Note 1: T                                    | his single bit ena                                                                                                                                                           | ables and disal                                                                                                                                                                                                              | oles all four DM                                                                                                                 | A channels.                       |                          |                             |      |

# REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           | 101 0101                                         | —                | _              |

| 010 1001                                         | I/O              | RP41           | 101 0110                                         | —                | —              |

| 010 1010                                         | I/O              | RP42           | 101 0111                                         | —                | —              |

| 010 1011                                         | I/O              | RP43           | 101 1000                                         | —                | —              |

| 010 1100                                         | I                | RPI44          | 101 1001                                         | —                | —              |

| 101 1010                                         | —                | _              | 110 1101                                         | —                | _              |

| 101 1011                                         | —                | —              | 110 1110                                         | —                | —              |

| 101 1100                                         | —                | —              | 110 1111                                         | —                | —              |

| 101 1101                                         | —                | —              | 111 0000                                         | —                | _              |

| 101 1110                                         | I                | RPI94          | 111 0001                                         | —                | —              |

| 101 1111                                         | I                | RP195          | 111 0010                                         | —                | —              |

| 110 0000                                         | I                | RPI96          | 111 0011                                         | —                | —              |

| 110 0001                                         | I/O              | RP97           | 111 0100                                         | —                | —              |

| 110 0010                                         | —                | —              | 111 0101                                         | —                | —              |

| 110 0011                                         | —                | _              | 111 0110                                         | I/O              | RP118          |

| 110 0100                                         | —                | —              | 111 0111                                         | I                | RPI119         |

| 110 0101                                         |                  |                | 111 1000                                         | I/O              | RP120          |

| 110 0110                                         | _                | _              | 111 1001                                         | Ι                | RPI121         |

| 110 0111                                         |                  |                | 111 1010                                         |                  |                |

| 110 1000                                         | —                |                | 111 1011                                         | —                | _              |

| 110 1001                                         | _                | _              | 111 1100                                         | —                |                |

| 110 1010                                         |                  |                | 111 1101                                         |                  |                |

| 110 1011                                         |                  |                | 111 1110                                         | —                |                |

| 110 1100                                         | —                |                | 111 1111                                         | —                | _              |

# TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

# REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                                                     |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

# REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     | —     | —     | —          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

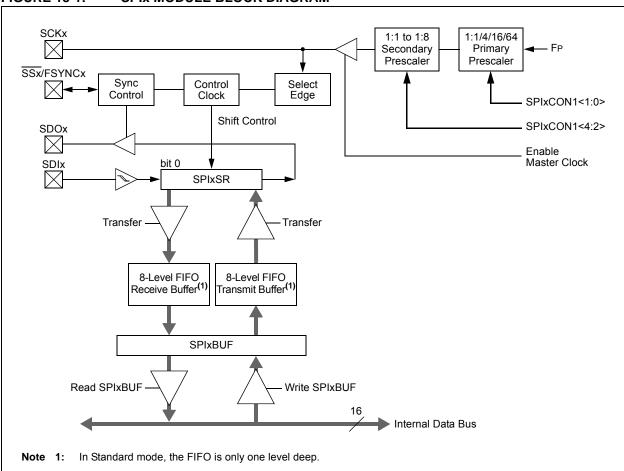

## FIGURE 18-1: SPIx MODULE BLOCK DIAGRAM

# REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |                                         |       |                                    |       |        |       |  |

|------------------------------------|-------|-----------------------------------------|-------|------------------------------------|-------|--------|-------|--|

|                                    | R/W-0 | R/W-0                                   | R/W-0 | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F7BF  | °<3:0>                                  |       |                                    | F6BF  | P<3:0> |       |  |

| bit 15                             |       |                                         |       |                                    |       |        | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

| F5BP<3:0>                          |       |                                         |       | F4BP<3:0>                          |       |        |       |  |

| bit 7                              |       |                                         |       |                                    |       |        | bit 0 |  |

| Legend:                            |       |                                         |       |                                    |       |        |       |  |

| R = Readable bi                    | t     | W = Writable                            | bit   | U = Unimplemented bit, read as '0' |       |        |       |  |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |                                    | nown  |        |       |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

# REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0                             | R/W-0                                              | R/W-0                                                                                          | R/W-0                              | R/W-0                | R/W-0          | R/W-0              | R/W-0 |

|-----------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------|----------------------|----------------|--------------------|-------|

| F11BP<3:0>                        |                                                    |                                                                                                | F10BP<3:0>                         |                      |                |                    |       |

| bit 15                            |                                                    |                                                                                                |                                    |                      |                |                    | bit 8 |

| R/W-0                             | R/W-0                                              | R/W-0                                                                                          | R/W-0                              | R/W-0                | R/W-0          | R/W-0              | R/W-0 |

|                                   | F9BP                                               | <3:0>                                                                                          |                                    | F8BP<3:0>            |                |                    |       |

| bit 7                             |                                                    |                                                                                                |                                    |                      |                |                    | bit 0 |

| Legend:                           |                                                    |                                                                                                |                                    |                      |                |                    |       |

| R = Readable bit W = Writable bit |                                                    |                                                                                                | U = Unimplemented bit, read as '0' |                      |                |                    |       |

| -n = Value at POR                 |                                                    | '1' = Bit is set                                                                               |                                    | '0' = Bit is cleared |                | x = Bit is unknown |       |

| bit 15-12                         | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | : RX Buffer Ma<br>hits received in<br>hits received in<br>hits received in<br>hits received in | n RX FIFO bu<br>n RX Buffer 1      | iffer<br>4           |                |                    |       |

| bit 11-8                          | F10BP<3:0>                                         | : RX Buffer Ma                                                                                 | sk for Filter 1                    | 0 bits (same val     | ues as bits<1  | 5:12>)             |       |

| bit 7-4                           | F9BP<3:0>:                                         | RX Buffer Mas                                                                                  | k for Filter 9 b                   | oits (same value     | s as bits<15:1 | 2>)                |       |

| bit 3-0                           | F8BP<3:0>:                                         | RX Buffer Mas                                                                                  | k for Filter 8 k                   | oits (same value     | s as bits<15:1 | 2>)                |       |

|                                   |                                                    |                                                                                                |                                    |                      |                |                    |       |

© 2011-2013 Microchip Technology Inc.

| Base<br>Instr<br># Assembly<br>Mnemonic |        | Assembly Syntax |                                                  | Description                               | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|-----------------------------------------|--------|-----------------|--------------------------------------------------|-------------------------------------------|---------------|-------------------------------|--------------------------|

| 46                                      | MOV    | MOV             | f,Wn                                             | Move f to Wn                              |               | 1                             | None                     |

|                                         |        | MOV             | f                                                | Move f to f                               | 1             | 1                             | None                     |

|                                         |        | MOV             | f,WREG                                           | Move f to WREG                            | 1             | 1                             | None                     |

|                                         |        | MOV             | #litl6,Wn                                        | Move 16-bit literal to Wn                 | 1             | 1                             | None                     |

|                                         |        | MOV.b           | #lit8,Wn                                         | Move 8-bit literal to Wn                  | 1             | 1                             | None                     |

|                                         |        | MOV             | Wn,f                                             | Move Wn to f                              | 1             | 1                             | None                     |

|                                         |        | MOV             | Wso,Wdo                                          | Move Ws to Wd                             | 1             | 1                             | None                     |

|                                         |        | MOV             | WREG, f                                          | Move WREG to f                            | 1             | 1                             | None                     |

|                                         |        | MOV.D           | Wns,Wd                                           | Move Double from W(ns):W(ns + 1) to<br>Wd | 1             | 2                             | None                     |

|                                         |        | MOV.D           | Ws , Wnd                                         | Move Double from Ws to W(nd +<br>1):W(nd) | 1             | 2                             | None                     |

| 47                                      | MOVPAG | MOVPAG          | #lit10,DSRPAG                                    | Move 10-bit literal to DSRPAG             | 1             | 1                             | None                     |

|                                         |        | MOVPAG          | #lit9,DSWPAG                                     | Move 9-bit literal to DSWPAG              | 1             | 1                             | None                     |

|                                         |        | MOVPAG          | #lit8,TBLPAG                                     | Move 8-bit literal to TBLPAG              | 1             | 1                             | None                     |

|                                         |        | MOVPAG          | Ws, DSRPAG                                       | Move Ws<9:0> to DSRPAG                    | 1             | 1                             | None                     |

|                                         |        | MOVPAG          | Ws, DSWPAG                                       | Move Ws<8:0> to DSWPAG                    | 1             | 1                             | None                     |

|                                         |        | MOVPAG          | Ws, TBLPAG                                       | Move Ws<7:0> to TBLPAG                    | 1             | 1                             | None                     |

| 48                                      | MOVSAC | MOVSAC          | Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>             | Prefetch and store accumulator            | 1             | 1                             | None                     |

| 49                                      | MPY    | MPY             | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Multiply Wm by Wn to Accumulator          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                                         |        | MPY             | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd <sup>(1)</sup>           | Square Wm to Accumulator                  | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 50                                      | MPY.N  | MPY.N           | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                       | -(Multiply Wm by Wn) to Accumulator       | 1             | 1                             | None                     |

| 51                                      | MSC    | MSC             | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Subtract from Accumulator    | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

# TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

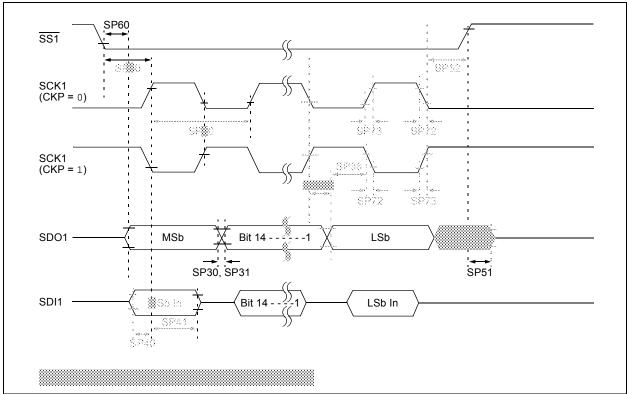

# TABLE 30-40:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |

|--------------------|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCK2 Input Frequency                    | —                                                                                                                                                                                                                                                                                       | —                   | 11   | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCK2 Input Fall Time                            | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP73               | TscR                  | SCK2 Input Rise Time                            | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                                                                                                                                                                                                                                                                     | —                   | _    | ns    |                                |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                                                                                                                                                                                                                                                                      | —                   | 50   | ns    | (Note 4)                       |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                                                                                                                                                                                                                                                            | —                   |      | ns    | (Note 4)                       |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

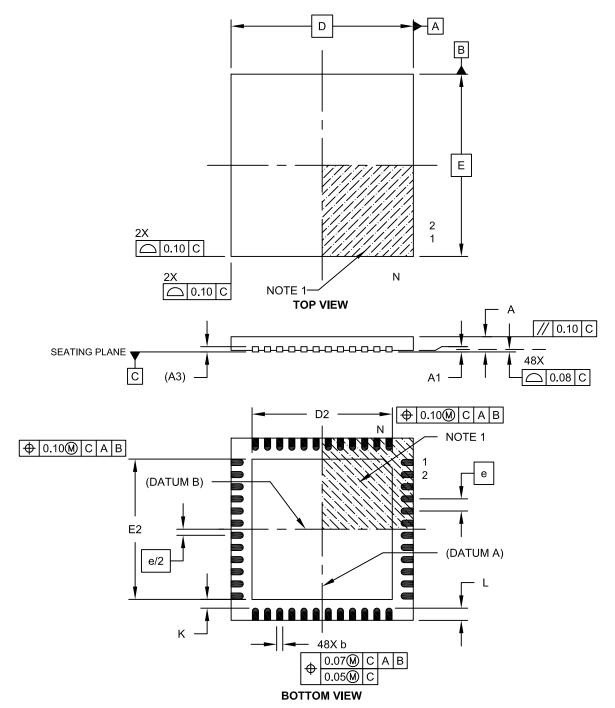

## 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

NOTES: