Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

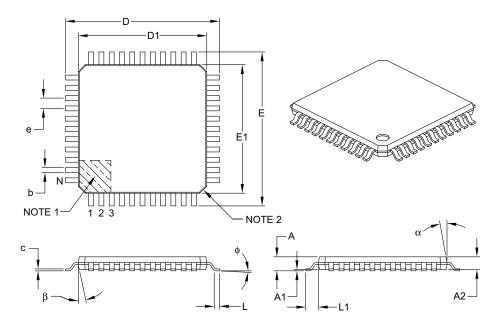

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VFTLA Exposed Pad                                                          |

| Supplier Device Package    | 44-VTLA (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp204-e-tl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:         PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |     |                                                                                  |  |  |  |  |  |  |

|--------------------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name <sup>(4)</sup>                                | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                      |  |  |  |  |  |  |

| U2CTS                                                  | Ι           | ST             | No  | UART2 Clear-To-Send.                                                             |  |  |  |  |  |  |

| U2RTS                                                  | 0           | —              | No  | UART2 Ready-To-Send.                                                             |  |  |  |  |  |  |

| U2RX                                                   | Ι           | ST             | Yes | UART2 receive.                                                                   |  |  |  |  |  |  |

| U2TX                                                   | 0           | —              | Yes | UART2 transmit.                                                                  |  |  |  |  |  |  |

| BCLK2                                                  | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                                       |  |  |  |  |  |  |

| SCK1                                                   | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                                  |  |  |  |  |  |  |

| SDI1                                                   | I           | ST             | No  | SPI1 data in.                                                                    |  |  |  |  |  |  |

| SDO1                                                   | 0           | —              | No  | SPI1 data out.                                                                   |  |  |  |  |  |  |

| SS1                                                    | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                                   |  |  |  |  |  |  |

| SCK2                                                   | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                                  |  |  |  |  |  |  |

| SDI2                                                   | I           | ST             | Yes | SPI2 data in.                                                                    |  |  |  |  |  |  |

| SDO2                                                   | 0           | _              | Yes | SPI2 data out.                                                                   |  |  |  |  |  |  |

| SS2                                                    | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                                   |  |  |  |  |  |  |

| SCL1                                                   | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                                  |  |  |  |  |  |  |

| SDA1                                                   | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                                   |  |  |  |  |  |  |

| ASCL1                                                  | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.                        |  |  |  |  |  |  |

| ASDA1                                                  | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.                         |  |  |  |  |  |  |

| SCL2                                                   | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                                  |  |  |  |  |  |  |

| SDA2                                                   | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                                   |  |  |  |  |  |  |

| ASCL2                                                  | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.                        |  |  |  |  |  |  |

| ASDA2                                                  | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.                         |  |  |  |  |  |  |

| TMS <sup>(5)</sup>                                     | Ι           | ST             | No  | JTAG Test mode select pin.                                                       |  |  |  |  |  |  |

| TCK                                                    | Ι           | ST             | No  | JTAG test clock input pin.                                                       |  |  |  |  |  |  |

| TDI                                                    | I           | ST             | No  | JTAG test data input pin.                                                        |  |  |  |  |  |  |

| TDO                                                    | 0           | _              | No  | JTAG test data output pin.                                                       |  |  |  |  |  |  |

| C1RX <sup>(2)</sup>                                    | Ι           | ST             | Yes | ECAN1 bus receive pin.                                                           |  |  |  |  |  |  |

| C1TX <sup>(2)</sup>                                    | 0           | _              | Yes | ECAN1 bus transmit pin.                                                          |  |  |  |  |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>              | Ι           | ST             | Yes | PWM Fault Inputs 1 and 2.                                                        |  |  |  |  |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>              | Ι           | ST             | No  | PWM Fault Inputs 3 and 4.                                                        |  |  |  |  |  |  |

| FLT32 <sup>(1,3)</sup>                                 | Ι           | ST             | No  | PWM Fault Input 32 (Class B Fault).                                              |  |  |  |  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                           | Ι           | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                                   |  |  |  |  |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                             | 0           | —              | No  | PWM Low Outputs 1 through 3.                                                     |  |  |  |  |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                             | 0           | —              | No  | PWM High Outputs 1 through 3.                                                    |  |  |  |  |  |  |

| SYNCI1 <sup>(1)</sup>                                  | Ι           | ST             |     | PWM Synchronization Input 1.                                                     |  |  |  |  |  |  |

| SYNCO1 <sup>(1)</sup>                                  | 0           |                | Yes | PWM Synchronization Output 1.                                                    |  |  |  |  |  |  |

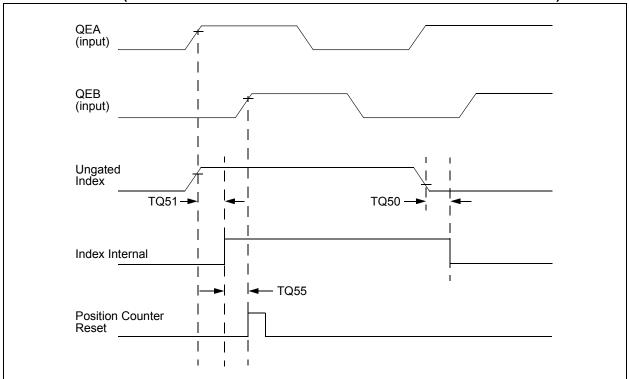

| INDX1 <sup>(1)</sup>                                   | Ι           | ST             | Yes | Quadrature Encoder Index1 pulse input.                                           |  |  |  |  |  |  |

| HOME1 <sup>(1)</sup>                                   | Ι           | ST             | Yes | Quadrature Encoder Home1 pulse input.                                            |  |  |  |  |  |  |

| QEA1 <sup>(1)</sup>                                    | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |  |  |  |  |  |  |

| QEB1 <sup>(1)</sup>                                    | ,           | ст             | Vee | external clock/gate input in Timer mode.                                         |  |  |  |  |  |  |

|                                                        | Ι           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |  |  |  |  |  |  |

| CNTCMP1 <sup>(1)</sup>                                 | 0           |                | Yes | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |  |  |  |  |  |  |

|                                                        | 0           |                | 162 |                                                                                  |  |  |  |  |  |  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7 | Bit 6        | Bit 5           | Bit 4         | Bit 3    | Bit 2       | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|--------|--------|--------|----------------|--------|-------|--------------|-----------------|---------------|----------|-------------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF        | T3IF   | T2IF  | OC2IF        | IC2IF           | DMA0IF        | T1IF     | OC1IF       | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF          | DMA2IF | _     | _            | _               | INT1IF        | CNIF     | CMIF        | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _      |        |        |                | _      | _     | IC4IF        | IC3IF           | DMA3IF        | C1IF     | C1RXIF      | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _      |        | QEI1IF | PSEMIF         | _      | _     | _            | _               | _             | _        | MI2C2IF     | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |        |        |        |                | _      | _     | C1TXIF       | _               | _             | CRCIF    | U2EIF       | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |        |        |        |                | _      | _     | _            | _               | _             | _        | _           | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |        |        |        |                | _      | _     | _            | _               | _             | _        | _           | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |        |        |        |                | _      | _     | _            | _               | _             | _        | _           | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _      | _      |        |                | _      | —     | PTG3IF       | PTG2IF          | PTG1IF        | PTG0IF   | PTGWDTIF    | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE        | T3IE   | T2IE  | OC2IE        | IC2IE           | DMA0IE        | T1IE     | OC1IE       | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE          | DMA2IE | —     | _            | —               | INT1IE        | CNIE     | CMIE        | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _      | _      |        | _              | _      | _     | IC4IE        | IC3IE           | <b>DMA3IE</b> | C1IE     | C1RXIE      | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _      | _      | QEI1IE | PSEMIE         | _      | _     | _            | _               | _             | _        | MI2C2IE     | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      |        |        | _              | _      | _     | C1TXIE       | _               | _             | CRCIE    | U2EIE       | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _      | _      |        | _              | _      | _     | _            | _               | _             | _        | _           | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _      | _      |        | _              | _      | _     | _            | _               | _             | _        | _           | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _      | _      |        | _              | _      | _     | _            | _               | _             | _        | _           | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      |        | _              | _      | _     | _            | _               | _             | _        | _           | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _      | _      |        | _              | _      | _     | PTG3IE       | PTG2IE          | PTG1IE        | PTG0IE   | PTGWDTIE    | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0      | >      | _     |              | IC1IP<2:0>      |               | _        |             | INT0IP<2:0>  |         | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0      | >      | _     |              | IC2IP<2:0>      |               | _        | [           | DMA0IP<2:0>  |         | 4444         |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >      | _      |        | SPI1IP<2:0     | )>     | _     |              | SPI1EIP<2:0     | >             |          |             | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _      | _      | C      | MA1IP<2:       | 0>     | _     |              | AD1IP<2:0>      |               |          |             | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0       | >      | _     |              | MI2C1IP<2:0     | >             |          | 5           | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _      | _      |        | _              | _      | _     | _            | _               | _             |          |             | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0      | >      | _     |              | OC3IP<2:0>      |               |          | [           | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:      | 0>     | _     |              | INT2IP<2:0>     |               |          |             | T5IP<2:0>    |         | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |        | _      | C      | 2:<br>2:<br>2: | 0>     | _     |              | SPI2IP<2:0>     |               |          | 5           | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0      | >      | _     | IC3IP<2:0>   |                 |               | [        | DMA3IP<2:0> |              | 0444    |              |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | 112C2IP<2:     | 0>     | _     | SI2C2IP<2:0> |                 | _             | _        | _           | _            | 0440    |              |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:(     | )>     | _     | PSEMIP<2:0>  |                 | _             | _        | _           | _            | 0440    |              |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0      |        | _     | U1EIP<2:0>   |                 | _             | <u> </u> | _           | _            | 4440    |              |

| IPC17        | 0862  | _      | _      | _          | _      | _      |        | C1TXIP<2:      |        | _     | _            | _               | —             | _        | _           | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            | _      | _      |        |                |        |       |              | L<br>CTMUIP<2:0 | >             |          | <u> </u>    | _            | _       | 0040         |

# TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

#### TABLE 4-24: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                  | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8    | Bit 7        | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|-------------------------|--------|--------|--------|-----------|-------|----------|--------------|--------|---------|-------|---------|-----------|-------|-------|---------------|

| CRCCON1   | 0640  | CRCEN  | —                       | CSIDL  |        | V      | WORD<4:0  | )>    |          | CRCFUL       | CRCMPT | CRCISEL | CRCGO | LENDIAN | _         | _     | —     | 0000          |

| CRCCON2   | 0642  |        | _                       | _      |        | D      | WIDTH<4:0 | )>    |          | _            | -      | _       |       | F       | PLEN<4:0> |       |       | 0000          |

| CRCXORL   | 0644  |        | X<15:1>0                |        |        |        |           |       |          |              | 0000   |         |       |         |           |       |       |               |

| CRCXORH   | 0646  |        |                         |        |        |        |           |       | X·       | <31:16>      |        |         |       |         |           |       |       | 0000          |

| CRCDATL   | 0648  |        |                         |        |        |        |           |       | CRC Data | Input Low V  | Vord   |         |       |         |           |       |       | 0000          |

| CRCDATH   | 064A  |        |                         |        |        |        |           |       | CRC Data | Input High \ | Vord   |         |       |         |           |       |       | 0000          |

| CRCWDATL  | 064C  |        | CRC Result Low Word     |        |        |        |           |       |          |              | 0000   |         |       |         |           |       |       |               |

| CRCWDATH  | 064E  |        | CRC Result High Word 00 |        |        |        |           |       |          |              |        | 0000    |       |         |           |       |       |               |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC202/502 AND PIC24EPXXXGP/MC202 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5        | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|--------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | —      | —      |        |            | RP35F  | <5:0>  |       |       | _     | _     |              |       | RP20F | ₹<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       | _     | Ι     | RP36R<5:0>   |       |       |        |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |            | RP39F  | <5:0>  |       |       | _     | Ι     | RP38R<5:0>   |       |       |        |       | 0000  |               |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0> |        |        |       |       | _     | Ι     | RP40R<5:0>   |       |       |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        |            | RP43F  | <5:0>  |       |       | —     | _     | – RP42R<5:0> |       |       |        |       | 0000  |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC203/503 AND PIC24EPXXXGP/MC203 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | —      |        |        | RP35F  | R<5:0> |       |       | _     | _     |       |       | RP20F | २<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |        | RP37F  | ۲<5:0> |       |       | _     | _     |       |       | RP36F | २<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |        | RP39F  | २<5:0> |       |       | _     | —     |       |       | RP38F | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |        | RP41F  | २<5:0> |       |       | _     | —     |       |       | RP40F | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43F  | ۲<5:0> |       |       | _     | _     |       |       | RP42F | २<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      | _      | _      | _      | _      |       | _     | _     | _     | _     | _     | _     | —      |       |       | 0000          |

| RPOR6        | 068C  | _      | —      | —      | _      | _      | _      | _     | —     | _     | _     |       |       | RP56F | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0         | R/W-0                                  | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|----------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                               | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                        |                                        |               |                       |                   |                  | bit 8         |

|               |                                        | DANIO                                  | DAA/ O        | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                        | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                    | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                        |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                        |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                               | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                 | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                        |                                        |               |                       |                   |                  |               |

| bit 15        | •                                      | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                        | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                      | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                        | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                        | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                      | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                      | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                        | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                        | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                        | ted: Read as '                         | -             | ,,                    | 5                 |                  |               |

| bit 9         | CM: Configur                           | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                          | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                           | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                      | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                           | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                        | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                            | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                        | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                             | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di          |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                             | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                        | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir  | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0          | U-0          | U-0             | U-0              | U-0              | U-0              | U-0                | U-0   |  |

|--------------|--------------|-----------------|------------------|------------------|------------------|--------------------|-------|--|

|              | —            | _               | —                | —                | —                | —                  | _     |  |

| bit 15       |              |                 |                  |                  |                  |                    | bit 8 |  |

|              |              |                 |                  |                  |                  |                    |       |  |

| U-0          | U-0          | R/W-0           | R/W-0            | U-0              | U-0              | U-0                | U-0   |  |

| —            | —            | DAE             | DOOVR            | —                | —                | —                  | —     |  |

| bit 7        |              |                 |                  |                  |                  |                    | bit 0 |  |

|              |              |                 |                  |                  |                  |                    |       |  |

| Legend:      |              |                 |                  |                  |                  |                    |       |  |

| R = Readab   | le bit       | W = Writable    | bit              | U = Unimplei     | mented bit, read | as '0'             |       |  |

| -n = Value a | It POR       | '1' = Bit is se | t                | '0' = Bit is cle | eared            | x = Bit is unknown |       |  |

|              |              |                 |                  |                  |                  |                    |       |  |

| bit 15-6     | Unimplemen   | ted: Read as    | '0'              |                  |                  |                    |       |  |

| bit 5        | DAE: DMA A   | ddress Error S  | Soft Trap Status | s bit            |                  |                    |       |  |

|              | 1 = DMA add  | ress error soft | trap has occur   | red              |                  |                    |       |  |

|              | 0 = DMA add  | ress error soft | trap has not o   | ccurred          |                  |                    |       |  |

| bit 4        | DOOVR: DO    | Stack Overflov  | v Soft Trap Sta  | tus bit          |                  |                    |       |  |

|              | 1 = DO stack | overflow soft t | rap has occurre  | ed               |                  |                    |       |  |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

# REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | _   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |  |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |  |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |  |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |  |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |  |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |  |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |  |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |  |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |  |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |  |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |  |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |  |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |  |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |  |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |  |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |  |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |  |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |  |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |  |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |  |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |  |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |  |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |  |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

# REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

# bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                                                                      |       |                  | STA   | <15:8>                                  |       |       |       |

| bit 15                                                               |       |                  |       |                                         |       |       | bit 8 |

|                                                                      |       |                  |       |                                         |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |                  | STA   | A<7:0>                                  |       |       |       |

| bit 7                                                                |       |                  |       |                                         |       |       | bit 0 |

|                                                                      |       |                  |       |                                         |       |       |       |

| Legend:                                                              |       |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       | ad as '0'                               |       |       |       |

| -n = Value at P                                                      | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

|        |     | PP20P<5:0> |       |       |         |       |       |

|--------|-----|------------|-------|-------|---------|-------|-------|

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| bit 15 |     |            |       |       |         |       | bit 8 |

|        |     |            |       | RP35  | iR<5:0> |       |       |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

# REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|

| —      | —   |       | RP37R<5:0> |       |       |       |       |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP36R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0            | R/W-0                | R/W-0    | R/W-0  |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|----------------------|----------|--------|

|               | F15BP<3:0>                   |                                                                                                                            |                                                |                  | F14BI                | P<3:0>   |        |

| bit 15        |                              |                                                                                                                            |                                                |                  |                      |          | bit 8  |

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0            | R/W-0                | R/W-0    | R/W-0  |

| F13BP<3:0>    |                              |                                                                                                                            |                                                |                  |                      | P<3:0>   | 1010 0 |

| bit 7         |                              |                                                                                                                            |                                                |                  |                      |          | bit 0  |

| Legend:       |                              |                                                                                                                            |                                                |                  |                      |          |        |

| R = Readabl   | e bit                        | W = Writable                                                                                                               | bit                                            | U = Unimplen     | nented bit, read     | d as '0' |        |

| -n = Value at | t POR                        | '1' = Bit is set                                                                                                           | '1' = Bit is set                               |                  | '0' = Bit is cleared |          | nown   |

| bit 15-12     | 1111 = Filte<br>1110 = Filte | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | differ<br>4      |                      |          |        |

| bit 11-8      | F14BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val | ues as bits<15       | :12>)    |        |

| bit 7-4       | F13BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val | ues as bits<15       | :12>)    |        |

| bit 3-0       | F12BP<3:0:                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 2 bits (same val | ues as bits<15       | :12>)    |        |

# REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

# REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

| R/W-0      | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |

|------------|---------------------------------------|------------------------------------|----------------|------------------|------------------------------|-----------------|--------|

| ADCTS4     | ADCTS3                                | ADCTS2                             | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |

| bit 15     |                                       |                                    |                |                  |                              |                 | bit 8  |

| R/W-0      | R/W-0                                 | R/W-0                              | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |

| OC4CS      |                                       | OC2CS                              | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |

| bit 7      |                                       |                                    |                |                  |                              |                 | bit (  |

| Legend:    |                                       |                                    |                |                  |                              |                 |        |

| R = Reada  | ble bit                               | W = Writable                       | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |

| -n = Value | at POR                                | '1' = Bit is set                   |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |

|            |                                       |                                    |                |                  |                              |                 |        |

| bit 15     | ADCTS4: Sa                            | mple Trigger P                     | TGO15 for AE   | OC bit           |                              |                 |        |

|            | 1 = Generate                          | es Trigger wher                    | the broadcas   | t command is     | executed                     |                 |        |

|            | 0 = Does not                          | generate Trigg                     | er when the b  | roadcast com     | mand is execute              | ed              |        |

| bit 14     |                                       | mple Trigger P                     |                |                  |                              |                 |        |

|            |                                       | es Trigger wher                    |                |                  |                              | al              |        |

| bit 13     |                                       |                                    |                |                  | mand is execute              | a               |        |

| DIE 13     |                                       | mple Trigger P<br>es Trigger wher  |                |                  | evecuted                     |                 |        |

|            |                                       |                                    |                |                  | mand is execute              | ed              |        |

| bit 12     |                                       | mple Trigger P                     |                |                  |                              |                 |        |

|            | 1 = Generate                          | es Trigger wher                    | the broadcas   | t command is     | executed                     |                 |        |

|            |                                       |                                    |                |                  | mand is execute              | ed              |        |

| bit 11     | -                                     | ger/Synchroniz                     |                |                  |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 10     | IC3TSS: Trig                          | ger/Synchroniz                     | ation Source f | for IC3 bit      |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 9      | IC2TSS: Trig                          | ger/Synchroniz                     | ation Source f | for IC2 bit      |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 8      |                                       | ger/Synchroniz                     |                |                  |                              |                 |        |

|            |                                       |                                    |                |                  | ast command is broadcast con |                 | ited   |

| bit 7      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            |                                       | es clock pulse v<br>generate clock |                |                  | d is executed command is exe | cuted           |        |

| bit 6      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            |                                       | es clock pulse v<br>aenerate clock |                |                  | d is executed command is exe | cuted           |        |

| bit 5      |                                       | ck Source for C                    | -              |                  |                              |                 |        |

|            | 1 = Generate                          | es clock pulse v                   | when the broad |                  | d is executed command is exe | cuted           |        |

|            | This register is rea<br>PTGSTRT = 1). | -                                  |                |                  |                              |                 | and    |

|            | This register is on                   | lv used with the                   | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |

|            |                                       | .,                                 |                |                  | c.op commune                 | •               |        |

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

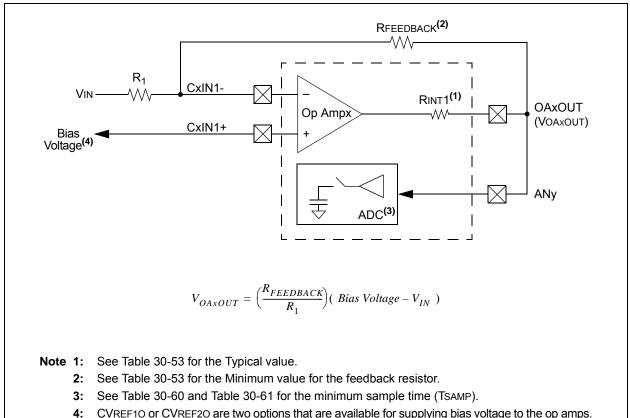

# 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

# 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

| REGISTER      | 25-3: CM40                                              | CON: COMPA                             | RATOR 4 CO        | ONTROL RE        | GISTER             |                                            |                     |

|---------------|---------------------------------------------------------|----------------------------------------|-------------------|------------------|--------------------|--------------------------------------------|---------------------|

| R/W-0         | R/W-0                                                   | R/W-0                                  | U-0               | U-0              | U-0                | R/W-0                                      | R/W-0               |

| CON           | COE                                                     | CPOL                                   | —                 | —                | _                  | CEVT                                       | COUT                |

| bit 15        |                                                         |                                        |                   |                  |                    |                                            | bit 8               |

| R/W-0         | DAM 0                                                   | U-0                                    |                   | U-0              | U-0                |                                            | R/W-0               |

|               | R/W-0                                                   | 0-0                                    | R/W-0             | 0-0              | 0-0                | R/W-0                                      |                     |

| EVPOL1        | EVPOL0                                                  | —                                      | CREF              | —                | _                  | CCH1 <sup>(1)</sup>                        | CCH0 <sup>(1)</sup> |

| bit 7         |                                                         |                                        |                   |                  |                    |                                            | bit (               |

| Legend:       |                                                         |                                        |                   |                  |                    |                                            |                     |

| R = Readable  | e bit                                                   | W = Writable                           | bit               | U = Unimple      | mented bit, rea    | d as '0'                                   |                     |

| -n = Value at |                                                         | '1' = Bit is se                        |                   | '0' = Bit is cle |                    | x = Bit is unkr                            | iown                |

|               |                                                         |                                        | •                 |                  |                    |                                            |                     |

| bit 15        | CON: Comp                                               | arator Enable b                        | bit               |                  |                    |                                            |                     |

|               |                                                         | ator is enabled                        |                   |                  |                    |                                            |                     |

|               |                                                         | ator is disabled                       |                   |                  |                    |                                            |                     |

| bit 14        | COE: Comp                                               | arator Output E                        | nable bit         |                  |                    |                                            |                     |

|               |                                                         | ator output is pr<br>ator output is in |                   | xOUT pin         |                    |                                            |                     |

| bit 13        | CPOL: Com                                               | parator Output                         | Polarity Select   | bit              |                    |                                            |                     |

|               |                                                         | ator output is in                      |                   |                  |                    |                                            |                     |

|               | 0 = Compara                                             | ator output is no                      | ot inverted       |                  |                    |                                            |                     |

| bit 12-10     | Unimpleme                                               | nted: Read as                          | '0'               |                  |                    |                                            |                     |

| bit 9         | CEVT: Com                                               | parator Event b                        | it                |                  |                    |                                            |                     |

|               | interrup                                                | ts until the bit is                    | cleared           | POL<1:0> set     | tings occurred;    | disables future                            | triggers and        |

|               | •                                                       | ator event did i                       |                   |                  |                    |                                            |                     |

| bit 8         |                                                         | parator Output                         |                   |                  |                    |                                            |                     |

|               | $\frac{\text{VVnen CPOL}}{1 = \text{VIN} + > \text{V}}$ | <u>. = 0 (non-inver</u><br>/N-         | ted polarity):    |                  |                    |                                            |                     |

|               | 0 = VIN + < V                                           |                                        |                   |                  |                    |                                            |                     |

|               | When CPOL                                               | = 1 (inverted p                        | olarity):         |                  |                    |                                            |                     |

|               | 1 = VIN+ < V                                            |                                        |                   |                  |                    |                                            |                     |

|               | 0 = VIN + > V                                           | 'IN-                                   |                   |                  |                    |                                            |                     |

| bit 7-6       |                                                         | >: Trigger/Ever                        |                   | -                |                    |                                            |                     |

|               | 10 = Trigger                                            |                                        | generated only    |                  |                    | or output (while (<br>ne polarity selected |                     |

|               |                                                         | L = 1 (inverted)<br>-high transition   |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-low transition     |                   | ator output.     |                    |                                            |                     |

|               |                                                         | /event/interrupt<br>(while CEVT =      |                   | v on low-to-higl | n transition of th | e polarity selecte                         | ed comparato        |

|               |                                                         | L = 1 (inverted                        |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-high transition    |                   | ator output.     |                    |                                            |                     |

|               | 00 = Trigger                                            | /event/interrupt                       | generation is     | disabled         |                    |                                            |                     |

| Note 1: In    | puts that are se                                        | lected and not a                       | available will be | e tied to Vss. S | See the "Pin Dia   | agrams" sectior                            | n for available     |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        |                                            | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|

| 25                 | DAW                  |        |                                            | Wn = decimal adjust Wn                      | 1             | 1                             | С                        |

| 26                 | DEC                  | DEC    | f                                          | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | f,WREG                                     | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC    | Ws,Wd                                      | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |