Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp204t-e-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1 (General Purpose Families) and Table 2 (Motor Control Families). Their pinout diagrams appear on the following pages.

|                   | â                              | (se                           |             |                      | Rei           | nappa          | ble Pe | eriphe             | rals                          |                                    |      |               |                              |                     |      |     |          |           |                                |

|-------------------|--------------------------------|-------------------------------|-------------|----------------------|---------------|----------------|--------|--------------------|-------------------------------|------------------------------------|------|---------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbyte) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | UART   | SPI <sup>(2)</sup> | ECAN <sup>TM</sup> Technology | External Interrupts <sup>(3)</sup> | I²C™ | CRC Generator | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | РТС | I/O Pins | Pins      | Packages                       |

| PIC24EP32GP202    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP64GP202    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128GP202   | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | —                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(4)</sup> , |

| PIC24EP256GP202   | 1024                           | 256                           | 32          | 2                    |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512GP202   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP32GP203    | 512                            | 32                            | 4           | 5                    | 4             | 4              | 2      | 2                  |                               | 3                                  | 2    | 1             | 8                            | 3/4                 | Vaa  | Vaa | 25       | 36        | VTLA                           |

| PIC24EP64GP203    | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    |               | 0                            | 3/4                 | Yes  | Yes | 25       | 30        | VILA                           |

| PIC24EP32GP204    | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP64GP204    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | VTLA <sup>(4)</sup> ,          |

| PIC24EP128GP204   | 1024                           | 128                           | 16          | 16 5<br>32           | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256GP204   | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | UQFN                           |

| PIC24EP512GP204   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP64GP206    | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| PIC24EP128GP206   | 1024                           | 128                           | 16          | _                    |               |                |        |                    |                               |                                    | -    |               |                              | ~ ~ ~               |      |     |          | ~ /       | TQFP.                          |

| PIC24EP256GP206   | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | _                             | 3                                  | 2    | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| PIC24EP512GP206   | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32GP502  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64GP502  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128GP502 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(4)</sup> . |

| dsPIC33EP256GP502 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512GP502 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32GP503  | 512                            | 32                            | 4           | _                    | _             | _              | _      | _                  |                               | _                                  | _    |               | _                            |                     |      |     |          |           |                                |

| dsPIC33EP64GP503  | 1024                           | 64                            | 8           | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP32GP504  | 512                            | 32                            | 4           |                      |               |                |        |                    |                               |                                    |      |               |                              | İ                   |      |     |          |           |                                |

| dsPIC33EP64GP504  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | VTLA <sup>(4)</sup> ,          |

| dsPIC33EP128GP504 | 1024                           | 128                           | 16          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256GP504 | 1024                           | 256                           | 32          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          | 40        | UQFN,<br>UQFN                  |

| dsPIC33EP512GP504 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64GP506  | 1024                           | 64                            | 8           |                      |               |                |        |                    |                               |                                    |      |               |                              | 1                   |      |     |          |           |                                |

| dsPIC33EP128GP506 | 1024                           | 128                           | 16          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           | TQFP,                          |

| dsPIC33EP256GP506 | 1024                           | 256                           | 32          | 5                    | 4             | 4              | 2      | 2                  | 1                             | 3                                  | 2    | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| dsPIC33EP512GP506 | 1024                           | 512                           | 48          |                      |               |                |        |                    |                               |                                    |      |               |                              |                     |      |     |          |           |                                |

|                   |                                | 1                             |             |                      |               | 1              | 1      | 1                  |                               |                                    | 1    | 1             | 1                            |                     |      |     |          |           |                                |

#### TABLE 1: dsPIC33EPXXXGP50X and PIC24EPXXXGP20X GENERAL PURPOSE FAMILIES

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

Only SPI2 is remappable.

INT0 is not remappable.

4: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

| IABLE 4-2  | 23: E | CAN1 I         | REGIST    | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0>                 | •) = 1 FC | OR dsPIC                      | 33EPX | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|----------------|-----------|--------|--------|--------|--------|-------------------------------|-----------|-------------------------------|-------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15         | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                         | Bit 8     | Bit 7                         | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  | 046E EID<15:8> |           |        |        |        |        |                               |           |                               |       | EID<   | 7:0>   |        |        |       | xxxx  |               |

| C1RXF12SID | 0470  | SID<10:3>      |           |        |        |        |        | SID<2:0> — EXIDE — EID<17:16> |           |                               |       |        | 7:16>  | xxxx   |        |       |       |               |

| C1RXF12EID | 0472  | EID<15:8>      |           |        |        |        |        | EID<7:0>                      |           |                               |       |        |        |        | xxxx   |       |       |               |

| C1RXF13SID | 0474  |                | SID<10:3> |        |        |        |        |                               |           | SID<2:0>                      |       | _      | EXIDE  | —      | EID<1  | 7:16> | xxxx  |               |

| C1RXF13EID | 0476  |                |           |        | EID<   | :15:8> |        |                               |           | EID<7:0>                      |       |        |        |        |        | xxxx  |       |               |

| C1RXF14SID | 0478  |                |           |        | SID<   | :10:3> |        |                               |           | SID<2:0> — EXIDE — EID<17:16> |       |        |        |        | 7:16>  | xxxx  |       |               |

| C1RXF14EID | 047A  | EID<15:8>      |           |        |        |        |        | EID<7:0>                      |           |                               |       |        |        | xxxx   |        |       |       |               |

| C1RXF15SID | 047C  | SID<10:3>      |           |        |        |        |        |                               | SID<2:0>  |                               | _     | EXIDE  | _      | EID<1  | 7:16>  | xxxx  |       |               |

| C1RXF15EID | 047E  |                |           |        | EID<   | :15:8> |        |                               |           |                               |       |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|--|

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| bit 7                              |       |       |       |                                         |       |       | bit C |  |  |

|                                    |       |       | NVMAD | )R<23:16>                               |       |       |       |  |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |  |

| _                                  | —     | —     | —     | —                                       | _     | —     | —     |  |  |

| U-0                                | U-0   | U-0   | U-0   | U-0                                     | U-0   | U-0   | U-0   |  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADR<23:16>:** Nonvolatile Memory Write Address High bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x           | R/W-x    | R/W-x |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-----------------|----------|-------|--|

|                                    |       |       | NVMA  | DR<15:8>                                |                 |          |       |  |

| bit 15                             |       |       |       |                                         |                 |          | bit 8 |  |

| R/W-x                              | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x           | R/W-x    | R/W-x |  |

|                                    |       |       | NVMA  | DR<7:0>                                 |                 |          |       |  |

| bit 7                              |       |       |       |                                         |                 |          | bit 0 |  |

| Legend:                            |       |       |       |                                         |                 |          |       |  |

| R = Readable bit W = Writable bit  |       |       | it    | U = Unimpler                            | nented bit, rea | d as '0' |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0             | U-0 | U-0              | U-0  | U-0                                | U-0                                                                    | U-0 | U-0   |  |  |  |

|-----------------|-----|------------------|------|------------------------------------|------------------------------------------------------------------------|-----|-------|--|--|--|

| —               | —   | —                | —    | —                                  | —                                                                      | —   | —     |  |  |  |

| bit 15          |     |                  |      |                                    |                                                                        |     | bit 8 |  |  |  |

|                 |     |                  |      |                                    |                                                                        |     |       |  |  |  |

| W-0             | W-0 | W-0              | W-0  | W-0                                | W-0                                                                    | W-0 | W-0   |  |  |  |

|                 |     |                  | NVMK | EY<7:0>                            |                                                                        |     |       |  |  |  |

| bit 7           |     |                  |      |                                    |                                                                        |     | bit 0 |  |  |  |

|                 |     |                  |      |                                    |                                                                        |     |       |  |  |  |

| Legend:         |     |                  |      |                                    |                                                                        |     |       |  |  |  |

| R = Readable I  | bit | W = Writable     | bit  | U = Unimplemented bit, read as '0' |                                                                        |     |       |  |  |  |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cle                   | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |     |       |  |  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

| U-0                                | U-0                                                | U-0                                          | U-0            | U-0              | U-0              | U-0             | U-0   |  |  |

|------------------------------------|----------------------------------------------------|----------------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|

| -                                  | —                                                  | —                                            | —              | —                | —                | —               | —     |  |  |

| bit 15                             |                                                    |                                              |                |                  |                  |                 | bit 8 |  |  |

| U-0                                | U-0                                                | U-0                                          | U-0            | R-1              | R-1              | R-1             | R-1   |  |  |

| _                                  | _                                                  | LSTCH<3:0>                                   |                |                  |                  |                 |       |  |  |

| bit 7                              |                                                    |                                              |                |                  |                  |                 |       |  |  |

| Legend:                            |                                                    |                                              |                |                  |                  |                 |       |  |  |

| R = Readat                         | ole bit                                            | W = Writable                                 | bit            | U = Unimpler     | mented bit, read | 1 as '0'        |       |  |  |

| -n = Value at POR '1' = Bit is set |                                                    |                                              |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

|                                    |                                                    |                                              |                |                  |                  |                 |       |  |  |

| bit 15-4                           | Unimplemen                                         | ted: Read as '                               | 0'             |                  |                  |                 |       |  |  |

| bit 3-0                            | LSTCH<3:0>                                         | : Last DMAC C                                | hannel Active  | e Status bits    |                  |                 |       |  |  |

|                                    | 1111 = No DI<br>1110 = Rese                        | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set              |                 |       |  |  |

|                                    | •                                                  |                                              |                |                  |                  |                 |       |  |  |

|                                    | •                                                  |                                              |                |                  |                  |                 |       |  |  |

|                                    | •                                                  |                                              |                |                  |                  |                 |       |  |  |

|                                    |                                                    | rved<br>data transfer wa<br>data transfer wa |                |                  |                  |                 |       |  |  |

|                                    | 0001 = Last data transfer was handled by Channel 1 |                                              |                |                  |                  |                 |       |  |  |

# REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0001 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0               | U-0   | U-0              | U-0   | R/W-0             | R/W-0           | R/W-0           | R/W-0            |  |

|-------------------|-------|------------------|-------|-------------------|-----------------|-----------------|------------------|--|

| —                 | -     | —                | —     |                   | LEB             | <11:8>          |                  |  |

| bit 15            |       |                  |       |                   |                 |                 | bit 8            |  |

|                   |       |                  |       |                   |                 |                 |                  |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0            |  |

|                   |       |                  | LEE   | 3<7:0>            |                 |                 |                  |  |

| bit 7             |       |                  |       |                   |                 |                 | bit 0            |  |

|                   |       |                  |       |                   |                 |                 |                  |  |

| Legend:           |       |                  |       |                   |                 |                 |                  |  |

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | id as '0'       |                  |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | = Bit is unknown |  |

# REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

| R/W-0         | R/W-0                          | R/W-0                                      | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|--------------------------------|--------------------------------------------|-------------------|-------------------|------------------|-----------------|-------|

| QCAPEN        | FLTREN                         | QFDIV2                                     | QFDIV1            | QFDIV0            | OUTFNC1          | OUTFNC0         | SWPAB |

| bit 15        | ·                              | ·                                          |                   |                   |                  |                 | bit 8 |

| R/W-0         | R/W-0                          | R/W-0                                      | R/W-0             | R-x               | R-x              | R-x             | R-x   |

| HOMPOL        | IDXPOL                         | QEBPOL                                     | QEAPOL            | HOME              | INDEX            | QEB             | QEA   |

| bit 7         |                                |                                            |                   | TIOME             | INDEX            | QLD             | bit ( |

| Legend:       |                                |                                            |                   |                   |                  |                 |       |

| R = Readable  | e bit                          | W = Writable                               | bit               | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at |                                | '1' = Bit is set                           |                   | '0' = Bit is cle  |                  | x = Bit is unkn | own   |

|               |                                |                                            |                   |                   |                  |                 |       |

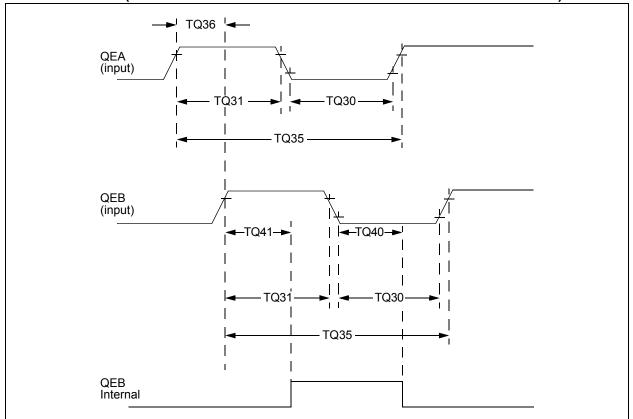

| bit 15        | QCAPEN: Q                      | EI Position Cou                            | nter Input Cap    | ture Enable bit   |                  |                 |       |

|               |                                | tch event trigge                           |                   |                   |                  |                 |       |

|               |                                | tch event does                             |                   | -                 |                  |                 |       |

| bit 14        |                                | Ax/QEBx/INDX                               | •                 | tal Filter Enable | e dit            |                 |       |

|               |                                | digital filter is e<br>digital filter is d |                   | sed)              |                  |                 |       |

| bit 13-11     |                                | : QEAx/QEBx/II                             |                   |                   | Iter Clock Divid | le Select bits  |       |

|               | 111 = 1:128                    |                                            |                   | g                 |                  |                 |       |

|               | 110 = 1:64 cl                  | lock divide                                |                   |                   |                  |                 |       |

|               | 101 = 1:32 cl                  |                                            |                   |                   |                  |                 |       |

|               | 100 = 1:16 cl                  |                                            |                   |                   |                  |                 |       |

|               | 011 = 1:8 clo<br>010 = 1:4 clo |                                            |                   |                   |                  |                 |       |

|               | 001 = 1:4 Clo                  |                                            |                   |                   |                  |                 |       |

|               | 000 = 1:1 clo                  |                                            |                   |                   |                  |                 |       |

| bit 10-9      | OUTFNC<1:                      | 0>: QEI Module                             | Output Functi     | on Mode Selec     | ct bits          |                 |       |

|               |                                | NCMPx pin goe                              | -                 |                   |                  | GEC             |       |

|               |                                | NCMPx pin goe                              |                   |                   |                  |                 |       |

|               |                                | NCMPx pin goe                              | s high when P     | $OS1CNT \ge QE$   | IIGEC            |                 |       |

| L:1 0         | 00 = Output i                  |                                            |                   |                   |                  |                 |       |

| bit 8         |                                | ap QEA and QE                              | •                 |                   |                  |                 |       |

|               |                                | d QEBx are sw<br>d QEBx are not            |                   | quadrature dec    | coder logic      |                 |       |

| bit 7         | HOMPOL: H                      | OMEx Input Po                              | larity Select bit |                   |                  |                 |       |

|               | 1 = Input is in                |                                            |                   |                   |                  |                 |       |

| bit 6         | 0 = Input is n                 |                                            | ty Soloot bit     |                   |                  |                 |       |

|               | 1 = Input is in                | OXx Input Polari                           | ly Select bit     |                   |                  |                 |       |

|               | 0 = Input is n                 |                                            |                   |                   |                  |                 |       |

| bit 5         | -                              | EBx Input Polar                            | itv Select bit    |                   |                  |                 |       |

|               | 1 = Input is i                 | •                                          | .,                |                   |                  |                 |       |

|               | 0 = Input is r                 |                                            |                   |                   |                  |                 |       |

| bit 4         | QEAPOL: Q                      | EAx Input Polar                            | ity Select bit    |                   |                  |                 |       |

|               | 1 = Input is i                 |                                            |                   |                   |                  |                 |       |

|               | 0 = Input is r                 | not inverted                               |                   |                   |                  |                 |       |

| bit 3         | HOME: Statu                    |                                            |                   |                   |                  |                 |       |

| DIL 3         | <b>HOME</b> . Statu            |                                            | out Pin Alter Po  | olarity Control   |                  |                 |       |

| DIL 3         | 1 = Pin is at<br>0 = Pin is at | logic '1'                                  | out Pin Aiter Po  | bianty Control    |                  |                 |       |

# REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER

# REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

# 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0                | U-0                                           | R/W-0                                                                                                           | R/W-0               | R/W-0             | U-0             | R/W-0                   | R/W-0                     |  |  |  |  |

|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-----------------|-------------------------|---------------------------|--|--|--|--|

| UARTEN <sup>(1</sup> | ) _                                           | USIDL                                                                                                           | IREN <sup>(2)</sup> | RTSMD             | _               | UEN1                    | UEN0                      |  |  |  |  |

| bit 15               |                                               |                                                                                                                 |                     |                   |                 |                         | bit 8                     |  |  |  |  |

|                      |                                               |                                                                                                                 |                     |                   | 5444.0          |                         |                           |  |  |  |  |

| R/W-0, HC            |                                               | R/W-0, HC                                                                                                       | R/W-0               | R/W-0             | R/W-0           | R/W-0                   | R/W-0                     |  |  |  |  |

| WAKE                 | LPBACK                                        | ABAUD                                                                                                           | URXINV              | BRGH              | PDSEL1          | PDSEL0                  | STSEL                     |  |  |  |  |

| bit 7                |                                               |                                                                                                                 |                     |                   |                 |                         | bit                       |  |  |  |  |

| Legend:              |                                               | HC = Hardwar                                                                                                    | e Clearable b       | it                |                 |                         |                           |  |  |  |  |

| R = Readal           | ole bit                                       | W = Writable b                                                                                                  | it                  | U = Unimplem      | ented bit, read | as '0'                  |                           |  |  |  |  |

| -n = Value a         | at POR                                        | '1' = Bit is set                                                                                                |                     | '0' = Bit is clea | ared            | x = Bit is unkn         | iown                      |  |  |  |  |

| bit 15               | 1 = UARTx is                                  | ARTx Enable bit<br>s enabled; all UA<br>s disabled; all UA                                                      | ARTx pins are       |                   |                 |                         |                           |  |  |  |  |

| bit 14               | Unimplemen                                    | ted: Read as '0                                                                                                 | ,                   |                   |                 |                         |                           |  |  |  |  |

| bit 13               | USIDL: UAR                                    | Tx Stop in Idle M                                                                                               | lode bit            |                   |                 |                         |                           |  |  |  |  |

|                      |                                               | nues module ope<br>es module opera                                                                              |                     |                   | le mode         |                         |                           |  |  |  |  |

| bit 12               |                                               | Encoder and De                                                                                                  |                     |                   |                 |                         |                           |  |  |  |  |

|                      |                                               | <ul> <li>1 = IrDA encoder and decoder are enabled</li> <li>0 = IrDA encoder and decoder are disabled</li> </ul> |                     |                   |                 |                         |                           |  |  |  |  |

| bit 11               | RTSMD: Mod                                    | le Selection for                                                                                                | UxRTS Pin bi        | t                 |                 |                         |                           |  |  |  |  |

|                      |                                               | oin is in Simplex<br>oin is in Flow Co                                                                          |                     |                   |                 |                         |                           |  |  |  |  |

| bit 10               | Unimplemen                                    | ted: Read as '0                                                                                                 | ,                   |                   |                 |                         |                           |  |  |  |  |

| bit 9-8              | UEN<1:0>: U                                   | JARTx Pin Enab                                                                                                  | le bits             |                   |                 |                         |                           |  |  |  |  |

|                      |                                               | JxRX and BCLK                                                                                                   |                     |                   |                 | controlled by PC        | ORT latches <sup>(3</sup> |  |  |  |  |

|                      |                                               | JxRX, UxCTS ar<br>JxRX and UxRT                                                                                 |                     |                   |                 | ontrolled by DC         | DT latabaa(4              |  |  |  |  |

|                      |                                               | nd UxRX pins a                                                                                                  |                     |                   |                 |                         |                           |  |  |  |  |

| bit 7                |                                               | e-up on Start bit                                                                                               | Detect During       | Sleep Mode Er     | nable bit       |                         |                           |  |  |  |  |

|                      | 1 = UARTx o<br>in hardwa                      | continues to sam<br>are on the follow<br>-up is enabled                                                         | ple the UxRX        | pin; interrupt is |                 | he falling edge         | ; bit is cleare           |  |  |  |  |

| bit 6                | LPBACK: UA                                    | ARTx Loopback                                                                                                   | Mode Select I       | oit               |                 |                         |                           |  |  |  |  |

|                      |                                               | Loopback mode<br>k mode is disabl                                                                               |                     |                   |                 |                         |                           |  |  |  |  |

|                      | Refer to the " <b>UAI</b><br>enabling the UAR |                                                                                                                 |                     |                   | Family Referen  | <i>ce Manual"</i> for i | nformation or             |  |  |  |  |

|                      | This feature is or                            |                                                                                                                 |                     | -                 | 0)              |                         |                           |  |  |  |  |

|                      |                                               | •                                                                                                               |                     |                   | · .             |                         |                           |  |  |  |  |

|                      |                                               | nis feature is only available on 44-pin and 64-pin devices.                                                     |                     |                   |                 |                         |                           |  |  |  |  |

4: This feature is only available on 64-pin devices.

| U-0                     | U-0                                                                | U-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |  |

|-------------------------|--------------------------------------------------------------------|------------------------------------|---------|------------------|-----------------|------------------|---------|--|--|--|

| _                       | _                                                                  |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1          | FILHIT0 |  |  |  |

| bit 15                  | <b>I</b>                                                           |                                    |         |                  |                 |                  | bit 8   |  |  |  |

|                         |                                                                    |                                    |         |                  |                 |                  |         |  |  |  |

| U-0                     | R-1                                                                | R-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |  |

| _                       | ICODE6                                                             | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1           | ICODE0  |  |  |  |

| bit 7                   |                                                                    |                                    |         |                  |                 |                  | bit     |  |  |  |

| Logondi                 |                                                                    |                                    |         |                  |                 |                  |         |  |  |  |

| Legend:<br>R = Readable | - hit                                                              | W = Writable                       | hit     | LI – Unimplor    | mented bit, rea | d as '0'         |         |  |  |  |

| -n = Value at           |                                                                    | '1' = Bit is set                   |         | '0' = Bit is cle |                 | x = Bit is unkr  |         |  |  |  |

|                         | FUR                                                                |                                    |         |                  | aleu            | x – Dit is uliki |         |  |  |  |

| bit 15-13               | Unimplemen                                                         | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |  |

| bit 12-8                | =                                                                  | Filter Hit Num                     |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | 1 = Reserved                       |         |                  |                 |                  |         |  |  |  |

|                         | 01111 <b>= Filte</b>                                               | er 15                              |         |                  |                 |                  |         |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         | •<br>00001 = Filter 1                                              |                                    |         |                  |                 |                  |         |  |  |  |

|                         | 00001 = Filte                                                      |                                    |         |                  |                 |                  |         |  |  |  |

| bit 7                   |                                                                    | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |  |

| bit 6-0                 | -                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         | ICODE<6:0>: Interrupt Flag Code bits<br>1000101-1111111 = Reserved |                                    |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | IFO almost full                    |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | leceiver overflo                   |         |                  |                 |                  |         |  |  |  |

|                         | 1000010 = K<br>1000001 = E                                         | Vake-up interru<br>rror interrupt  | μ       |                  |                 |                  |         |  |  |  |

|                         | 1000000 = N                                                        |                                    |         |                  |                 |                  |         |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | 11111 = Rese                       |         |                  |                 |                  |         |  |  |  |

|                         | •                                                                  | B15 buffer inte                    | inupt   |                  |                 |                  |         |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |  |

|                         | 0001001 <b>= R</b>                                                 | B9 buffer inter                    | rupt    |                  |                 |                  |         |  |  |  |

|                         |                                                                    | B8 buffer inter                    |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | RB5 buffer inte                    |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | RB4 buffer inte                    |         |                  |                 |                  |         |  |  |  |

|                         | 0000011 <b>= T</b>                                                 | RB3 buffer inte                    | errupt  |                  |                 |                  |         |  |  |  |

|                         |                                                                    |                                    |         |                  |                 |                  |         |  |  |  |

|                         |                                                                    | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                  |         |  |  |  |

# REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

NOTES:

# 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the AD1CON2 register:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the AD1CON2 registers is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (AD1CON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (AD1CON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "Analog-to-Digital Converter (ADC)" (DS70621) section in the "dsPIC33/ PIC24 Family Reference Manual".

# 23.3 ADC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser:<br>http://www.microchip.com/wwwproducts/ |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Devices.aspx?dDocName=en555464                                                                                                                          |

# 23.3.1 KEY RESOURCES

- "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

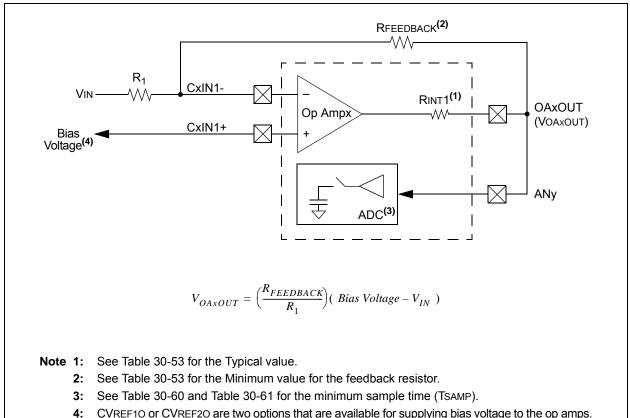

#### 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

# 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax    | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------|------------------------------------|---------------|-------------------------------|--------------------------|

| 72                 | SL                   | SL     | f                  | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG             | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd              | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd         | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd       | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |