Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp204t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

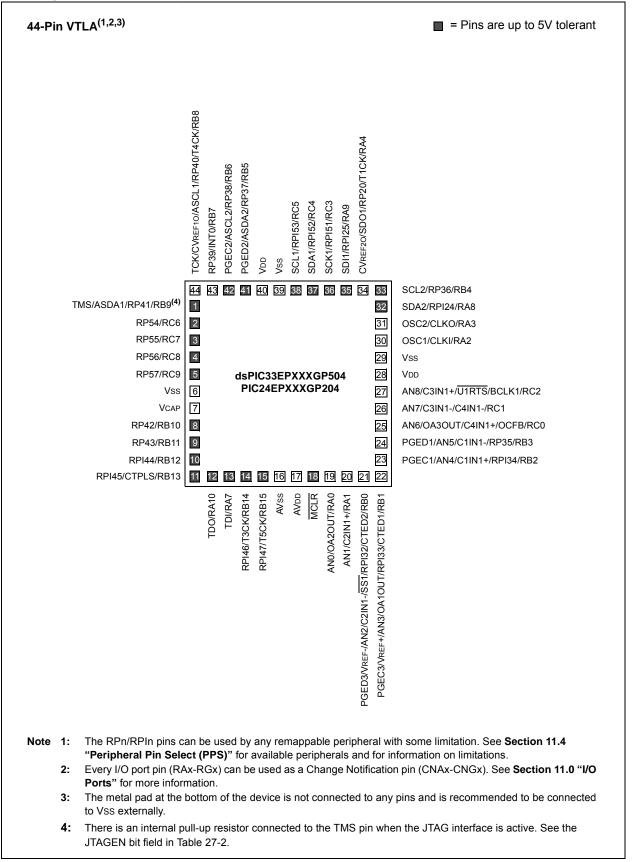

#### **Pin Diagrams (Continued)**

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

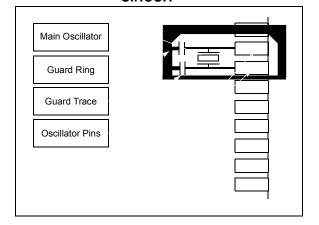

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

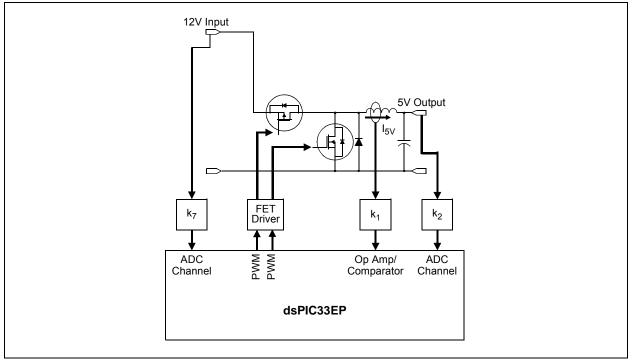

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

# TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                                        | Bit 8                                                | Bit 7 | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|----------------------------------------------|------------------------------------------------------|-------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —                                            | _                                                    |       |       |           | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —                                            | _                                                    |       |       |           | I2C1 Transi  | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | Baud Rate Generator                          |                                                      |       |       |           |              |              |       | 0000  |       |               |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                                       | DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN |       |       |           |              |              |       | 1000  |       |               |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT ADD10 IWCOL I2COV D_A P S R_W RBF TBF |                                                      |       |       |           |              | TBF          | 0000  |       |       |               |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |                                              |                                                      |       |       | I2C1 Addr | ess Register | r            |       |       |       | 0000          |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |                                              |                                                      |       |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _                                            | _                                                    |       |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _                                            | _                                                    |       |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _                                            |                                                      |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                                       | SMEN                                                 | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                                       | ADD10                                                | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      |                                              |                                                      |       |       | I2C2 Addr | ess Register | r            |       |       |       | 0000          |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | _      |                                              |                                                      |       |       | I2C2 Add  | dress Mask   |              |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                            | Bit 14                    | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8                                                | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|-----------------------------------|---------------------------|----------|--------|--------|--------|--------------------------|------------------------------------------------------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN                            | —                         | USIDL    | IREN   | RTSMD  | _      | UEN<                     | UEN<1:0> WAKE LPBACK ABAUD URXINV BRGH PDSEL<1:0> ST |            |          |       |            | STSEL    | 0000  |        |       |               |

| U1STA       | 0222  | UTXISEL1                          | UTXINV                    | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                    | TRMT                                                 | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _                                 | _                         | _        | _      | _      | _      | UART1 Transmit Register  |                                                      |            |          |       |            |          |       | xxxx   |       |               |

| U1RXREG     | 0226  | _                                 | _                         | _        | _      | _      | _      | – UART1 Receive Register |                                                      |            |          |       |            |          |       | 0000   |       |               |

| U1BRG       | 0228  |                                   |                           |          |        |        |        | Baud                     | Rate Gen                                             | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

| U2MODE      | 0230  | UARTEN                            | _                         | USIDL    | IREN   | RTSMD  | _      | UEN<                     | :1:0>                                                | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1                          | UTXINV                    | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                    | TRMT                                                 | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _                                 | _                         | _        | _      | _      | _      | _                        |                                                      |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | _                                 | UART2 Receive Register 00 |          |        |        |        |                          |                                                      |            |          | 0000  |            |          |       |        |       |               |

| U2BRG       | 0238  | Baud Rate Generator Prescaler 000 |                           |          |        |        |        |                          |                                                      |            |          |       | 0000       |          |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nown                                                                                                                                                                                                                                                                                                                                                                                                |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Unimplemer                   | nted: Read as '0                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| (see Table 11<br>1111001 = I | I-2 for input pin's nput tied to RPI1                                                                                                                                  | election num<br>21                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          | onding RPn Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | e bit<br>POR<br>Unimplemen<br>IC2R<6:0>: /<br>(see Table 11<br>1111001 = I<br>0000001 = I<br>0000000 = I<br>Unimplemen<br>IC1R<6:0>: /<br>(see Table 11<br>1111001 = I | e bit W = Writable b<br>POR '1' = Bit is set<br>Unimplemented: Read as '0<br>IC2R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s<br>1111001 = Input tied to RPI1<br>0000001 = Input tied to CMP<br>0000000 = Input tied to Vss<br>Unimplemented: Read as '0<br>IC1R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s | e bit W = Writable bit<br>POR '1' = Bit is set<br>Unimplemented: Read as '0'<br>IC2R<6:0>: Assign Input Capture 2 (IC2)<br>(see Table 11-2 for input pin selection num<br>1111001 = Input tied to RPI121 | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>       IC1R<6:0>         e bit       W = Writable bit       U = Unimplem         POR       '1' = Bit is set       '0' = Bit is clear         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>         e bit       W = Writable bit       U = Unimplemented bit, real         POR       '1' = Bit is set       '0' = Bit is cleared         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>    e bit W = Writable bit U = Unimplemented bit, read as '0' POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkr Unimplemented: Read as '0' IC2R<6:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 <p< td=""></p<> |

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

# REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

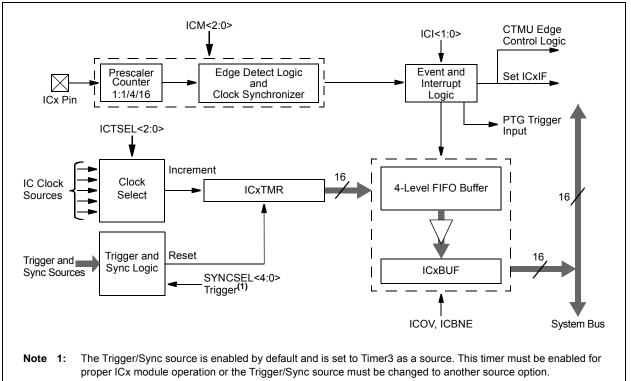

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

| PTG Output<br>Number | PTG Output Description                                  |

|----------------------|---------------------------------------------------------|

| PTGO0                | Trigger/Synchronization Source for OC1                  |

| PTGO1                | Trigger/Synchronization Source for OC2                  |

| PTGO2                | Trigger/Synchronization Source for OC3                  |

| PTGO3                | Trigger/Synchronization Source for OC4                  |

| PTGO4                | Clock Source for OC1                                    |

| PTGO5                | Clock Source for OC2                                    |

| PTGO6                | Clock Source for OC3                                    |

| PTGO7                | Clock Source for OC4                                    |

| PTGO8                | Trigger/Synchronization Source for IC1                  |

| PTGO9                | Trigger/Synchronization Source for IC2                  |

| PTGO10               | Trigger/Synchronization Source for IC3                  |

| PTGO11               | Trigger/Synchronization Source for IC4                  |

| PTGO12               | Sample Trigger for ADC                                  |

| PTGO13               | Sample Trigger for ADC                                  |

| PTGO14               | Sample Trigger for ADC                                  |

| PTGO15               | Sample Trigger for ADC                                  |

| PTGO16               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO17               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO18               | Mask Input Select for Op Amp/Comparator                 |

| PTGO19               | Mask Input Select for Op Amp/Comparator                 |

| PTGO20               | Reserved                                                |

| PTGO21               | Reserved                                                |

| PTGO22               | Reserved                                                |

| PTGO23               | Reserved                                                |

| PTGO24               | Reserved                                                |

| PTGO25               | Reserved                                                |

| PTGO26               | Reserved                                                |

| PTGO27               | Reserved                                                |

| PTGO28               | Reserved                                                |

| PTGO29               | Reserved                                                |

| PTGO30               | PTG Output to PPS Input Selection                       |

| PTGO31               | PTG Output to PPS Input Selection                       |

# TABLE 24-2: PTG OUTPUT DESCRIPTIONS

Note 1: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

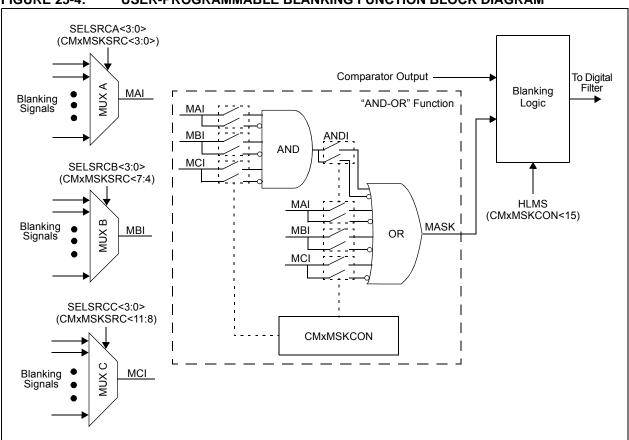

## DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN-0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

| U-0          | U-0                      | U-0                | U-0              | U-0              | U-0              | U-0            | U-0    |

|--------------|--------------------------|--------------------|------------------|------------------|------------------|----------------|--------|

|              | —                        | —                  | _                | —                |                  | —              | _      |

| bit 15       |                          |                    |                  |                  |                  |                | bit    |

|              |                          |                    |                  |                  |                  |                |        |

| U-0          | R/W-0                    | R/W-0              | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |

|              | CFSEL2                   | CFSEL1             | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |

| bit 7        |                          |                    |                  |                  |                  |                | bit    |

| Legend:      |                          |                    |                  |                  |                  |                |        |

| R = Readab   | le bit                   | W = Writable       | bit              | U = Unimpler     | mented bit, read | as '0'         |        |

| -n = Value a |                          | '1' = Bit is set   |                  | '0' = Bit is cle |                  | x = Bit is unk | nown   |

|              |                          |                    |                  |                  |                  |                | -      |

| bit 15-7     | Unimplemen               | ted: Read as       | ʻ0'              |                  |                  |                |        |

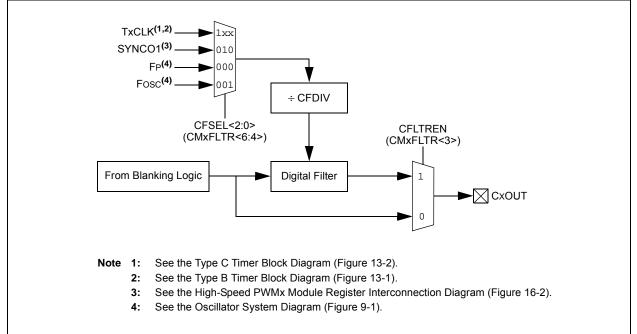

| oit 6-4      | CFSEL<2:0>               | : Comparator       | Filter Input Clo | ock Select bits  |                  |                |        |

|              | 111 = T5CLK              |                    | ·                |                  |                  |                |        |

|              | 110 = T4CLK              |                    |                  |                  |                  |                |        |

|              | 101 = T3CLK              | ( <sup>(1)</sup>   |                  |                  |                  |                |        |

|              | 100 = T2CLK              | <mark>(</mark> (2) |                  |                  |                  |                |        |

|              | 011 = Reserv             |                    |                  |                  |                  |                |        |

|              | 010 = SYNC               | 01 <sup>(3)</sup>  |                  |                  |                  |                |        |

|              | 001 = Fosc <sup>(4</sup> | 1)                 |                  |                  |                  |                |        |

|              | 000 = FP <sup>(4)</sup>  |                    |                  |                  |                  |                |        |

| bit 3        |                          | comparator Filt    | er Enable bit    |                  |                  |                |        |

|              | 1 = Digital filt         |                    |                  |                  |                  |                |        |

|              | •                        | er is disabled     |                  |                  |                  |                |        |

| bit 2-0      | CFDIV<2:0>:              | : Comparator F     | ilter Clock Div  | vide Select bits |                  |                |        |

|              | 111 = Clock              | Divide 1:128       |                  |                  |                  |                |        |

|              | 110 = Clock              | Divide 1:64        |                  |                  |                  |                |        |

|              | 101 = Clock              | Divide 1:32        |                  |                  |                  |                |        |

|              | 100 = Clock              | Divide 1:16        |                  |                  |                  |                |        |

|              | 011 = Clock              |                    |                  |                  |                  |                |        |

|              | 010 = Clock              |                    |                  |                  |                  |                |        |

|              | 001 = Clock              |                    |                  |                  |                  |                |        |

|              | 000 = Clock              | Divide 1:1         |                  |                  |                  |                |        |

| Note 1: S    | See the Type C Ti        | mer Block Diag     | gram (Figure 1   | 3-2).            |                  |                |        |

|              | See the Type B Tir       |                    |                  |                  |                  |                |        |

| •            |                          |                    |                  |                  | D: (E)           |                |        |

# REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 16-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

#### 26.1 Overview

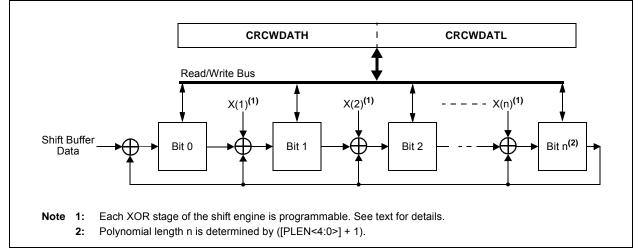

The CRC module can be programmed for CRC polynomials of up to the 32nd order, using up to 32 bits. Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation; functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit equation and the other a 32-bit equation:

$$\begin{array}{c} x16+x12+x5+1\\ \text{and}\\ x32+x26+x23+x22+x16+x12+x11+x10+x8+x7\\ +x5+x4+x2+x+1 \end{array}$$

To program these polynomials into the CRC generator, set the register bits as shown in Table 26-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The 0 bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length N, it is assumed that the *N*th bit will always be used, regardless of the bit setting. Therefore, for a polynomial length of 32, there is no 32nd bit in the CRCxOR register.

# TABLE 26-1:CRC SETUP EXAMPLES FOR16 AND 32-BIT POLYNOMIAL

| CRC Control | Bit V                  | alues                  |

|-------------|------------------------|------------------------|

| Bits        | 16-bit<br>Polynomial   | 32-bit<br>Polynomial   |

| PLEN<4:0>   | 01111                  | 11111                  |

| X<31:16>    | 0000 0000<br>0000 000x | 0000 0100<br>1100 0001 |

| X<15:0>     | 0001 0000<br>0010 000x | 0001 1101<br>1011 011x |

# 26.2 Programmable CRC Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|