Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-VFQFN Exposed Pad                                                          |

| Supplier Device Package    | 64-VQFN (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64gp206-e-mr |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                     |  |  |  |  |  |  |

|-------------------------------|-------------|----------------|---------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                                           |  |  |  |  |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                                  |  |  |  |  |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                                           |  |  |  |  |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                                |  |  |  |  |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                                            |  |  |  |  |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                                           |  |  |  |  |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                                  |  |  |  |  |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                                           |  |  |  |  |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                                |  |  |  |  |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                                            |  |  |  |  |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                                           |  |  |  |  |  |  |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                                  |  |  |  |  |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                                           |  |  |  |  |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                                |  |  |  |  |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                                            |  |  |  |  |  |  |

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                                  |  |  |  |  |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                                  |  |  |  |  |  |  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                                            |  |  |  |  |  |  |

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                                     |  |  |  |  |  |  |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                                        |  |  |  |  |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |  |  |  |  |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.                              |  |  |  |  |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |  |  |  |  |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.                              |  |  |  |  |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |  |  |  |  |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.                              |  |  |  |  |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |  |  |  |  |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.                    |  |  |  |  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.                   |  |  |  |  |  |  |

| Vdd                           | Р           |                | No      | Positive supply for peripheral logic and I/O pins.                                              |  |  |  |  |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                                          |  |  |  |  |  |  |

| Vss                           | Р           |                | No      | Ground reference for logic and I/O pins.                                                        |  |  |  |  |  |  |

| VREF+                         | 1           | Analog         | No      | Analog voltage reference (high) input.                                                          |  |  |  |  |  |  |

| VREF-                         | Ι           | Analog         | No      | Analog voltage reference (low) input.                                                           |  |  |  |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |  |  |  |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

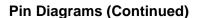

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

#### 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: Cl                                                              | PU STATUS I                                                                                                             | REGISTER                    |                          |                    |                   |               |  |  |  |  |

|------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|--|--|--|--|

| R/W-0                  | R/W-0                                                                    | R/W-0                                                                                                                   | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |  |  |  |  |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                                        | SA <sup>(1,4)</sup>                                                                                                     | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |  |  |  |  |

| bit 15                 |                                                                          |                                                                                                                         |                             |                          |                    |                   | bit 8         |  |  |  |  |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                                                   | R/W-0 <sup>(2,3)</sup>                                                                                                  | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |  |  |  |  |

| IPL2                   | IPL1                                                                     | IPL0                                                                                                                    | RA                          | N                        | OV                 | Z                 | С             |  |  |  |  |

| bit 7                  | ·                                                                        | •                                                                                                                       |                             | •                        |                    |                   | bit (         |  |  |  |  |

| Legend:                |                                                                          | C = Clearable                                                                                                           | e bit                       |                          |                    |                   |               |  |  |  |  |

| R = Readab             | le bit                                                                   | W = Writable                                                                                                            | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |  |  |  |  |

| -n = Value a           | t POR                                                                    | '1'= Bit is set                                                                                                         |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |  |  |  |  |

|                        |                                                                          |                                                                                                                         |                             |                          |                    |                   |               |  |  |  |  |

| bit 15                 | OA: Accumul                                                              | ator A Overflov                                                                                                         | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                                             | ator A has over                                                                                                         | flowed                      |                          |                    |                   |               |  |  |  |  |

|                        | 0 = Accumula                                                             | ator A has not o                                                                                                        | verflowed                   |                          |                    |                   |               |  |  |  |  |

| bit 14                 | OB: Accumul                                                              | ator B Overflov                                                                                                         | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                                             | ator B has over                                                                                                         | flowed                      |                          |                    |                   |               |  |  |  |  |

|                        |                                                                          | ator B has not c                                                                                                        |                             |                          |                    |                   |               |  |  |  |  |

| bit 13                 | bit 13 SA: Accumulator A Saturation 'Sticky' Status bit <sup>(1,4)</sup> |                                                                                                                         |                             |                          |                    |                   |               |  |  |  |  |

|                        |                                                                          | ator A is saturat<br>ator A is not sat                                                                                  |                             | en saturated at          | some time          |                   |               |  |  |  |  |

| bit 12                 | SB: Accumul                                                              | ator B Saturatio                                                                                                        | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                                             | ator B is saturat<br>ator B is not sat                                                                                  | ted or has bee              |                          | some time          |                   |               |  |  |  |  |

| bit 11                 |                                                                          |                                                                                                                         |                             | vorflow Status           | ы#(1)              |                   |               |  |  |  |  |

|                        |                                                                          | <b>OAB:</b> OA    OB Combined Accumulator Overflow Status bit <sup>(1)</sup><br>1 = Accumulators A or B have overflowed |                             |                          |                    |                   |               |  |  |  |  |

|                        |                                                                          | ccumulators A                                                                                                           |                             | erflowed                 |                    |                   |               |  |  |  |  |

| bit 10                 |                                                                          | B Combined Ad                                                                                                           |                             |                          | (1)                |                   |               |  |  |  |  |

|                        |                                                                          |                                                                                                                         |                             |                          | urated at some     | time              |               |  |  |  |  |

|                        | 0 = Neither A                                                            | ccumulators A                                                                                                           | or B are satur              | ated                     |                    |                   |               |  |  |  |  |

| bit 9                  | DA: DO Loop                                                              | Active bit <sup>(1)</sup>                                                                                               |                             |                          |                    |                   |               |  |  |  |  |

|                        | 1 = DO <b>loop is</b>                                                    | s in progress                                                                                                           |                             |                          |                    |                   |               |  |  |  |  |

|                        | 0 = DO <b>loop</b> is                                                    | s not in progres                                                                                                        | S                           |                          |                    |                   |               |  |  |  |  |

| bit 8                  | DC: MCU AL                                                               | U Half Carry/Bo                                                                                                         | orrow bit                   |                          |                    |                   |               |  |  |  |  |

|                        |                                                                          | out from the 4th sult occurred                                                                                          | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |  |  |  |  |

|                        | 0 = No carry                                                             |                                                                                                                         |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |  |  |  |  |

|                        | his bit is available                                                     |                                                                                                                         |                             |                          |                    |                   | -             |  |  |  |  |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1.                     |                                                                                                                         |                             |                          |                    |                   |               |  |  |  |  |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

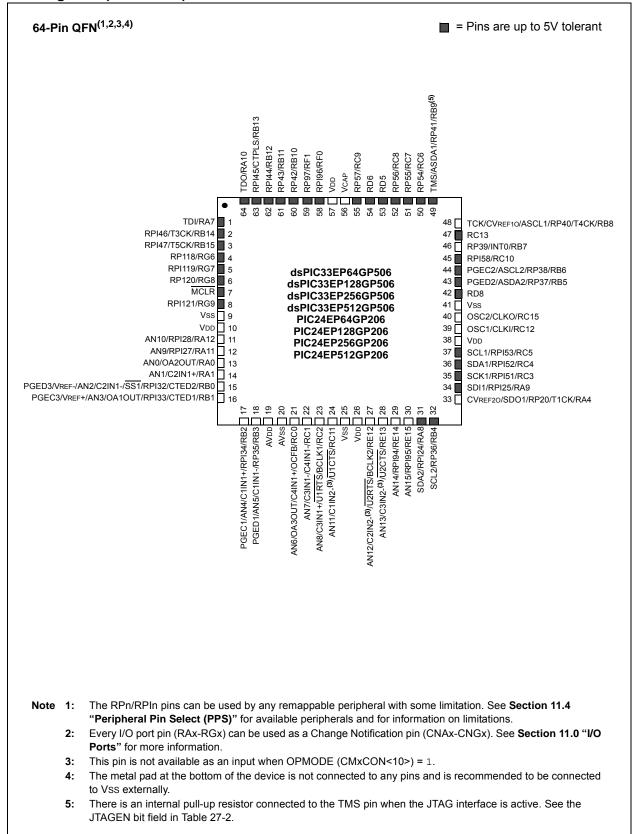

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

## FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

### TABLE 4-20: ADC1 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14             | Bit 13 | Bit 12  | Bit 11     | Bit 10    | Bit 9   | Bit 8        | Bit 7    | Bit 6    | Bit 5        | Bit 4     | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------------------|--------|---------|------------|-----------|---------|--------------|----------|----------|--------------|-----------|--------|--------|---------|---------|---------------|

| ADC1BUF0  | 0300  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 0  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF1  | 0302  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 1  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF2  | 0304  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 2  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF3  | 0306  |        | ADC1 Data Buffer 3 |        |         |            |           |         |              | xxxx     |          |              |           |        |        |         |         |               |

| ADC1BUF4  | 0308  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 4  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF5  | 030A  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 5  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF6  | 030C  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 6  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF7  | 030E  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 7  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF8  | 0310  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 8  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUF9  | 0312  |        |                    |        |         |            |           |         | ADC1 Data B  | uffer 9  |          |              |           |        |        |         |         | xxxx          |

| ADC1BUFA  | 0314  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 10 |          |              |           |        |        |         |         | xxxx          |

| ADC1BUFB  | 0316  |        |                    |        |         |            |           |         | ADC1 Data Bu | uffer 11 |          |              |           |        |        |         |         | xxxx          |

| ADC1BUFC  | 0318  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 12 |          |              |           |        |        |         |         | xxxx          |

| ADC1BUFD  | 031A  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 13 |          |              |           |        |        |         |         | xxxx          |

| ADC1BUFE  | 031C  |        |                    |        |         |            |           |         | ADC1 Data Bu | Iffer 14 |          |              |           |        |        |         |         | xxxx          |

| ADC1BUFF  | 031E  |        |                    |        |         |            |           |         | ADC1 Data Bu | iffer 15 |          |              |           |        |        |         |         | xxxx          |

| AD1CON1   | 0320  | ADON   | _                  | ADSIDL | ADDMABM | _          | AD12B     | FOR     | M<1:0>       | Ş        | SRC<2:0> | <b>`</b>     | SSRCG     | SIMSAM | ASAM   | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322  | ١      | VCFG<2:0>          | >      | _       | _          | CSCNA     | CHP     | S<1:0>       | BUFS     |          |              | SMPI<4:0> | >      |        | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _                  | _      |         |            | SAMC<4:03 | >       |              |          |          |              | ADCS      | <7:0>  |        |         |         | 0000          |

| AD1CHS123 | 0326  | _      | _                  | _      | _       | _          | CH123N    | NB<1:0> | CH123SB      | —        | _        | —            | _         | _      | CH123N | A<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  | _                  | _      |         | CH0SB<4:0> |           |         | CH0NA        | _        | —        | — CH0SA<4:0> |           |        |        | 0000    |         |               |

| AD1CSSH   | 032E  | CSS31  | CSS30              | _      | _       |            | CSS26     | CSS25   | CSS24        | _        |          | _            | —         | —      | —      | —       | —       | 0000          |

| AD1CSSL   | 0330  | CSS15  | CSS14              | CSS13  | CSS12   | CSS11      | CSS10     | CSS9    | CSS8         | CSS7     | CSS6     | CSS5         | CSS4      | CSS3   | CSS2   | CSS1    | CSS0    | 0000          |

| AD1CON4   | 0332  |        | _                  | _      | _       |            | _         | _       | ADDMAEN      | -        |          |              |           | _      | D      | MABL<2: | )>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                         | SV SI ACE BOON |              |                        |                |              |                        |  |

|-------------|---------------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|

| O/U,        |                           |                | Before       |                        | After          |              |                        |  |

| R/W         | Operation                 | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |

| O,<br>Read  |                           | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |

| O,<br>Read  | [++Wn]                    | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |

| O,<br>Read  | <b>Or</b><br>[Wn++]       | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |

| O,<br>Write |                           | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |

| U,<br>Read  |                           | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |

| U,<br>Read  | [Wn]<br><b>Or</b><br>[Wn] | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |

| U,<br>Read  | [ //11 - ]                | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |

## TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

#### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

#### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

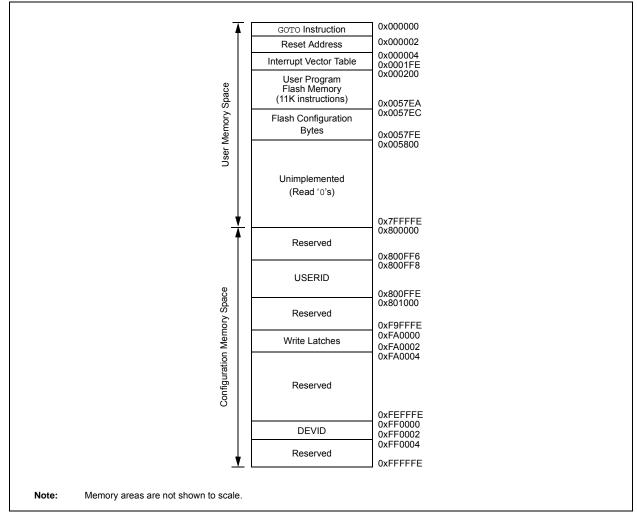

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |  |  |  |  |

|-------------------------|-----|-------|-------|--|--|--|--|

| Timer                   | 0   | 0     | х     |  |  |  |  |

| Gated Timer             | 0   | 1     | x     |  |  |  |  |

| Synchronous<br>Counter  | 1   | х     | 1     |  |  |  |  |

| Asynchronous<br>Counter | 1   | x     | 0     |  |  |  |  |

#### TABLE 12-1: TIMER MODE SETTINGS

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

### 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

| DC CHARACTERISTICS |        |                                                                     | $\begin{array}{ c c c c c c c c } \hline Standard Operating Conditions (see Note 1): 3.0V to 3.6V \\ \hline (unless otherwise stated) \\ \hline Operating temperature \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ for Extended} \end{array}$ |      |      |       |                 |  |  |

|--------------------|--------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                                      | Min.                                                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions      |  |  |

| Operating Voltage  |        |                                                                     |                                                                                                                                                                                                                                                                                                                     |      |      |       |                 |  |  |

| DC10               | Vdd    | Supply Voltage                                                      | 3.0                                                                                                                                                                                                                                                                                                                 |      | 3.6  | V     |                 |  |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | -                                                                                                                                                                                                                                                                                                                   | _    | Vss  | V     |                 |  |  |

| DC17               | Svdd   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.03                                                                                                                                                                                                                                                                                                                | _    | —    | V/ms  | 0V-1V in 100 ms |  |  |

#### TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

|              | Standard Operating Conditions (unless otherwise stated):         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |  |  |  |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Param<br>No. | Symbol Characteristics Min Typ Max Units Comments                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

|              | CEFC External Filter Capacitor 4.7 10 — μF Capacitor must have a low series resistance (< 1 Ohm)                                                                                                  |  |  |  |  |  |  |  |  |  |  |

**Note 1:** Typical VCAP voltage = 1.8 volts when VDD  $\geq$  VDDMIN.

| DC CHARACTE      | RISTICS                       |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                       |                 |  |  |  |  |

|------------------|-------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|--|--|

| Parameter<br>No. | Тур.                          | Max.          | Units                                                                                                                                                                                                                                                                                   | Units Conditions      |                 |  |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |  |  |

| DC60d            | 30                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |  |

| DC60a            | 35                            | 100           | μA                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |  |

| DC60b            | 150                           | 200           | μA                                                                                                                                                                                                                                                                                      | +85°C                 | 3.3V            |  |  |  |  |

| DC60c            | 250                           | 500           | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                         | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |  |  |

| DC60d            | 25                            | 100           | μA                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |  |

| DC60a            | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |  |

| DC60b            | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 0.0 V           |  |  |  |  |

| DC60c            | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |  |  |  |

| DC60d            | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |  |

| DC60a            | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |  |

| DC60b            | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.50            |  |  |  |  |

| DC60c            | 550                           | 1000          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |  |  |  |

| DC60d            | 35                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |  |

| DC60a            | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |  |

| DC60b            | 250                           | 450           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 5.57            |  |  |  |  |

| DC60c            | 1000                          | 1200          | μΑ                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E                                                                                                                                                                                                                                                                          | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |  |  |  |

| DC60d            | 40                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | -40°C                 |                 |  |  |  |  |

| DC60a            | 45                            | 100           | μΑ                                                                                                                                                                                                                                                                                      | +25°C                 | 3.3V            |  |  |  |  |

| DC60b            | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                      | +85°C                 | 0.0 v           |  |  |  |  |

| DC60c            | 1100                          | 1500          | μA                                                                                                                                                                                                                                                                                      | +125°C                |                 |  |  |  |  |

#### TABLE 30-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | R1 EXTERNAL CLOCK TIMING REQUIREMENTS <sup>(1)</sup> | ) |

|-------------------|------------------------------------------------------|---|

|-------------------|------------------------------------------------------|---|

| АС СН        | AC CHARACTERISTICS |                                                                                                    |                          |                                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |               |       |                                                                             |  |  |

|--------------|--------------------|----------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-----------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol             | Charao                                                                                             | cteristic <sup>(2)</sup> | Min.                                   | Тур.                                                                                                                                                                                                                                                                                    | Max.          | Units | Conditions                                                                  |  |  |

| TA10         | ТтхН               | T1CK High<br>Time                                                                                  | Synchronous<br>mode      | Greater of:<br>20 or<br>(Tcy + 20)/N   |                                                                                                                                                                                                                                                                                         | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |  |  |

|              |                    |                                                                                                    | Asynchronous             | 35                                     | _                                                                                                                                                                                                                                                                                       | —             | ns    |                                                                             |  |  |

| TA11         | ΤτχL               | T1CK Low<br>Time                                                                                   | Synchronous<br>mode      | Greater of:<br>20 or<br>(Tcy + 20)/N   | _                                                                                                                                                                                                                                                                                       | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |  |  |

|              |                    |                                                                                                    | Asynchronous             | 10                                     |                                                                                                                                                                                                                                                                                         | —             | ns    |                                                                             |  |  |

| TA15         | ΤτχΡ               | T1CK Input<br>Period                                                                               | Synchronous mode         | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _                                                                                                                                                                                                                                                                                       | —             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |  |  |

| OS60         | Ft1                | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                          | DC                                     |                                                                                                                                                                                                                                                                                         | 50            | kHz   |                                                                             |  |  |

| TA20         | TCKEXTMRL          | Delay from E<br>Clock Edge t<br>Increment                                                          | xternal T1CK<br>to Timer | 0.75 Tcy + 40                          | _                                                                                                                                                                                                                                                                                       | 1.75 Tcy + 40 | ns    |                                                                             |  |  |

Note 1: Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

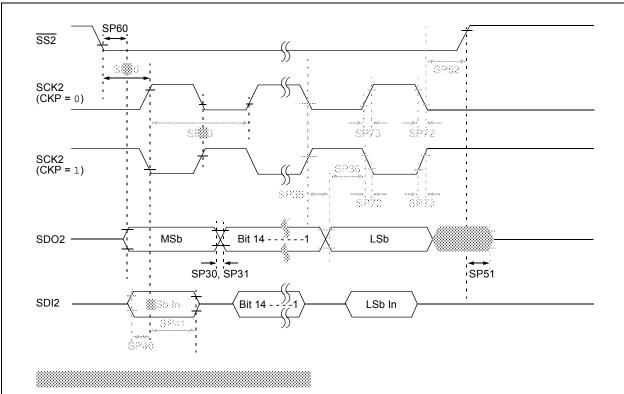

#### FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

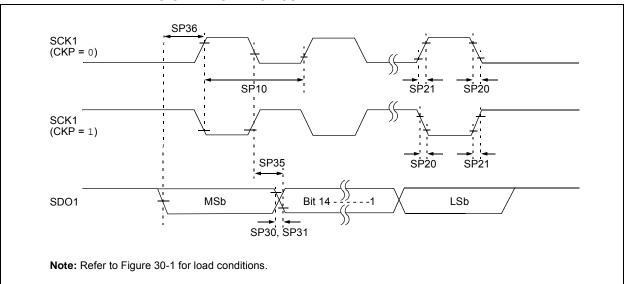

#### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10               | FscP                  | Maximum SCK1 Frequency                       | —                                                                                                                                                                                                                                                                                       |                     | 15   | MHz   | (Note 3)                       |

| SP20               | TscF                  | SCK1 Output Fall Time                        | -                                                                                                                                                                                                                                                                                       | -                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21               | TscR                  | SCK1 Output Rise Time                        | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | -                                                                                                                                                                                                                                                                                       | -                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                                                                                                      |                     |      | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

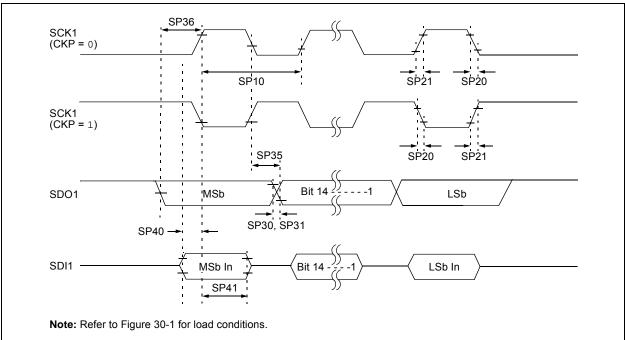

#### FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-43:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS