#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\mathbf{\cdot} \mathbf{X} \mathbf{F}$

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc202-e-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE        | 4-2:  | CPU C          | CORE RE | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES   | ONLY   |       |           |          |       |       |       |               |

|--------------|-------|----------------|---------|---------|---------|---------|--------|-------|----------|----------|--------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15         | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6  | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |                |         |         |         |         |        |       | W0 (WR   | EG)      |        |       |           |          |       |       |       | xxxx          |

| W1           | 0002  |                |         |         |         |         |        |       | W1       |          |        |       |           |          |       |       |       | xxxx          |

| W2           | 0004  |                |         |         |         |         |        |       | W2       |          |        |       |           |          |       |       |       | xxxx          |

| W3           | 0006  |                |         |         |         |         |        |       | W3       |          |        |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |                |         |         |         |         |        |       | W4       |          |        |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |                |         |         |         |         |        |       | W5       |          |        |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |                |         |         |         |         |        |       | W6       |          |        |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |                |         |         |         |         |        |       | W7       |          |        |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |                |         |         |         |         |        |       | W8       |          |        |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |                |         |         |         |         |        |       | W9       |          |        |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |                |         |         |         |         |        |       | W10      |          |        |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |                |         |         |         |         |        |       | W11      |          |        |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |                |         |         |         |         |        |       | W12      |          |        |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |                |         |         |         |         |        |       | W13      |          |        |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |                |         |         |         |         |        |       | W14      |          |        |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |                |         |         |         |         |        |       | W15      |          |        |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |                |         |         |         |         |        |       | SPLIM<1  | 5:0>     |        |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |                |         |         |         |         |        | P     | CL<15:1> |          |        |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —              | -       | _       | _       | —       | —      | —     | —        | _        |        |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —              | -       | _       | _       | —       | —      |       |          |          |        | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _              |         |         |         | _       |        | _     |          |          |        | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |                |         |         |         |         |        |       | RCOUNT<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _              |         |         |         | —       |        | —     | DC       | IPL2     | IPL1   | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR            | _       | -       | -       | —       |        | —     | _        | -        | _      | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | _              | _       |         |         |         |        |       |          | DISICNT< | :13:0> |       |           |          |       |       |       | 0000          |

| TBLPAG       | 0054  | _              | _       | -       | -       | —       |        | —     | _        |          |        |       | TBLPA     | G<7:0>   |       |       |       | 0000          |

| MSTRPR       | 0058  | MSTRPR<15:0> 0 |         |         |         |         |        |       |          |          | 0000   |       |           |          |       |       |       |               |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12        | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7 | Bit 6  | Bit 5           | Bit 4         | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|---------------|--------|--------|----------------|--------|-------|--------|-----------------|---------------|--------|----------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF        | U1RXIF | SPI1IF | SPI1EIF        | T3IF   | T2IF  | OC2IF  | IC2IF           | DMA0IF        | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF          | T4IF   | OC4IF  | OC3IF          | DMA2IF | _     | _      | _               | INT1IF        | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _             |        |        |                | _      | _     | IC4IF  | IC3IF           | DMA3IF        | C1IF   | C1RXIF   | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _             |        | QEI1IF | PSEMIF         | _      | _     | _      | _               | _             | _      | MI2C2IF  | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |               |        |        | -              | _      | _     | C1TXIF | _               | _             | CRCIF  | U2EIF    | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |               |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |               |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |               |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _             | _      |        |                | _      | _     | PTG3IF | PTG2IF          | PTG1IF        | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | <b>U1TXIE</b> | U1RXIE | SPI1IE | SPI1EIE        | T3IE   | T2IE  | OC2IE  | IC2IE           | DMA0IE        | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE          | T4IE   | OC4IE  | OC3IE          | DMA2IE | —     | _      | —               | INT1IE        | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _             | _      |        | _              | _      | _     | IC4IE  | IC3IE           | <b>DMA3IE</b> | C1IE   | C1RXIE   | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _             | _      | QEI1IE | PSEMIE         | _      | _     | _      | _               | _             | _      | MI2C2IE  | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _             |        |        | _              | _      | _     | C1TXIE | _               | _             | CRCIE  | U2EIE    | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _             | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _             | _      |        | _              | _      | _     | PTG3IE | PTG2IE          | PTG1IE        | PTG0IE | PTGWDTIE | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |               | _      |        | OC1IP<2:0      | >      | _     |        | IC1IP<2:0>      |               | _      |          | INT0IP<2:0>  |         | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |               | _      |        | OC2IP<2:0      | >      | _     |        | IC2IP<2:0>      |               | _      | [        | DMA0IP<2:0>  |         | 4444         |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >             | _      |        | SPI1IP<2:0     | )>     | _     |        | SPI1EIP<2:0     | >             |        |          | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _             | _      | C      | MA1IP<2:       | 0>     | _     |        | AD1IP<2:0>      |               |        |          | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |               | _      |        | CMIP<2:0       | >      | _     |        | MI2C1IP<2:0     | >             |        | 5        | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _             | _      |        | _              | _      | _     | _      | _               | _             |        |          | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |               | _      |        | OC4IP<2:0      | >      | _     |        | OC3IP<2:0>      |               |        | [        | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >             | _      | ι      | J2RXIP<2:      | 0>     | _     |        | INT2IP<2:0>     |               |        |          | T5IP<2:0>    |         | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |               | _      | C      | 2:<br>2:<br>2: | 0>     | _     |        | SPI2IP<2:0>     |               |        | 5        | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _             | _      |        | IC4IP<2:0      | >      | _     |        | IC3IP<2:0>      |               |        | [        | DMA3IP<2:0>  |         | 0444         |

| IPC12        | 0858  | _      | _      | _          | _             | _      | N      | 112C2IP<2:     | 0>     | _     |        | SI2C2IP<2:0     | >             | _      | _        | _            | _       | 0440         |

| IPC14        | 085C  | _      | _      | _          | _             | _      | (      | QEI1IP<2:(     | )>     | _     |        | PSEMIP<2:0      | >             | _      | _        | _            | _       | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >             | _      |        | U2EIP<2:0      |        | _     |        | U1EIP<2:0>      |               | _      | <u> </u> | _            | _       | 4440         |

| IPC17        | 0862  | _      | _      | _          | _             | _      |        | C1TXIP<2:      |        | _     | _      | _               | —             | _      | _        | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            | _             | _      |        |                |        |       |        | L<br>CTMUIP<2:0 | >             |        | <u> </u> | _            | _       | 0040         |

#### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

| File Name  | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8      | Bit 7      | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|-----------|--------|--------|--------|--------|--------|------------|------------|----------|--------|-------|-------|-------|--------|--------|---------------|

|            | 0400-<br>041E |        |           |        |        |        |        |        | See defini | ion when W | 'IN = x  |        |       |       |       |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BF      | P<3:0> |        |        | F2BI   | ><3:0> |            |            | F1BP     | <3:0>  |       |       | F0BP  | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BF      | ><3:0> |        |        | F6BI   | ><3:0> |            |            | F5BP     | <3:0>  |       |       | F4BP  | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11B      | P<3:0> |        |        | F10B   | P<3:0> |            |            | F9BP     | <3:0>  |       |       | F8BP  | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B      | P<3:0> |        |        | F14B   | P<3:0> |            |            | F13B     | D<3:0> |       |       | F12BF | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | MIDE  | _     | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXM1SID  | 0434          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | MIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXM2SID  | 0438          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | MIDE  | —     | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF0SID  | 0440          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       | -      |        | xxxx          |

| C1RXF1SID  | 0444          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | _     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |        | EID<15:8> |        |        |        |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF2SID  | 0448          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF3SID  | 044C          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF4SID  | 0450          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF5SID  | 0454          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF6SID  | 0458          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |           |        | EID<   | :15:8> |        |        |            |            |          |        | EID<  | 7:0>  |       |        |        | xxxx          |

| C1RXF8SID  | 0460          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |        | EID<15:8> |        |        |        |        |        |            |            |          |        | EID<  | -     |       |        |        | xxxx          |

| C1RXF9SID  | 0464          |        | SID<10:3> |        |        |        |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |        | EID<15:8> |        |        |        |        |        |            |            |          |        | EID<  |       |       |        |        | xxxx          |

| C1RXF10SID | 0468          |        |           |        |        | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | —     | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |        |           |        |        | :15:8> |        |        |            |            |          |        | EID<  | -     |       |        |        | xxxx          |

| C1RXF11SID | 046C          |        |           |        | SID<   | :10:3> |        |        |            |            | SID<2:0> |        | —     | EXIDE | -     | EID<   | 17:16> | xxxx          |

#### TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: NVM REGISTER MAP

| File Name                 | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|---------------------------|-------|--------|--------|--------|---------|--------|--------|-------|-------|---------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| NVMCON                    | 0728  | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _             | _     | _     | —     |       |       | 0000  |       |               |

| NVMADRL 072A NVMADR<15:0> |       |        |        |        |         |        |        |       |       |               |       |       | 0000  |       |       |       |       |               |

| NVMADRH                   | 072C  | _      | _      | _      | _       | -      | _      | _     | _     | NVMADR<23:16> |       |       |       |       |       |       |       | 0000          |

| NVMKEY                    | 072E  |        |        | _      | —       | _      |        | —     | -     | NVMKEY<7:0>   |       |       |       |       |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8    | Bit 7   | Bit 6  | Bit 5  | Bit 4   | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|--------|-----------|----------|---------|--------|--------|---------|-------|--------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _      | СМ        | VREGS    | EXTR    | SWR    | SWDTEN | WDTO    | SLEEP | IDLE   | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |        | NOSC<2:0> |          | CLKLOCK | IOLOCK | LOCK   | _       | CF    | _      | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | F      | RCDIV<2:0 | >        | PLLPOS  | T<1:0> | _      |         | F     | LLPRE< | 4:0>  |       | 0030          |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      |        |           |          |         |        | PLLD   | IV<8:0> |       |        |       |       | 0030          |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _      | _         | TUN<5:0> |         |        |        |         | 0000  |        |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

#### TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  |        | RODIV<3:0> |       |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| R/W-0           | R/W-0                           | R/W-1                             | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |

|-----------------|---------------------------------|-----------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|

| ROI             | DOZE2 <sup>(1)</sup>            | DOZE1 <sup>(1)</sup>              | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |

| bit 15          |                                 |                                   | •                    |                        |                    |                 | bit 8     |

|                 |                                 |                                   |                      |                        |                    |                 |           |

| R/W-0           | R/W-1                           | U-0                               | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |

| PLLPOST1        | PLLPOST0                        | —                                 | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |

| bit 7           |                                 |                                   |                      |                        |                    |                 | bit (     |

|                 |                                 |                                   |                      |                        |                    |                 |           |

| Legend:         |                                 |                                   |                      |                        |                    |                 |           |

| R = Readable    |                                 | W = Writable                      |                      | -                      | nented bit, read   |                 |           |

| -n = Value at F | POR                             | '1' = Bit is set                  |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |

| h:+ 45          |                                 | on Interview h                    |                      |                        |                    |                 |           |

| bit 15          |                                 | on Interrupt bis will clear the l |                      |                        |                    |                 |           |

|                 |                                 | s have no effect                  |                      | EN bit                 |                    |                 |           |

| bit 14-12       | •                               | Processor Clo                     |                      |                        |                    |                 |           |

|                 | 111 = Fcy div                   |                                   |                      |                        |                    |                 |           |

|                 | 110 = Fcy div                   | vided by 64                       |                      |                        |                    |                 |           |

|                 | 101 = Fcy div                   |                                   |                      |                        |                    |                 |           |

|                 | 100 = FCY div                   | vided by 16<br>vided by 8 (defa   | oult)                |                        |                    |                 |           |

|                 | 011 = FCY div<br>010 = FCY div  |                                   | auit)                |                        |                    |                 |           |

|                 | 001 = FCY div                   |                                   |                      |                        |                    |                 |           |

|                 | 000 = Fcy div                   | •                                 |                      |                        |                    |                 |           |

| bit 11          |                                 | e Mode Enable                     |                      |                        |                    |                 |           |

|                 |                                 |                                   |                      |                        | pheral clocks a    | nd the process  | or clocks |

|                 |                                 | -                                 | -                    | ratio is forced to     |                    |                 |           |

| bit 10-8        |                                 |                                   | RC Oscillator        | r Postscaler bit       | S                  |                 |           |

|                 | 111 = FRC di<br>110 = FRC di    |                                   |                      |                        |                    |                 |           |

|                 | 101 <b>= FRC di</b>             |                                   |                      |                        |                    |                 |           |

|                 | 100 <b>= FRC d</b> i            | vided by 16                       |                      |                        |                    |                 |           |

|                 | 011 = FRC di                    |                                   |                      |                        |                    |                 |           |

|                 | 010 = FRC di<br>001 = FRC di    | 2                                 |                      |                        |                    |                 |           |

|                 |                                 | vided by 2<br>vided by 1 (de      | fault)               |                        |                    |                 |           |

| bit 7-6         |                                 |                                   | -                    | r Select bits (al      | so denoted as      | 'N2', PLL posts | caler)    |

|                 | 11 = Output d                   |                                   |                      |                        |                    |                 | ,         |

|                 | 10 = Reserve                    |                                   |                      |                        |                    |                 |           |

|                 |                                 | livided by 4 (de                  | efault)              |                        |                    |                 |           |

| bit 5           | 00 = Output d                   | ted: Read as '                    | o'                   |                        |                    |                 |           |

|                 | •                               |                                   |                      |                        |                    |                 |           |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig |                                   | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |

| <b>2:</b> This  | s bit is cleared                | when the ROI I                    | oit is set and a     | an interrupt occ       | urs.               |                 |           |

|                 | DOJENUS                         |                                   |                      |                        | ~ ~                |                 | <i>.</i>  |

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

### REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

#### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| bit 7            |                      |                                    | bit 0 |

|------------------|----------------------|------------------------------------|-------|

|                  |                      |                                    |       |

| Legend:          | HS = Hardware Settal | ole bit                            |       |

| R = Readable bit | W = Writable bit     | U = Unimplemented bit, read as '0' |       |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup>

SYNCSEL0(4)

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

bit 15-9 Unimplemented: Read as '0'

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

bit 8

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

#### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

NOTES:

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x                                                            | R/W-x                                           | R/W-x                                        | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |

|------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------|---------------|------------------------------------|-------|--------------------|-------|--|--|--|

| EID5                                                             | EID4                                            | EID3                                         | EID2          | EID1                               | EID0  | RTR                | RB1   |  |  |  |

| bit 15                                                           |                                                 |                                              |               |                                    |       |                    | bit 8 |  |  |  |

|                                                                  |                                                 |                                              |               |                                    |       |                    |       |  |  |  |

| U-x                                                              | U-x                                             | U-x                                          | R/W-x         | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |

| —                                                                | —                                               | —                                            | RB0           | DLC3                               | DLC2  | DLC1               | DLC0  |  |  |  |

| bit 7                                                            |                                                 |                                              |               |                                    |       |                    | bit 0 |  |  |  |

| Lonondi                                                          |                                                 |                                              |               |                                    |       |                    |       |  |  |  |

| Legend:                                                          | l. h.:.                                         |                                              | L.11          |                                    |       | -l (O)             |       |  |  |  |

| R = Readab                                                       |                                                 | W = Writable                                 |               | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |

| -n = Value at POR                                                |                                                 | '1' = Bit is set                             |               | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |  |  |  |

|                                                                  |                                                 |                                              |               |                                    |       |                    |       |  |  |  |

| bit 15-10                                                        | EID<5:0>: E                                     | xtended Identifi                             | er bits       |                                    |       |                    |       |  |  |  |

| bit 9                                                            | RTR: Remot                                      | RTR: Remote Transmission Request bit         |               |                                    |       |                    |       |  |  |  |

|                                                                  | When IDE = 1:                                   |                                              |               |                                    |       |                    |       |  |  |  |

|                                                                  | •                                               | 1 = Message will request remote transmission |               |                                    |       |                    |       |  |  |  |

|                                                                  |                                                 | 0 = Normal message                           |               |                                    |       |                    |       |  |  |  |

|                                                                  |                                                 | When IDE = 0:                                |               |                                    |       |                    |       |  |  |  |

| The RTR bit is ignored.         bit 8 <b>RB1:</b> Reserved Bit 1 |                                                 |                                              |               |                                    |       |                    |       |  |  |  |

| bit 8                                                            |                                                 |                                              | or CAN proto  |                                    |       |                    |       |  |  |  |

|                                                                  | User must set this bit to '0' per CAN protocol. |                                              |               |                                    |       |                    |       |  |  |  |

| bit 7-5                                                          | •                                               | nted: Read as '                              | 0             |                                    |       |                    |       |  |  |  |

| bit 4                                                            | RB0: Reserv                                     |                                              | <b></b>       |                                    |       |                    |       |  |  |  |

|                                                                  | User must se                                    | et this bit to '0' p                         | per CAN proto | ocol.                              |       |                    |       |  |  |  |

| hit 2 0                                                          | DIC - 2:00 + Data Langth Cada hita              |                                              |               |                                    |       |                    |       |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

#### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x | R/W-x |

|------------------------------------|-------|-------|------------------|-----------------|-----------------|-------|-------|

|                                    |       |       | Ву               | /te 1           |                 |       |       |

| bit 15                             |       |       |                  |                 |                 |       | bit 8 |

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x | R/W-x |

|                                    |       |       | Ву               | rte 0           |                 |       |       |

| bit 7                              |       |       |                  |                 |                 |       | bit 0 |

| Legend:                            |       |       |                  |                 |                 |       |       |

| R = Readable bit W = Writable b    |       | bit   | U = Unimplen     | nented bit, rea | d as '0'        |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |       |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          |         | ADC Channel |         |

|----------------|---------|-------------|---------|

| value          | CH1     | CH2         | CH3     |

| 1 <b>(2)</b>   | OA1/AN3 | OA2/AN0     | OA3/AN6 |

| 0 <b>(1,2)</b> | OA2/AN0 | AN1         | AN2     |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

# 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                      |

|---------|------------------------|-------------|---------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                               |

|         |                        | 0001        | Reserved.                                                                                               |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                       |

|         |                        | 0011        | Reserved.                                                                                               |

|         |                        | 0100        | Reserved.                                                                                               |

|         |                        | 0101        | Reserved.                                                                                               |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                        |

|         |                        | 0111        | Reserved.                                                                                               |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                   |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                   |

|         |                        | 1010        | Reserved.                                                                                               |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = $0$ to $1$ ). |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                        |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                        |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                        |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                          |

|         | PTGADD <sup>(1)</sup>  | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                         |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                         |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                            |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                            |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                         |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                  |

|         |                        | 0110        | Reserved.                                                                                               |

|         |                        | 0111        | Reserved.                                                                                               |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                       |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                       |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                          |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                          |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                      |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                |

|         |                        | 1110        | Reserved.                                                                                               |

|         |                        | 1111        | Reserved.                                                                                               |

### TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a То comprehensive reference source. complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# 27.1 Configuration Bits

In dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 27-1.

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

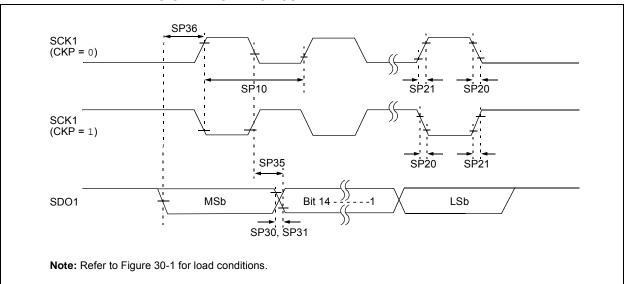

#### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

#### TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10               | FscP                  | Maximum SCK1 Frequency                       | —                                                                                                                                                                                                                                                                                     |                     | 15   | MHz   | (Note 3)                       |

| SP20               | TscF                  | SCK1 Output Fall Time                        | -                                                                                                                                                                                                                                                                                     | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21               | TscR                  | SCK1 Output Rise Time                        | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | -                                                                                                                                                                                                                                                                                     | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                                                                                                     | 6                   | 20   | ns    |                                |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                                                                                                    |                     |      | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

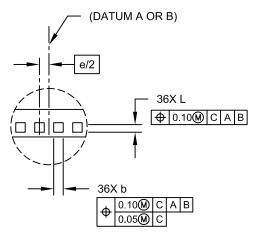

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |          |      |       |  |  |

|-------------------------|-------------|----------|------|-------|--|--|

| Dimension               | Limits      | MIN      | NOM  | MAX   |  |  |

| Number of Pins          | Ν           | 36       |      |       |  |  |

| Number of Pins per Side | ND          | 10       |      |       |  |  |

| Number of Pins per Side | NE          | 8        |      |       |  |  |

| Pitch                   | е           | 0.50 BSC |      |       |  |  |

| Overall Height          | Α           | 0.80     | 0.90 | 1.00  |  |  |

| Standoff                | A1          | 0.025    | -    | 0.075 |  |  |

| Overall Width           | E           | 5.00 BSC |      |       |  |  |

| Exposed Pad Width       | E2          | 3.60     | 3.75 | 3.90  |  |  |

| Overall Length          | D           | 5.00 BSC |      |       |  |  |

| Exposed Pad Length      | D2          | 3.60     | 3.75 | 3.90  |  |  |

| Contact Width           | b           | 0.20     | 0.25 | 0.30  |  |  |

| Contact Length          | L           | 0.20     | 0.25 | 0.30  |  |  |

| Contact-to-Exposed Pad  | К           | 0.20     | -    | -     |  |  |

#### Notes: