Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 70 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc202-i-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

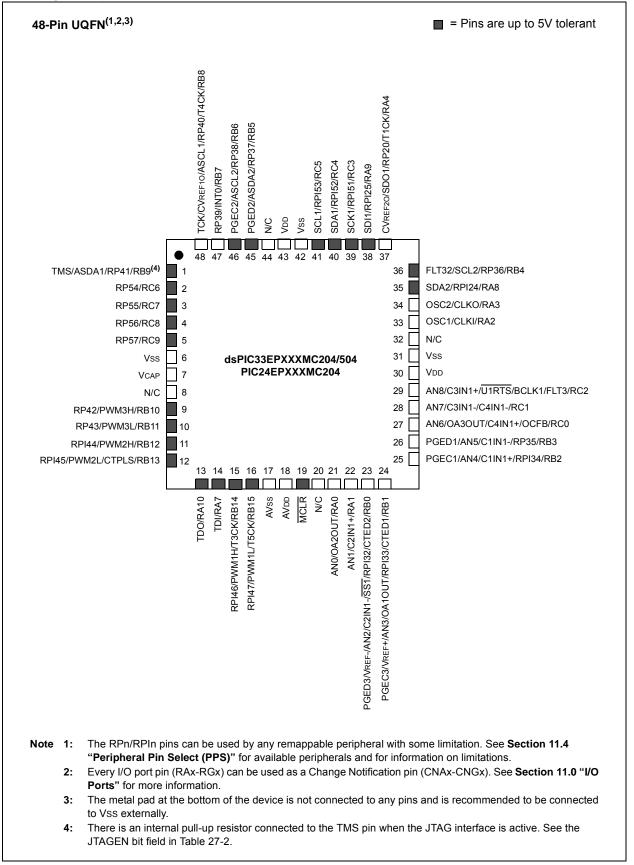

### Pin Diagrams (Continued)

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

### 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      | -          | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|--------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN  | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | -      | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |        |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN  | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | -      | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  |        |        |         |        |        |        | SPI2 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

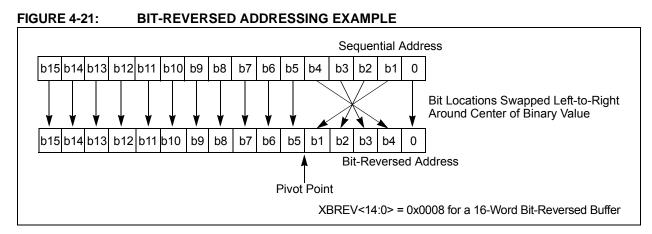

### TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |  |  |  |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|--|--|--|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |  |  |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |  |  |  |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |  |  |  |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |  |  |  |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |  |  |  |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |  |  |  |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |  |  |  |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |  |  |  |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |  |  |  |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |  |  |  |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |  |  |  |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |  |  |  |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |  |  |  |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |  |  |  |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |  |  |  |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |  |  |  |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |  |  |  |

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

#### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> 444 A                             | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | D M M A         | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | PTPE  | R<15:8>      |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | PTPE  | R<7:0>       |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 16-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

'1' = Bit is set

#### REGISTER 16-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | SEVTC | MP<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | SEVT  | CMP<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable bi  | t     | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

-n = Value at POR

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

NOTES:

#### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits <sup>(1)</sup>                     |

|---------|-----------------------------------------------------------------------------------------------------|

|         | 11111 = Open; use this selection with CTMU capacitive and time measurement                          |

|         | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP) |

|         | 11101 = Reserved                                                                                    |

|         | 11100 = Reserved                                                                                    |

|         | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>      |

|         | 11010 =  Channel 0 positive input is the output of OA3/AN0 <sup>(2)</sup>                           |

|         | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                            |

|         | 10110 = Reserved                                                                                    |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 10000 = Reserved                                                                                    |

|         | 01111 = Channel 0 positive input is AN15 <sup>(1,3)</sup>                                           |

|         | 01110 = Channel 0 positive input is AN14 <sup>(1,3)</sup>                                           |

|         | 01101 = Channel 0 positive input is AN13 <sup>(1,3)</sup>                                           |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 00010 = Channel 0 positive input is $AN2^{(1,3)}$                                                   |

|         | 00001 = Channel 0 positive input is $AN1^{(1,3)}$                                                   |

|         | 00000 = Channel 0 positive input is AN0 <sup>(1,3)</sup>                                            |

|         |                                                                                                     |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

## 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                          |

|---------|------------------------|-------------|-------------------------------------------------------------|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger. <sup>(3)</sup>                   |

|         | or (1)                 | 0001        | PWM master time base synchronization output. <sup>(3)</sup> |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt. <sup>(3)</sup>                              |

|         |                        | 0011        | PWM2 interrupt. <sup>(3)</sup>                              |

|         |                        | 0100        | PWM3 interrupt. <sup>(3)</sup>                              |

|         |                        | 0101        | Reserved.                                                   |

|         |                        | 0110        | Reserved.                                                   |

|         |                        | 0111        | OC1 Trigger event.                                          |

|         |                        | 1000        | OC2 Trigger event.                                          |

|         |                        | 1001        | IC1 Trigger event.                                          |

|         |                        | 1010        | CMP1 Trigger event.                                         |

|         |                        | 1011        | CMP2 Trigger event.                                         |

|         |                        | 1100        | CMP3 Trigger event.                                         |

|         |                        | 1101        | CMP4 Trigger event.                                         |

|         |                        | 1110        | ADC conversion done interrupt.                              |

|         |                        | 1111        | INT2 external interrupt.                                    |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0.                                   |

|         |                        | 0001        | Generate PTG Interrupt 1.                                   |

|         |                        | 0010        | Generate PTG Interrupt 2.                                   |

|         |                        | 0011        | Generate PTG Interrupt 3.                                   |

|         |                        | 0100        | Reserved.                                                   |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         | (2)                    | 1111        | Reserved.                                                   |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0.                                                      |

|         |                        | 00001       | PTGO1.                                                      |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | •           | •                                                           |

|         |                        | 11110       | PTGO30.                                                     |

|         |                        | 11111       | PTGO31.                                                     |

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

#### 25.3 Op Amp/Comparator Registers

| R/W-0                                                                                      | U-0                                                                                                                          | U-0                               | U-0                          | R-0                                | R-0                  | R-0                  | R-0                  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------|------------------------------------|----------------------|----------------------|----------------------|--|

| PSIDL                                                                                      |                                                                                                                              | _                                 | _                            | C4EVT <sup>(1)</sup>               | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT <sup>(1)</sup> |  |

| bit 15                                                                                     |                                                                                                                              |                                   | •                            |                                    |                      |                      | bit                  |  |

|                                                                                            |                                                                                                                              |                                   |                              |                                    |                      |                      |                      |  |

| U-0                                                                                        | U-0                                                                                                                          | U-0                               | U-0                          | R-0                                | R-0                  | R-0                  | R-0                  |  |

| _                                                                                          | —                                                                                                                            | _                                 | _                            | C4OUT <sup>(2)</sup>               | C3OUT <sup>(2)</sup> | C2OUT <sup>(2)</sup> | C10UT <sup>(2)</sup> |  |

| bit 7                                                                                      |                                                                                                                              |                                   |                              |                                    |                      |                      | bit                  |  |

|                                                                                            |                                                                                                                              |                                   |                              |                                    |                      |                      |                      |  |

| Legend:                                                                                    | - 1-:4                                                                                                                       |                                   | L:4                          |                                    |                      |                      |                      |  |

| R = Readabl                                                                                |                                                                                                                              | W = Writable                      |                              | U = Unimplemented bit, read as '0' |                      |                      |                      |  |

| -n = Value at                                                                              | PUR                                                                                                                          | '1' = Bit is se                   | [                            | '0' = Bit is clea                  | ared                 | x = Bit is unknown   |                      |  |

| bit 15                                                                                     |                                                                                                                              | narator Ston in                   | Idle Mode hit                |                                    |                      |                      |                      |  |

|                                                                                            | <b>PSIDL:</b> Comparator Stop in Idle Mode bit<br>1 = Discontinues operation of all comparators when device enters Idle mode |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            |                                                                                                                              |                                   |                              | rs in Idle mode                    |                      |                      |                      |  |

| bit 14-12                                                                                  | Unimplemen                                                                                                                   | ted: Read as                      | 0'                           |                                    |                      |                      |                      |  |

| bit 11                                                                                     | C4EVT: Op A                                                                                                                  | mp/Comparate                      | or 4 Event Sta               | atus bit <sup>(1)</sup>            |                      |                      |                      |  |

|                                                                                            | 1 = Op amp/comparator event occurred                                                                                         |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | <ul> <li>0 = Op amp/comparator event did not occur</li> <li>C3EVT: Comparator 3 Event Status bit<sup>(1)</sup></li> </ul>    |                                   |                              |                                    |                      |                      |                      |  |

| bit 10                                                                                     |                                                                                                                              |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | 1 = Comparator event occurred<br>0 = Comparator event did not occur                                                          |                                   |                              |                                    |                      |                      |                      |  |

| bit 9                                                                                      | •                                                                                                                            | parator 2 Ever                    |                              |                                    |                      |                      |                      |  |

|                                                                                            | 1 = Comparator event occurred                                                                                                |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | 0 = Comparator event did not occur                                                                                           |                                   |                              |                                    |                      |                      |                      |  |

| bit 8                                                                                      | C1EVT: Comparator 1 Event Status bit <sup>(1)</sup>                                                                          |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            |                                                                                                                              | tor event occu<br>tor event did n |                              |                                    |                      |                      |                      |  |

| bit 7-4                                                                                    | -                                                                                                                            |                                   |                              |                                    |                      |                      |                      |  |

| bit 7-4Unimplemented: Read as '0'bit 3C4OUT: Comparator 4 Output Status bit <sup>(2)</sup> |                                                                                                                              |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | When CPOL                                                                                                                    |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | 1 = VIN+ > VI                                                                                                                | N-                                |                              |                                    |                      |                      |                      |  |

|                                                                                            | 0 = VIN + < VI                                                                                                               |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | $\frac{\text{When CPOL}}{1 = \text{VIN} + < \text{VI}}$                                                                      |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | 0 = VIN + > VI                                                                                                               |                                   |                              |                                    |                      |                      |                      |  |

| bit 2                                                                                      | C3OUT: Com                                                                                                                   | parator 3 Outp                    | out Status bit <sup>(;</sup> | 2)                                 |                      |                      |                      |  |

|                                                                                            | When CPOL                                                                                                                    |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | 1 = VIN+ > VI<br>0 = VIN+ < VI                                                                                               |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | 0 = VIN + < VI<br>When CPOL                                                                                                  |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | 1 = VIN + < VII                                                                                                              |                                   |                              |                                    |                      |                      |                      |  |

|                                                                                            | $\perp = VIN + < VI$                                                                                                         | N-                                |                              |                                    |                      |                      |                      |  |

#### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

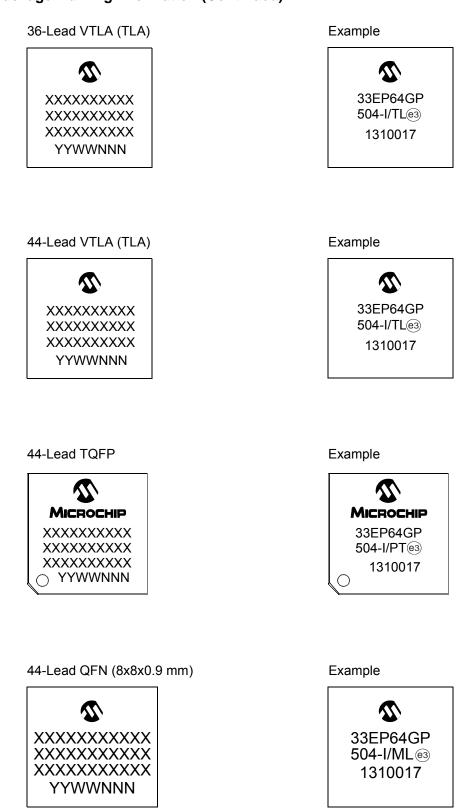

#### 33.1 Package Marking Information (Continued)

# **Revision D (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

#### TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>512-Kbyte Flash and<br>48-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | Removed the Analog Comparators column and updated the Op amps/Comparators column in Table 1 and Table 2.                                                                                                                                                                                                |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                                                                                 | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                       |

| Section 30.0 "Electrical<br>Characteristics"                                                                                                                            | Updated the VBOR specifications and/or its related note in the following electrical<br>characteristics tables:<br>• Table 30-1<br>• Table 30-4<br>• Table 30-12<br>• Table 30-14<br>• Table 30-15<br>• Table 30-16<br>• Table 30-56<br>• Table 30-57<br>• Table 30-58<br>• Table 30-59<br>• Table 30-60 |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: