Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 70 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc202-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

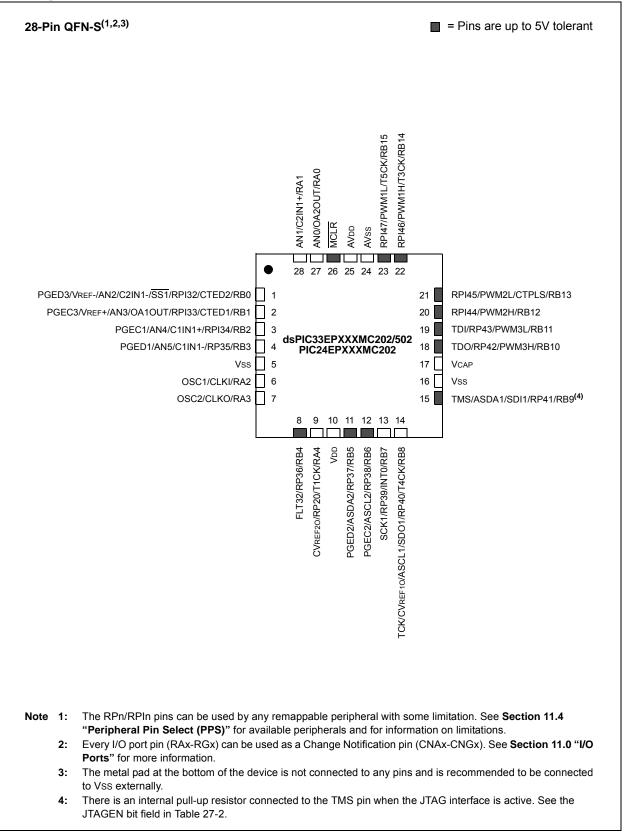

# Pin Diagrams (Continued)

| IABLE 4         | ABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |        |                  |          |            |            |          |          |             |        | r      |            |          |        |        |        |        |               |

|-----------------|-----------------------------------------------------------------------------------------|--------|------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr.                                                                                   | Bit 15 | Bit 14           | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0                                                                                    | QEIEN  | —                | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2                                                                                    | QCAPEN | FLTREN           |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4                                                                                    | _      | _                | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6                                                                                    |        |                  |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH        | 01C8                                                                                    |        |                  |          |            |            |          | ł        | POSCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| POS1HLD         | 01CA                                                                                    |        |                  |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT         | 01CC                                                                                    |        |                  |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL        | 01CE                                                                                    |        |                  |          |            |            |          |          | INTTMR<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRH        | 01D0                                                                                    |        | INTTMR<31:16> 00 |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| INT1HLDL        | 01D2                                                                                    |        |                  |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH        | 01D4                                                                                    |        |                  |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6                                                                                    |        |                  |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8                                                                                    |        |                  |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA                                                                                    |        |                  |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC                                                                                    |        |                  |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC                                                                                    |        |                  |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE                                                                                    |        |                  |          |            |            |          |          | QEIGEC<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI1ICH         | 01DE                                                                                    |        | QEIIC<31:16> 000 |          |            |            |          |          |             |        | 0000   |            |          |        |        |        |        |               |

| QEI1LECL        | 01E0                                                                                    |        |                  |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2                                                                                    |        |                  |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

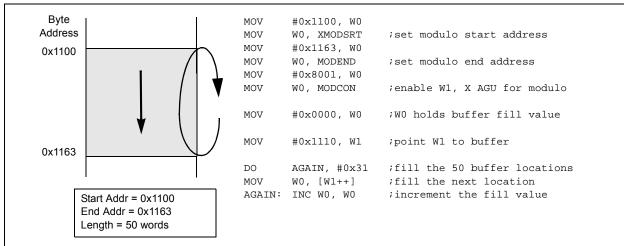

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

# 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

# FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

| R/W-1        | R/W-0                                                               | R/W-0                                     | U-0          | U-0              | U-0              | U-0             | U-0    |  |  |  |  |

|--------------|---------------------------------------------------------------------|-------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|--|--|

| GIE          | DISI                                                                | SWTRAP                                    |              |                  |                  | _               |        |  |  |  |  |

| bit 15       |                                                                     |                                           |              |                  |                  |                 | bit 8  |  |  |  |  |

|              |                                                                     |                                           |              |                  |                  |                 |        |  |  |  |  |

| U-0          | U-0                                                                 | U-0                                       | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|              | —                                                                   |                                           |              |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |  |

| bit 7        |                                                                     |                                           |              |                  |                  |                 | bit C  |  |  |  |  |

| Legend:      |                                                                     |                                           |              |                  |                  |                 |        |  |  |  |  |

| R = Readab   | le bit                                                              | W = Writable                              | bit          | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value a |                                                                     | '1' = Bit is set                          |              | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |  |

|              |                                                                     |                                           |              |                  |                  |                 |        |  |  |  |  |

| bit 15       | GIE: Global                                                         | Interrupt Enable                          | e bit        |                  |                  |                 |        |  |  |  |  |

|              | 1 = Interrupts and associated IE bits are enabled                   |                                           |              |                  |                  |                 |        |  |  |  |  |

|              |                                                                     | s are disabled, I                         | •            | still enabled    |                  |                 |        |  |  |  |  |

| bit 14       | DISI: DISI                                                          | nstruction Statu                          | s bit        |                  |                  |                 |        |  |  |  |  |

|              |                                                                     | struction is active<br>struction is not a | -            |                  |                  |                 |        |  |  |  |  |

| bit 13       | SWTRAP: Software Trap Status bit                                    |                                           |              |                  |                  |                 |        |  |  |  |  |

|              |                                                                     | e trap is enabled<br>e trap is disabled   |              |                  |                  |                 |        |  |  |  |  |

| bit 12-3     | Unimpleme                                                           | nted: Read as '                           | 0'           |                  |                  |                 |        |  |  |  |  |

| bit 2        | INT2EP: Ext                                                         | ternal Interrupt 2                        | 2 Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |                                                                     | on negative edg                           |              |                  |                  |                 |        |  |  |  |  |

| bit 1        | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit |                                           |              |                  |                  |                 |        |  |  |  |  |

|              |                                                                     | on negative edg                           |              |                  |                  |                 |        |  |  |  |  |

| bit 0        | INTOEP: Ext                                                         | ternal Interrupt C                        | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |  |

|              |                                                                     | on negative edg                           |              |                  |                  |                 |        |  |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

# 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                       | U-0              | U-0             | U-0                  | U-0              | U-0                | R/W-0   |

|-----------------|-------------------------------------------|------------------|-----------------|----------------------|------------------|--------------------|---------|

| _               | —                                         | —                |                 | —                    | —                | —                  | PLLDIV8 |

| bit 15          |                                           |                  |                 |                      |                  |                    | bit 8   |

|                 |                                           |                  |                 |                      |                  |                    |         |

| R/W-0           | R/W-0                                     | R/W-1            | R/W-1           | R/W-0                | R/W-0            | R/W-0              | R/W-0   |

| PLLDIV7         | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3              | PLLDIV2          | PLLDIV1            | PLLDIV0 |

| bit 7           |                                           |                  |                 |                      |                  |                    | bit 0   |

|                 |                                           |                  |                 |                      |                  |                    |         |

| Legend:         |                                           |                  |                 |                      |                  |                    |         |

| R = Readable    | bit                                       | W = Writable     | bit             | U = Unimpler         | mented bit, read | as '0'             |         |

| -n = Value at P | OR                                        | '1' = Bit is set |                 | '0' = Bit is cleared |                  | x = Bit is unknown |         |

|                 |                                           |                  |                 |                      |                  |                    |         |

| bit 15-9        | Unimplemen                                | ted: Read as '   | 0'              |                      |                  |                    |         |

| bit 8-0         | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted        | as 'M', PLL mul  | tiplier)           |         |

|                 | 111111111 =                               | = 513            |                 |                      |                  |                    |         |

|                 | •                                         |                  |                 |                      |                  |                    |         |

|                 | •                                         |                  |                 |                      |                  |                    |         |

|                 | •                                         |                  |                 |                      |                  |                    |         |

|                 | 000110000 =                               | = 50 (default)   |                 |                      |                  |                    |         |

|                 |                                           |                  |                 |                      |                  |                    |         |

|                 | •                                         |                  |                 |                      |                  |                    |         |

|                 | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                      |                  |                    |         |

|                 |                                           |                  |                 |                      |                  |                    |         |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

# 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

# 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

# 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32. NOTES:

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

# 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

# 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# 23.4 ADC Control Registers

### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                                                                                                                                                                                    | R/W-0                                                                   | R/W-0               | U-0               | R/W-0            | R/W-0             | R/W-0               |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|-------------------|------------------|-------------------|---------------------|--|--|--|--|

| ADON          | —                                                                                                                                                                                      | ADSIDL                                                                  | ADDMABM             |                   | AD12B            | FORM1             | FORM0               |  |  |  |  |

| bit 15        | •                                                                                                                                                                                      |                                                                         |                     |                   |                  |                   | bit 8               |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                  | R/W-0                                                                   | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS     | R/C-0. HC. HS       |  |  |  |  |

| SSRC2         | SSRC1                                                                                                                                                                                  | SSRC0                                                                   | SSRCG               | SIMSAM            | ASAM             | SAMP              | DONE <sup>(3)</sup> |  |  |  |  |

| bit 7         |                                                                                                                                                                                        |                                                                         |                     |                   |                  |                   | bit (               |  |  |  |  |

| Legend:       |                                                                                                                                                                                        | HC - Hardwar                                                            | e Clearable bit     | HS - Hardwa       | re Settable bit  | C = Clearable bi  | +                   |  |  |  |  |

| R = Readable  | a hit                                                                                                                                                                                  | W = Writable b                                                          |                     |                   | nented bit, read |                   | L                   |  |  |  |  |

| -n = Value at |                                                                                                                                                                                        | '1' = Bit is set                                                        | nt -                | '0' = Bit is clea |                  | x = Bit is unknov | vp.                 |  |  |  |  |

|               | FUR                                                                                                                                                                                    | I - DILIS SEL                                                           |                     |                   | aieu             | x – Bit is unknov |                     |  |  |  |  |

| bit 15        | ADON: ADO                                                                                                                                                                              | C1 Operating M                                                          | ode bit             |                   |                  |                   |                     |  |  |  |  |

|               | 1 = ADC mo<br>0 = ADC is 0                                                                                                                                                             | odule is operatir<br>off                                                | ng                  |                   |                  |                   |                     |  |  |  |  |

| bit 14        | Unimpleme                                                                                                                                                                              | nted: Read as                                                           | <b>'</b> 0 <b>'</b> |                   |                  |                   |                     |  |  |  |  |

| bit 13        | ADSIDL: A                                                                                                                                                                              | DC1 Stop in Idle                                                        | e Mode bit          |                   |                  |                   |                     |  |  |  |  |

|               | 1 = Discontinues module operation when device enters Idle mode                                                                                                                         |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               | 0 = Continues module operation in Idle mode                                                                                                                                            |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

| bit 12        | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                     |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               | 1 = DMA buffers are written in the order of conversion; the module provides an address to the DMA                                                                                      |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               | channel that is the same as the address used for the non-DMA stand-alone buffer<br>0 = DMA buffers are written in Scatter/Gather mode; the module provides a Scatter/Gather address to |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               |                                                                                                                                                                                        |                                                                         |                     |                   |                  | size of the DMA b |                     |  |  |  |  |

| bit 11        |                                                                                                                                                                                        | nted: Read as                                                           |                     |                   |                  |                   |                     |  |  |  |  |

| bit 10        | AD12B: AD                                                                                                                                                                              | C1 10-Bit or 12                                                         | -Bit Operation I    | Mode bit          |                  |                   |                     |  |  |  |  |

|               | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                    |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               | 0 = 10-bit, 4                                                                                                                                                                          | -channel ADC                                                            | operation           |                   |                  |                   |                     |  |  |  |  |

| bit 9-8       | FORM<1:0>                                                                                                                                                                              | Data Output I                                                           | Format bits         |                   |                  |                   |                     |  |  |  |  |

|               |                                                                                                                                                                                        | or 10-Bit Operation:                                                    |                     |                   |                  |                   |                     |  |  |  |  |

|               |                                                                                                                                                                                        | 1 = Signed fractional (Dout = sddd dddd dd00 0000, where s = .NOT.d<9>) |                     |                   |                  |                   |                     |  |  |  |  |

|               | 10 = Fractional (Dout = dddd  dddd  dd00  0000)<br>01 = Signed integer (Dout = ssss  sssd  dddd  dddd, where s = .NOT.d<9>)                                                            |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               | 01 = Signed integer (DOUT = ssss sssa aaaa aaaa aaaa, where s = .NOT.u<9>)<br>00 = Integer (DOUT = 0000 00dd dddd dddd)                                                                |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               | For 12-Bit C                                                                                                                                                                           | peration:                                                               |                     |                   |                  |                   |                     |  |  |  |  |

|               | 11 = Signed fractional (DOUT = sddd dddd dddd 0000, where s = .NOT.d<11>)                                                                                                              |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               | 10 = Fractional (DOUT = dddd dddd dddd 0000)<br>01 = Signed integer (DOUT = ssss sddd dddd dddd, where s = .NOT.d<11>)                                                                 |                                                                         |                     |                   |                  |                   |                     |  |  |  |  |

|               |                                                                                                                                                                                        |                                                                         |                     |                   |                  | (<11>)            |                     |  |  |  |  |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 3: Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

# 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                                                                                                         | R/W-0                                                                                                     | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------|------------------|------------------------------|-----------------|--------|--|--|--|--|

| ADCTS4     | ADCTS3                                                                                                                                        | ADCTS2                                                                                                    | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |  |  |  |  |

| bit 15     |                                                                                                                                               |                                                                                                           |                |                  |                              |                 | bit 8  |  |  |  |  |

| R/W-0      | R/W-0                                                                                                                                         | R/W-0                                                                                                     | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |

| OC4CS      |                                                                                                                                               | OC2CS                                                                                                     | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |  |  |  |  |

| bit 7      |                                                                                                                                               | 00100                                                                                                     |                |                  |                              |                 | bit (  |  |  |  |  |

| Legend:    |                                                                                                                                               |                                                                                                           |                |                  |                              |                 |        |  |  |  |  |

| R = Reada  | ble bit                                                                                                                                       | W = Writable                                                                                              | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |  |  |  |  |

| -n = Value | at POR                                                                                                                                        | '1' = Bit is set                                                                                          |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |  |  |  |  |

|            |                                                                                                                                               |                                                                                                           |                |                  |                              |                 |        |  |  |  |  |

| bit 15     | ADCTS4: Sa                                                                                                                                    | mple Trigger P                                                                                            | TGO15 for AE   | OC bit           |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                                                                                                  | es Trigger wher                                                                                           | the broadcas   | t command is     | executed                     |                 |        |  |  |  |  |

|            | 0 = Does not                                                                                                                                  | generate Trigg                                                                                            | er when the b  | roadcast com     | mand is execute              | ed              |        |  |  |  |  |

| bit 14     |                                                                                                                                               | mple Trigger P                                                                                            |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               | es Trigger wher                                                                                           |                |                  |                              | al              |        |  |  |  |  |

| bit 13     |                                                                                                                                               |                                                                                                           |                |                  | mand is execute              | a               |        |  |  |  |  |

| DIE 13     |                                                                                                                                               | ADCTS2: Sample Trigger PTGO13 for ADC bit<br>1 = Generates Trigger when the broadcast command is executed |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               |                                                                                                           |                |                  | mand is execute              | ed              |        |  |  |  |  |

| bit 12     |                                                                                                                                               | ADCTS1: Sample Trigger PTGO12 for ADC bit                                                                 |                |                  |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                                                                                                  | 1 = Generates Trigger when the broadcast command is executed                                              |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               |                                                                                                           |                |                  | mand is execute              | ed              |        |  |  |  |  |

| bit 11     | -                                                                                                                                             | IC4TSS: Trigger/Synchronization Source for IC4 bit                                                        |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               |                                                                                                           |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 10     | IC3TSS: Trig                                                                                                                                  | ger/Synchroniz                                                                                            | ation Source f | for IC3 bit      |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               |                                                                                                           |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 9      | IC2TSS: Trig                                                                                                                                  | ger/Synchroniz                                                                                            | ation Source f | for IC2 bit      |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               |                                                                                                           |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 8      |                                                                                                                                               | ger/Synchroniz                                                                                            |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               |                                                                                                           |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 7      | <ul> <li>Does not generate Trigger/Synchronization when the broadcast command is executed</li> <li>OC4CS: Clock Source for OC4 bit</li> </ul> |                                                                                                           |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               | es clock pulse v<br>generate clock                                                                        |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |

| bit 6      |                                                                                                                                               | ck Source for C                                                                                           | -              |                  |                              |                 |        |  |  |  |  |

|            |                                                                                                                                               | es clock pulse v<br>aenerate clock                                                                        |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |

| bit 5      |                                                                                                                                               | ck Source for C                                                                                           | -              |                  |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                                                                                                  | es clock pulse v                                                                                          | when the broad |                  | d is executed command is exe | cuted           |        |  |  |  |  |

|            | This register is rea<br>PTGSTRT = 1).                                                                                                         | -                                                                                                         |                |                  |                              |                 | and    |  |  |  |  |

|            | This register is on                                                                                                                           | lv used with the                                                                                          | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |  |  |  |  |

|            |                                                                                                                                               | .,                                                                                                        |                |                  | c.op commune                 | •               |        |  |  |  |  |

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

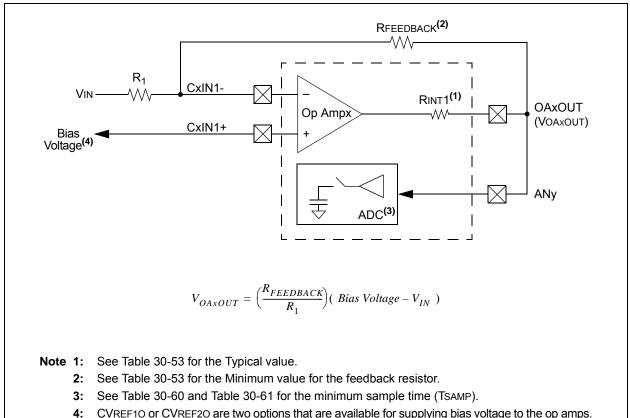

### 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

# 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

### REGISTER 25-1: CMSTAT: OP AMP/COMPARATOR STATUS REGISTER (CONTINUED)

- C2OUT: Comparator 2 Output Status bit<sup>(2)</sup> bit 1 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -C10UT: Comparator 1 Output Status bit<sup>(2)</sup> bit 0 When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN-When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- **Note 1:** Reflects the value of the of the CEVT bit in the respective Op Amp/Comparator Control register, CMxCON<9>.

- 2: Reflects the value of the COUT bit in the respective Op Amp/Comparator Control register, CMxCON<8>.

# 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| DC CHARACTERISTICS |      |      | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |        |       |  |  |  |

|--------------------|------|------|----------------------------------------------------------|--------|-------|--|--|--|

| Parameter No.      | Тур. | Max. | Units Conditions                                         |        |       |  |  |  |

| DC61d              | 8    |      | μΑ                                                       | -40°C  |       |  |  |  |

| DC61a              | 10   | —    | μA                                                       | +25°C  | 2.21/ |  |  |  |

| DC61b              | 12   | —    | μA                                                       | +85°C  | 3.3V  |  |  |  |

| DC61c              | 13   | —    | μA                                                       | +125°C |       |  |  |  |

# TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |    |               |       |            |      |                |  |  |

|-------------------------------------|-------------------------------------------------------|----|---------------|-------|------------|------|----------------|--|--|

| Parameter No. Typ. Max.             |                                                       |    | Doze<br>Ratio | Units | Conditions |      |                |  |  |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                       |    |               |       |            |      |                |  |  |

| DC73a <sup>(2)</sup>                | 35                                                    |    | 1:2           | mA    | -40°C      | 3.3V | Fosc = 140 MHz |  |  |

| DC73g                               | 20                                                    | 30 | 1:128         | mA    | -40 C      |      |                |  |  |

| DC70a <sup>(2)</sup>                | 35                                                    | _  | 1:2           | mA    | +25°C      | 3.3V | Fosc = 140 MHz |  |  |

| DC70g                               | 20                                                    | 30 | 1:128         | mA    | +25 C      |      |                |  |  |

| DC71a <sup>(2)</sup>                | 35                                                    | —  | 1:2           | mA    | 195%       | 3.3V |                |  |  |

| DC71g                               | 20                                                    | 30 | 1:128         | mA    | +85°C      |      | Fosc = 140 MHz |  |  |

| DC72a <sup>(2)</sup>                | 28                                                    | —  | 1:2           | mA    | +125°C     | 3.3V | Ecco - 120 MH- |  |  |

| DC72g                               | 15                                                    | 30 | 1:128         | mA    | +125 C     |      | Fosc = 120 MHz |  |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

| DC CHARACTERISTICS |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |     |   |                                                                                                                                                                        |  |

|--------------------|--------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                              | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                         |   |     |   |                                                                                                                                                                        |  |

| DO10 Vol           |        | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                                                                                                                                                                         |   | 0.4 | V | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}, -40^{\circ}\text{C} \le Ta \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}, +85^{\circ}\text{C} < Ta \le +125^{\circ}\text{C}$ |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                       |   | 0.4 | V |                                                                                                                                                                        |  |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                                     |   | _   | V | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                                                                     | _ | —   | V | $IOH \ge -15 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |  |

| DO20A              | Voн1   | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 1.5(1)                                                                                                                                                                                                                                                                                  | _ |     | V | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |  |

|                    |        |                                                             | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _ | _   |   | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                  |   | —   |   | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                    |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | — | —   | V | $IOH \geq -22  mA,  VDD = 3.3  V$                                                                                                                                      |  |

|                    |        |                                                             | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _ | —   |   | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                                                                          |  |