#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc202t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

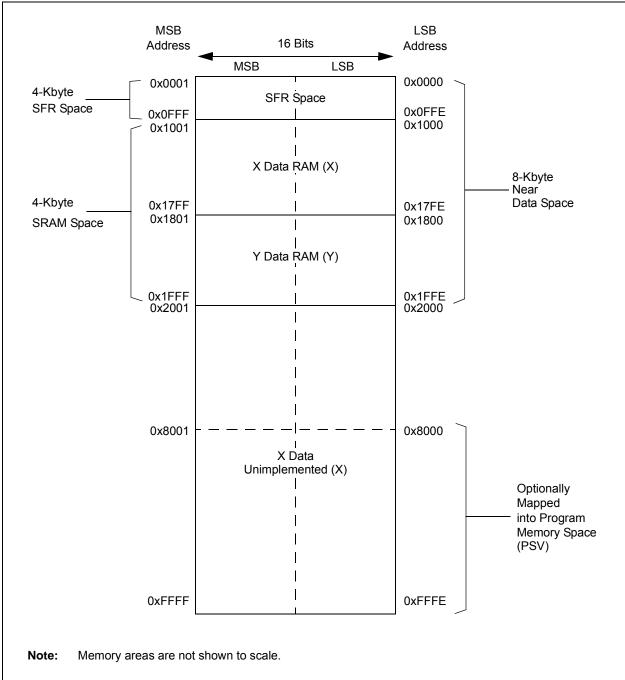

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

| TABLE        | 4-2:  | CPU C             | CORE RE | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES | ONLY  |       |           |          |       |       |       |               |

|--------------|-------|-------------------|---------|---------|---------|---------|--------|-------|----------|--------|-------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15            | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7  | Bit 6 | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |                   |         |         |         |         |        |       | W0 (WR   | EG)    |       |       |           |          |       |       |       | xxxx          |

| W1           | 0002  |                   |         |         |         |         |        |       | W1       |        |       |       |           |          |       |       |       | xxxx          |

| W2           | 0004  |                   |         |         |         |         |        |       | W2       |        |       |       |           |          |       |       |       | xxxx          |

| W3           | 0006  |                   |         |         |         |         |        |       | W3       |        |       |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |                   |         |         |         |         |        |       | W4       |        |       |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |                   |         |         |         |         |        |       | W5       |        |       |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |                   |         |         |         |         |        |       | W6       |        |       |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |                   |         |         |         |         |        |       | W7       |        |       |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |                   |         |         |         |         |        |       | W8       |        |       |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |                   |         |         |         |         |        |       | W9       |        |       |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |                   |         |         |         |         |        |       | W10      |        |       |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |                   |         |         |         |         |        |       | W11      |        |       |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |                   |         |         |         |         |        |       | W12      |        |       |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |                   |         |         |         |         |        |       | W13      |        |       |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |                   |         |         |         |         |        |       | W14      |        |       |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |                   |         |         |         |         |        |       | W15      |        |       |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |                   |         |         |         |         |        |       | SPLIM<1  | 5:0>   |       |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |                   |         |         |         |         |        | P     | CL<15:1> |        |       |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —                 | -       | _       | _       | —       | —      | —     | —        | _      |       |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —                 | -       | _       | _       | —       | —      |       |          |        |       | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _                 |         |         |         | _       |        | _     |          |        |       | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |                   |         |         |         |         |        |       | RCOUNT<  | 15:0>  |       |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _                 |         |         |         | _       |        | —     | DC       | IPL2   | IPL1  | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR               | _       | -       | -       | —       |        | —     | _        | -      | _     | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | — — DISICNT<13:0> |         |         |         |         |        | 0000  |          |        |       |       |           |          |       |       |       |               |

| TBLPAG       | 0054  | TBLPAG<7:0>       |         |         |         |         |        | 0000  |          |        |       |       |           |          |       |       |       |               |

| MSTRPR       | 0058  |                   |         |         |         |         |        |       | MSTRPR<  | 15:0>  |       |       |           |          |       |       |       | 0000          |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | —           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                 |       |                       |                         |         |         |         |            |         |          |         |        |       |       |        |          |          |        | All    |

|-----------------|-------|-----------------------|-------------------------|---------|---------|---------|------------|---------|----------|---------|--------|-------|-------|--------|----------|----------|--------|--------|

| File Name       | Addr. | Bit 15                | Bit 14                  | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9   | Bit 8    | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN                 | —                       | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN | PTGIVIS  | PTGSTRT | PTGWTO | _     | _     | —      | —        | PTGIT    | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F                     | PTGCLK<2                | :0>     |         | F       | PTGDIV<4:0 | >       |          |         | PTGPWD | <3:0> |       | _      | P        | TGWDT<2: | 0>     | 0000   |

| PTGBTE          | 0AC4  |                       | ADC                     | TS<4:1> |         | IC4TSS  | IC3TSS     | IC2TSS  | IC1TSS   | OC4CS   | OC3CS  | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS   | OC1TSS | 0000   |

| PTGHOLD         | 0AC6  |                       |                         |         |         |         |            |         | PTGHOLD  | <15:0>  |        |       |       |        |          |          |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |                       |                         |         |         |         |            |         | PTGT0LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGT1LIM        | 0ACA  |                       |                         |         |         |         |            |         | PTGT1LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGSDLIM        | 0ACC  |                       |                         |         |         |         |            |         | PTGSDLIN | l<15:0> |        |       |       |        |          |          |        | 0000   |

| <b>PTGC0LIM</b> | 0ACE  |                       |                         |         |         |         |            |         | PTGC0LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGC1LIM        | 0AD0  |                       |                         |         |         |         |            |         | PTGC1LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGADJ          | 0AD2  |                       |                         |         |         |         |            |         | PTGADJ<  | :15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGL0           | 0AD4  |                       |                         |         |         |         |            |         | PTGL0<   | 15:0>   |        |       |       |        |          |          |        | 0000   |

| PTGQPTR         | 0AD6  | —                     | —                       | —       | —       | _       | —          | —       | _        | —       | —      | -     |       | P      | TGQPTR<4 | 4:0>     |        | 0000   |

| PTGQUE0         | 0AD8  |                       |                         |         | STEP    | 1<7:0>  |            |         |          |         |        |       | STEPO | )<7:0> |          |          |        | 0000   |

| PTGQUE1         | 0ADA  |                       |                         |         | STEP    | '3<7:0> |            |         |          |         |        |       | STEP2 | 2<7:0> |          |          |        | 0000   |

| PTGQUE2         | 0ADC  |                       |                         |         | STEP    | 25<7:0> |            |         |          |         |        |       | STEP4 | <7:0>  |          |          |        | 0000   |

| PTGQUE3         | 0ADE  | STEP7<7:0> STEP6<7:0> |                         |         |         |         |            |         |          | 0000    |        |       |       |        |          |          |        |        |

| PTGQUE4         | 0AE0  | STEP9<7:0> STEP8<7:0> |                         |         |         |         |            |         |          |         | 0000   |       |       |        |          |          |        |        |

| PTGQUE5         | 0AE2  |                       |                         |         | STEP    | 11<7:0> |            |         |          |         |        |       | STEP1 | 0<7:0> |          |          |        | 0000   |

| PTGQUE6         | 0AE4  |                       |                         |         | STEP    | 13<7:0> |            |         |          |         |        |       | STEP1 | 2<7:0> |          |          |        | 0000   |

| PTGQUE7         | 0AE6  |                       | STEP15<7:0> STEP14<7:0> |         |         |         |            |         |          |         | 0000   |       |       |        |          |          |        |        |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

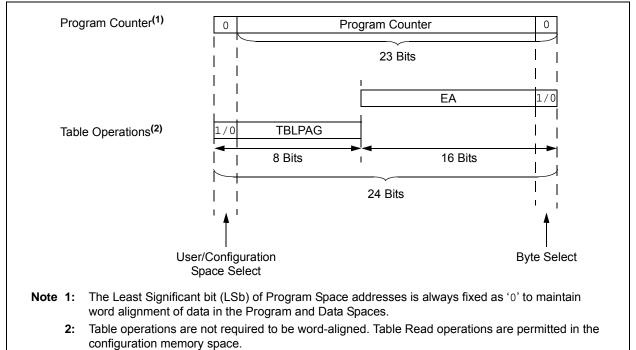

# 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address        |           |          |               |     |  |  |  |  |  |

|------------------------|---------------|------------------------------|-----------|----------|---------------|-----|--|--|--|--|--|

| Access Type            | Space         | <23>                         | <22:16>   | <15>     | <14:1>        | <0> |  |  |  |  |  |

| Instruction Access     | User          | 0                            | PC<22:1>  |          |               |     |  |  |  |  |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |          |               |     |  |  |  |  |  |

| TBLRD/TBLWT            | User          | TB                           | LPAG<7:0> |          | Data EA<15:0> |     |  |  |  |  |  |

| (Byte/Word Read/Write) |               | 0                            | xxx xxxx  | XXXX XXX | ***           |     |  |  |  |  |  |

|                        | Configuration | TB                           | LPAG<7:0> |          | Data EA<15:0> |     |  |  |  |  |  |

|                        |               | 1                            | xxx xxxx  | XXXX XX  | ***           |     |  |  |  |  |  |

## FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ol> <li>1 = Device was in Idle mode</li> <li>0 = Device was not in Idle mode</li> </ol>                                |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred<br>0 = A Brown-out Reset has not occurred    |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|-------|-------------------|------------------|-----------------|-------|

|                                    |       |       | PAD   | <15:8>            |                  |                 |       |

| bit 15                             |       |       |       |                   |                  |                 | bit 8 |

|                                    |       |       |       |                   |                  |                 |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                                    |       |       | PAE   | )<7:0>            |                  |                 |       |

| bit 7                              |       |       |       |                   |                  |                 | bit 0 |

|                                    |       |       |       |                   |                  |                 |       |

| Legend:                            |       |       |       |                   |                  |                 |       |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                                                 | U-0   | R/W-0          | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|-----------------------------------------------------|-------|----------------|-------|------------------|------------------|-----------------|-------|

| —                                                   |       |                |       | CNT<             | 13:8> <b>(2)</b> |                 |       |

| bit 15                                              |       |                |       |                  |                  |                 | bit 8 |

| R/W-0                                               | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|                                                     |       |                | CNT<  | <7:0> <b>(2)</b> |                  |                 |       |

| bit 7                                               |       |                |       |                  |                  |                 | bit 0 |

| Legend:                                             |       |                |       |                  |                  |                 |       |

| R = Readable b                                      | oit   | W = Writable b | bit   | U = Unimplen     | nented bit, rea  | id as '0'       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cle |       |                |       |                  | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

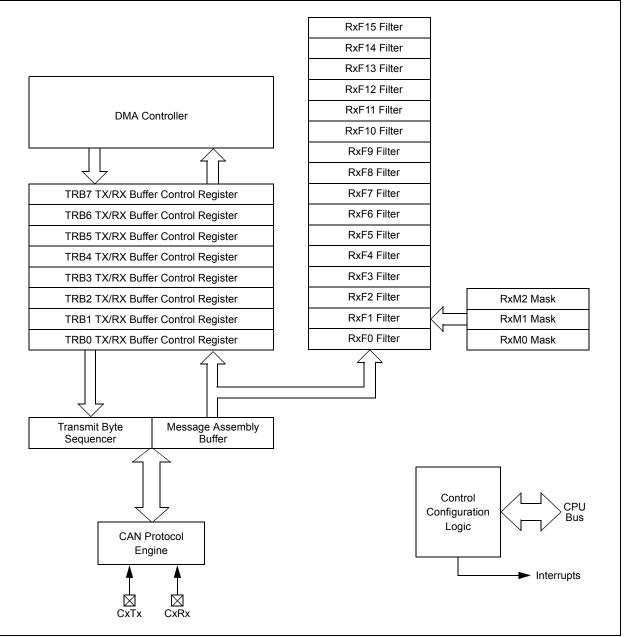

| REGISTER 21-20: | CxRXMnSID: ECANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER |

|-----------------|---------------------------------------------------------------|

|                 | REGISTER (n = 0-2)                                            |

|              |               | -                                        | -             |                                                 |       |       |       |  |  |

|--------------|---------------|------------------------------------------|---------------|-------------------------------------------------|-------|-------|-------|--|--|

| R/W-x        | R/W-x         | R/W-x                                    | R/W-x         | R/W-x                                           | R/W-x | R/W-x | R/W-x |  |  |

| SID10        | SID9          | SID8                                     | SID7          | SID6                                            | SID5  | SID4  | SID3  |  |  |

| bit 15       |               |                                          |               |                                                 |       |       | bit 8 |  |  |

| R/W-x        | R/W-x         | R/W-x                                    | U-0           | R/W-x                                           | U-0   | R/W-x | R/W-x |  |  |

| SID2         | SID1          | SID0                                     | -             | MIDE                                            | _     | EID17 | EID16 |  |  |

| bit 7        |               |                                          |               |                                                 |       |       | bit C |  |  |

| <u> </u>     |               |                                          |               |                                                 |       |       |       |  |  |

| Legend:      |               |                                          |               |                                                 |       |       |       |  |  |

| R = Readab   | ole bit       | W = Writable                             | bit           | U = Unimplemented bit, read as '0'              |       |       |       |  |  |

| -n = Value a | at POR        | '1' = Bit is set                         | :             | '0' = Bit is cleared x = Bit is unknown         |       |       |       |  |  |

| bit 15-5     | SID<10:0>: S  | Standard Identi                          | fier bits     |                                                 |       |       |       |  |  |

|              |               | bit, SIDx, in filte<br>is a don't care i |               |                                                 |       |       |       |  |  |

| bit 4        | Unimplemer    | nted: Read as '                          | 0'            |                                                 |       |       |       |  |  |

| bit 3        | MIDE: Identif | fier Receive Mo                          | de bit        |                                                 |       |       |       |  |  |

|              | 0 = Matches   |                                          | or extended a | d or extended ac<br>address messag<br>SID/EID)) |       | •     |       |  |  |

| bit 2        | Unimplemer    | Unimplemented: Read as '0'               |               |                                                 |       |       |       |  |  |

| bit 1-0      | EID<17:16>:   | Extended Iden                            | tifier bits   |                                                 |       |       |       |  |  |

|              |               | bit, EIDx, in fill<br>is a don't care    |               |                                                 |       |       |       |  |  |

|              |               |                                          |               |                                                 |       |       |       |  |  |

#### REGISTER 21-21: CxRXMnEID: ECANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R = Readable bit W = Writable bit |       |       | bit   | U = Unimplemented bit, read as '0' |       |       |       |

|-----------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|

| Legend:                           |       |       |       |                                    |       |       |       |

| bit 7                             |       |       |       |                                    |       |       | bit 0 |

| EID7                              | EID6  | EID5  | EID4  | EID3                               | EID2  | EID1  | EID0  |

| R/W-x                             | R/W-x | R/W-x | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |

|                                   |       |       |       |                                    |       |       | 511.0 |

| bit 15                            | •     |       | •     | •                                  |       |       | bit 8 |

| EID15                             | EID14 | EID13 | EID12 | EID11                              | EID10 | EID9  | EID8  |

| R/W-x                             | R/W-x | R/W-x | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Includes bit, EIDx, in filter comparison

0 = EIDx bit is a don't care in filter comparison

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|--------|-----|-----|-----|-----|----------|----------|---------|

| —      | —   | —   | —   | -   | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |     |     |     |     |          |          | bit 8   |

|        |     |     |     |     |          |          |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | —   | —   | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

# Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

**CH123NB<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXB bits In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|--|

| Value           | CH1         | CH2   | CH3   |  |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |  |

| 0x              | Vrefl       | VREFL | Vrefl |  |  |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |  |

|----------------|-------------|---------|---------|--|--|--|--|

| value          | CH1         | CH2     | CH3     |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|--|

| Value           | CH1         | CH2   | CH3   |  |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |  |

| 0x              | VREFL       | Vrefl | Vrefl |  |  |  |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

| CSS15                             | CSS14 | CSS13            | CSS12                              | CSS11                | CSS10 | CSS9               | CSS8  |

| bit 15                            |       |                  |                                    | ·                    | •     | ·                  | bit 8 |

|                                   |       |                  |                                    |                      |       |                    |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

| CSS7                              | CSS6  | CSS5             | CSS4                               | CSS3                 | CSS2  | CSS1               | CSS0  |

| bit 7                             | -     |                  |                                    |                      | •     |                    | bit ( |

|                                   |       |                  |                                    |                      |       |                    |       |

| Legend:                           |       |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

# REGISTER 23-8: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

bit 15-0 CSS<15:0>: ADC1 Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all AD1CSSL bits can be selected by the user. However, inputs selected for scan, without a corresponding input on the device, convert VREFL.

**2:** CSSx = ANx, where x = 0-15.

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0           | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|-----------------|-----------|-------|-------|-------|

|                                                                      |       |       | PTGSD           | LIM<15:8> |       |       |       |

| bit 15                                                               |       |       |                 |           |       |       | bit 8 |

|                                                                      |       |       |                 |           |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0           | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |       | PTGSE           | )LIM<7:0> |       |       |       |

| bit 7                                                                |       |       |                 |           |       |       | bit 0 |

|                                                                      |       |       |                 |           |       |       |       |

| Legend:                                                              |       |       |                 |           |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |                 |           |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is   |       |       | x = Bit is unkr | nown      |       |       |       |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|

|                 |       |                  | PTGC0 | LIM<15:8>                          |       |                 |       |  |

| bit 15          |       |                  |       |                                    |       |                 | bit 8 |  |

|                 |       |                  |       |                                    |       |                 |       |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|                 |       |                  | PTGC  | )LIM<7:0>                          |       |                 |       |  |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |  |

|                 |       |                  |       |                                    |       |                 |       |  |

| Legend:         |       |                  |       |                                    |       |                 |       |  |

| R = Readable    | bit   | W = Writable bi  | it    | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unki | nown  |  |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|----------------|-------|-------|--------|---------|-------|-------|-------|--|--|--|

| PTGC1LIM<15:8> |       |       |        |         |       |       |       |  |  |  |

| bit 15         |       |       |        |         |       |       | bit 8 |  |  |  |

|                |       |       |        |         |       |       |       |  |  |  |

| R/W-0          | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|                |       |       | PTGC1L | IM<7:0> |       |       |       |  |  |  |

| bit 7          |       |       |        |         |       |       | bit C |  |  |  |

| Legena.           |                  |                       |                                    |  |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |  |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

# REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGHOLD<15:8> |       |       |       |       |       |       |       |  |

| bit 15        |       |       |       |       |       |       | bit 8 |  |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGHOLD<7:0> |       |       |       |       |       |       |       |  |

| bit 7 bi     |       |       |       |       |       |       |       |  |

| Legend:           |                                                         |                      |                    |  |  |

|-------------------|---------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                        | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

NOTES:

| DC CHARACTERISTICS |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                                                                                            |  |

|--------------------|--------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                              | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions                                                                                                                                                                                 |  |

| DO10 Vol           |        | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |                                                                                                                                                                                                                                                                                         |      | 0.4  | V     | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}$ , $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}$ , $+85^{\circ}\text{C} < \text{TA} \le +125^{\circ}\text{C}$ |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>    | _                                                                                                                                                                                                                                                                                       |      | 0.4  | V     |                                                                                                                                                                                            |  |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup> | 2.4                                                                                                                                                                                                                                                                                     |      | _    | V     | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                      |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup> | 2.4                                                                                                                                                                                                                                                                                     | _    | —    | V     | $IOH \ge -15 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                                      |  |

| DO20A              | Von1   | Output High Voltage                                         | 1.5(1)                                                                                                                                                                                                                                                                                  | _    |      | V     | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                                       |  |

|                    |        | 4x Source Driver Pins <sup>(2)</sup>                        | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _    | _    |       | $IOH \geq -12 ~mA, ~VDD = 3.3 V$                                                                                                                                                           |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                  | _    |      |       | $IOH \geq -7 \; mA,  VDD = 3.3 V$                                                                                                                                                          |  |

|                    |        | Output High Voltage                                         | 1.5 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _    | —    | V     | $IOH \geq \textbf{-22 mA, VDD} = 3.3V$                                                                                                                                                     |  |

|                    |        | 8x Source Driver Pins <sup>(3)</sup>                        | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                      | _    | —    | 1     | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                                                                                              |  |

|                    |        |                                                             | 3.0(1)                                                                                                                                                                                                                                                                                  | _    | —    | 1     | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                                                                                              |  |

# TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<7:15> and RC3

For 64-pin devices: RA4, RA9, RB<7:15>, RC3 and RC15

## TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                        |

|--------------------|--------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------|

| Param<br>No.       | Symbol | Characteristic                             | Min. <sup>(2)</sup>                                                                                                                                                                                                                                                                           | Тур. | Max. | Units | Conditions             |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low | 2.65                                                                                                                                                                                                                                                                                          | _    | 2.95 | V     | VDD<br>(Notes 2 and 3) |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance.

**2:** Parameters are for design guidance only and are not tested in manufacturing.

3: The VBOR specification is relative to VDD.

# TABLE 30-39:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| АС СНА | AC CHARACTERISTICS    |                                              |              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                |  |  |

|--------|-----------------------|----------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.         | Typ. <sup>(2)</sup>                                                                                                                                                                                                                                                                   | Max. | Units | Conditions                     |  |  |

| SP70   | FscP                  | Maximum SCK2 Input Frequency                 | —            | —                                                                                                                                                                                                                                                                                     | 15   | MHz   | (Note 3)                       |  |  |

| SP72   | TscF                  | SCK2 Input Fall Time                         | —            | —                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO32 (Note 4)    |  |  |

| SP73   | TscR                  | SCK2 Input Rise Time                         | —            | _                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO31<br>(Note 4) |  |  |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                   | —            | —                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO32 (Note 4)    |  |  |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                   | —            | _                                                                                                                                                                                                                                                                                     | _    | ns    | See Parameter DO31 (Note 4)    |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —            | 6                                                                                                                                                                                                                                                                                     | 20   | ns    |                                |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30           | —                                                                                                                                                                                                                                                                                     | _    | ns    |                                |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge   | 30           | —                                                                                                                                                                                                                                                                                     | _    | ns    |                                |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge    | 30           | —                                                                                                                                                                                                                                                                                     | _    | ns    |                                |  |  |

| SP50   | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓<br>Input           | 120          | —                                                                                                                                                                                                                                                                                     | _    | ns    |                                |  |  |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance       | 10           | —                                                                                                                                                                                                                                                                                     | 50   | ns    | (Note 4)                       |  |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                        | 1.5 TCY + 40 | —                                                                                                                                                                                                                                                                                     |      | ns    | (Note 4)                       |  |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

# TABLE 30-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | rics                                         | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |                    |       |                                |

|--------|-----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|-------|--------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                 | Тур. <sup>(2)</sup> | Max.               | Units | Conditions                     |

| SP70   | FscP                  | Maximum SCK1 Input<br>Frequency              | _                                                                                                                                                                                                    |                     | Lesser of FP or 15 | MHz   | (Note 3)                       |

| SP72   | TscF                  | SCK1 Input Fall Time                         | _                                                                                                                                                                                                    |                     |                    | ns    | See Parameter DO32<br>(Note 4) |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                    |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                    |                     | _                  | ns    | See Parameter DO32<br>(Note 4) |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                    |                     | —                  | ns    | See Parameter DO31<br>(Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                    | 6                   | 20                 | ns    |                                |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                   |                     | _                  | ns    |                                |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                                                                                                                                                                   |                     |                    | ns    |                                |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                                                                                                                                                                   |                     | —                  | ns    |                                |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                                                                                                                                                                  |                     | —                  | ns    |                                |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                                                                                                                                                                   | _                   | 50                 | ns    | (Note 4)                       |

| SP52   | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40                                                                                                                                                                                         | _                   | _                  | ns    | (Note 4)                       |

| SP60   | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge     | —                                                                                                                                                                                                    | _                   | 50                 | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| AC CHA       | ARACTER | RISTICS                                                                                             | (unless   | otherwis  | e stated) <sup>(</sup> | 1)    | 0V to 3.6V                                             |

|--------------|---------|-----------------------------------------------------------------------------------------------------|-----------|-----------|------------------------|-------|--------------------------------------------------------|

|              |         |                                                                                                     | Operatir  | ng temper |                        |       | $\leq$ +85°C for Industrial $\leq$ +125°C for Extended |

| Param<br>No. | Symbol  | Characteristic                                                                                      | Min.      | Тур.      | Max.                   | Units | Conditions                                             |

|              |         | Cloci                                                                                               | k Parame  | eters     |                        |       |                                                        |

| AD50         | TAD     | ADC Clock Period                                                                                    | 76        | _         | _                      | ns    |                                                        |

| AD51         | tRC     | ADC Internal RC Oscillator Period <sup>(2)</sup>                                                    |           | 250       | _                      | ns    |                                                        |

|              |         | Conv                                                                                                | version F | Rate      |                        | •     |                                                        |

| AD55         | tCONV   | Conversion Time                                                                                     |           | 12 Tad    | _                      |       |                                                        |

| AD56         | FCNV    | Throughput Rate                                                                                     | _         | —         | 1.1                    | Msps  | Using simultaneous sampling                            |

| AD57a        | TSAMP   | Sample Time when Sampling any ANx Input                                                             | 2 Tad     | —         | _                      | —     |                                                        |

| AD57b        | TSAMP   | Sample Time when Sampling the Op Amp Outputs (Configuration A and Configuration B) <sup>(4,5)</sup> | 4 Tad     | _         | —                      | —     |                                                        |

|              |         | Timin                                                                                               | g Param   | eters     |                        |       |                                                        |

| AD60         | tPCS    | Conversion Start from Sample<br>Trigger <sup>(2,3)</sup>                                            | 2 Tad     | —         | 3 Tad                  | _     | Auto-convert trigger is<br>not selected                |

| AD61         | tPSS    | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2,3))</sup>                                    | 2 Tad     | —         | 3 Tad                  | —     |                                                        |

| AD62         | tcss    | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2,3)</sup>                                | _         | 0.5 Tad   |                        | —     |                                                        |

| AD63         | tdpu    | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2,3)</sup>                           |           | —         | 20                     | μs    | (Note 6)                                               |

## TABLE 30-61: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Parameters are characterized but not tested in manufacturing.

- **3:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (AD1CON1<15>) = 1). During this time, the ADC result is indeterminate.

## TABLE 30-62: DMA MODULE TIMING REQUIREMENTS

|              |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |            |  |

|--------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|--|

| Param<br>No. | Characteristic                 | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(1)</sup> | Max. | Units | Conditions |  |

| DM1          | DMA Byte/Word Transfer Latency | 1 Tcy <b>(2)</b>                                                                                                                                                                                                                                                                        | _                   | _    | ns    |            |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

<sup>© 2011-2013</sup> Microchip Technology Inc.