Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | - ·                                                                            |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 8x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc203t-e-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

NOTES:

| U-0                                                                                           | U-0                                                                                                                                                                                        | U-0                                                                                                               | U-0                                                                                  | U-0                                                                                | U-0    | U-0                | R/W-0   |  |  |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------|--------------------|---------|--|--|

| _                                                                                             | —                                                                                                                                                                                          |                                                                                                                   |                                                                                      | —                                                                                  | _      | _                  | ADDMAEN |  |  |

| bit 15                                                                                        |                                                                                                                                                                                            |                                                                                                                   |                                                                                      |                                                                                    |        |                    | bit 8   |  |  |

|                                                                                               |                                                                                                                                                                                            |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

| U-0                                                                                           | U-0                                                                                                                                                                                        | U-0 U-                                                                                                            |                                                                                      | U-0                                                                                | R/W-0  | R/W-0              | R/W-0   |  |  |

| _                                                                                             |                                                                                                                                                                                            | _                                                                                                                 | _                                                                                    |                                                                                    | DMABL2 | DMABL1             | DMABL0  |  |  |

| bit 7                                                                                         |                                                                                                                                                                                            |                                                                                                                   |                                                                                      |                                                                                    |        |                    | bit 0   |  |  |

|                                                                                               |                                                                                                                                                                                            |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

| Legend:                                                                                       |                                                                                                                                                                                            |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

| R = Readab                                                                                    | ole bit                                                                                                                                                                                    | W = Writable b                                                                                                    | bit                                                                                  | U = Unimplemented bit, read as '0'                                                 |        |                    |         |  |  |

| -n = Value a                                                                                  | at POR                                                                                                                                                                                     | '1' = Bit is set                                                                                                  |                                                                                      | '0' = Bit is cleared                                                               |        | x = Bit is unknown |         |  |  |

|                                                                                               |                                                                                                                                                                                            |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

| bit 15-9                                                                                      | Unimplemented: Read as 'O'                                                                                                                                                                 |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

| bit 8                                                                                         | ADDMAEN: ADC1 DMA Enable bit                                                                                                                                                               |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

|                                                                                               | 1 = Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA<br>O = Conversion results are stored in ADC1BUF0 through ADC1BUFF registers; DMA will not be used |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

| bit 7-3                                                                                       | Unimplemented: Read as '0'                                                                                                                                                                 |                                                                                                                   |                                                                                      |                                                                                    |        |                    |         |  |  |

| bit 2-0 <b>DMABL&lt;2:0&gt;:</b> Selects Number of DMA Buffer Locations per Analog Input bits |                                                                                                                                                                                            |                                                                                                                   |                                                                                      |                                                                                    |        | ut bits            |         |  |  |

|                                                                                               | 110 = Allocat<br>101 = Allocat<br>100 = Allocat<br>011 = Allocat                                                                                                                           | es 128 words of<br>es 64 words of l<br>es 32 words of l<br>es 16 words of b<br>es 8 words of b<br>es 4 words of b | buffer to each<br>buffer to each<br>buffer to each<br>uffer to each<br>uffer to each | n analog input<br>n analog input<br>n analog input<br>analog input<br>analog input | t      |                    |         |  |  |

# REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                                                            | R/W-0                                                                                     | U-0              | U-0            | U-0                  | R/W-0                              | R/W-0                | R/W-0                |  |  |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|----------------|----------------------|------------------------------------|----------------------|----------------------|--|--|

| CSS31                                                            | CSS30                                                                                     |                  | _              |                      | CSS26 <sup>(2)</sup>               | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |  |  |

| bit 15                                                           |                                                                                           |                  |                |                      |                                    |                      | bit 8                |  |  |

|                                                                  |                                                                                           |                  |                |                      |                                    |                      |                      |  |  |

| U-0                                                              | U-0                                                                                       | U-0              | U-0            | U-0                  | U-0                                | U-0                  | U-0                  |  |  |

|                                                                  | —                                                                                         | —                | _              | _                    | _                                  | —                    | _                    |  |  |

| bit 7                                                            | •                                                                                         |                  |                |                      |                                    |                      | bit C                |  |  |

|                                                                  |                                                                                           |                  |                |                      |                                    |                      |                      |  |  |

| Legend:                                                          |                                                                                           |                  |                |                      |                                    |                      |                      |  |  |

| R = Readabl                                                      | e bit                                                                                     | W = Writable     | bit            | U = Unimple          | mented bit, read                   | d as '0'             |                      |  |  |

| -n = Value at                                                    | POR                                                                                       | '1' = Bit is set |                | '0' = Bit is cleared |                                    | x = Bit is unknown   |                      |  |  |

|                                                                  |                                                                                           |                  |                |                      |                                    |                      |                      |  |  |

| bit 15                                                           | CSS31: ADC                                                                                | I Input Scan S   | election bit   |                      |                                    |                      |                      |  |  |

|                                                                  |                                                                                           |                  |                |                      | input scan (Ope                    |                      |                      |  |  |

|                                                                  | •                                                                                         | •                |                | surement for ir      | iput scan (Open                    | )                    |                      |  |  |

| bit 14                                                           |                                                                                           | I Input Scan S   |                |                      |                                    |                      |                      |  |  |

|                                                                  |                                                                                           |                  |                |                      | r input scan (CT<br>nput scan (CTM |                      |                      |  |  |

| bit 13-11                                                        | -                                                                                         | ted: Read as '   | •              |                      |                                    |                      |                      |  |  |

| bit 10                                                           | -                                                                                         |                  |                |                      |                                    |                      |                      |  |  |

|                                                                  | CSS26: ADC1 Input Scan Selection bit <sup>(2)</sup><br>1 = Selects OA3/AN6 for input scan |                  |                |                      |                                    |                      |                      |  |  |

|                                                                  | O = Skips OA3/AN6 for input scan                                                          |                  |                |                      |                                    |                      |                      |  |  |

| bit 9 <b>CSS25:</b> ADC1 Input Scan Selection bit <sup>(2)</sup> |                                                                                           |                  |                |                      |                                    |                      |                      |  |  |

|                                                                  | 1 = Selects OA2/AN0 for input scan                                                        |                  |                |                      |                                    |                      |                      |  |  |

|                                                                  | 0 = Skips OA2                                                                             | 2/AN0 for input  | scan           |                      |                                    |                      |                      |  |  |

| bit 8                                                            | CSS24: ADC1 Input Scan Selection bit <sup>(2)</sup>                                       |                  |                |                      |                                    |                      |                      |  |  |

|                                                                  | 1 = Selects O                                                                             | A1/AN3 for inp   | ut scan        |                      |                                    |                      |                      |  |  |

|                                                                  | 0 = Skips OA                                                                              | 1/AN3 for input  | scan           |                      |                                    |                      |                      |  |  |

| bit 7-0                                                          | Unimplemented: Read as '0'                                                                |                  |                |                      |                                    |                      |                      |  |  |

| Note 1: A                                                        | II AD1CSSH bits                                                                           | can be selecte   | d by user soft | ware Howeve          | r innuts selected                  | d for scan with      | out a                |  |  |

|                                                                  |                                                                                           |                  |                |                      |                                    |                      |                      |  |  |

# REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| <sup>3-0</sup> Step<br>Commar | option<3:0>        | Option Description                                                                                 |

|-------------------------------|--------------------|----------------------------------------------------------------------------------------------------|

| PTGCTRL(                      | <sup>1)</sup> 0000 | Reserved.                                                                                          |

|                               | 0001               | Reserved.                                                                                          |

|                               | 0010               | Disable Step Delay Timer (PTGSD).                                                                  |

|                               | 0011               | Reserved.                                                                                          |

|                               | 0100               | Reserved.                                                                                          |

|                               | 0101               | Reserved.                                                                                          |

|                               | 0110               | Enable Step Delay Timer (PTGSD).                                                                   |

|                               | 0111               | Reserved.                                                                                          |

|                               | 1000               | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                              |

|                               | 1001               | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                              |

|                               | 1010               | Reserved.                                                                                          |

|                               | 1011               | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = 0 to 1). |

|                               | 1100               | Copy contents of the Counter 0 register to the AD1CHS0 register.                                   |

|                               | 1101               | Copy contents of the Counter 1 register to the AD1CHS0 register.                                   |

|                               | 1110               | Copy contents of the Literal 0 register to the AD1CHS0 register.                                   |

|                               | 1111               | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                     |

| PTGADD <sup>(1)</sup>         | 0000               | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                    |

|                               | 0001               | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                    |

|                               | 0010               | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                       |

|                               | 0011               | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                       |

|                               | 0100               | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM).                   |

|                               | 0101               | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                             |

|                               | 0110               | Reserved.                                                                                          |

|                               | 0111               | Reserved.                                                                                          |

| PTGCOP                        | <b>1)</b> 1000     | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                  |

|                               | 1001               | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                  |

|                               | 1010               | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                     |

|                               | 1011               | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                     |

|                               | 1100               | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                 |

|                               | 1101               | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                           |

|                               | 1110               | Reserved.                                                                                          |

|                               | 1111               | Reserved.                                                                                          |

## TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOPinstruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                      |    |            |                                                                                                                                               |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                        | Min. | Min. Typ. Max. Units |    | Conditions |                                                                                                                                               |

|                    | liL    | Input Leakage Current <sup>(1,2)</sup>                                                                                                                                                                                                                                                |      |                      |    |            |                                                                                                                                               |

| DI50               |        | I/O Pins 5V Tolerant <sup>(3)</sup>                                                                                                                                                                                                                                                   | -1   | —                    | +1 | μA         | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in at high-impedance} \end{split}$                         |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(3)</sup>                                                                                                                                                                                                                                               | -1   | _                    | +1 | μA         | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup>                                                                                                                                                                                                                                               | -1   | _                    | +1 | μA         | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup>                                                                                                                                                                                                                                               | -1   | _                    | +1 | μA         | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                      |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup>                                                                                                                                                                                                                                               | -1   | _                    | +1 | μA         | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |

| DI55               |        | MCLR                                                                                                                                                                                                                                                                                  | -5   | —                    | +5 | μA         | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |

| DI56               |        | OSC1                                                                                                                                                                                                                                                                                  | -5   | —                    | +5 | μΑ         | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |

### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

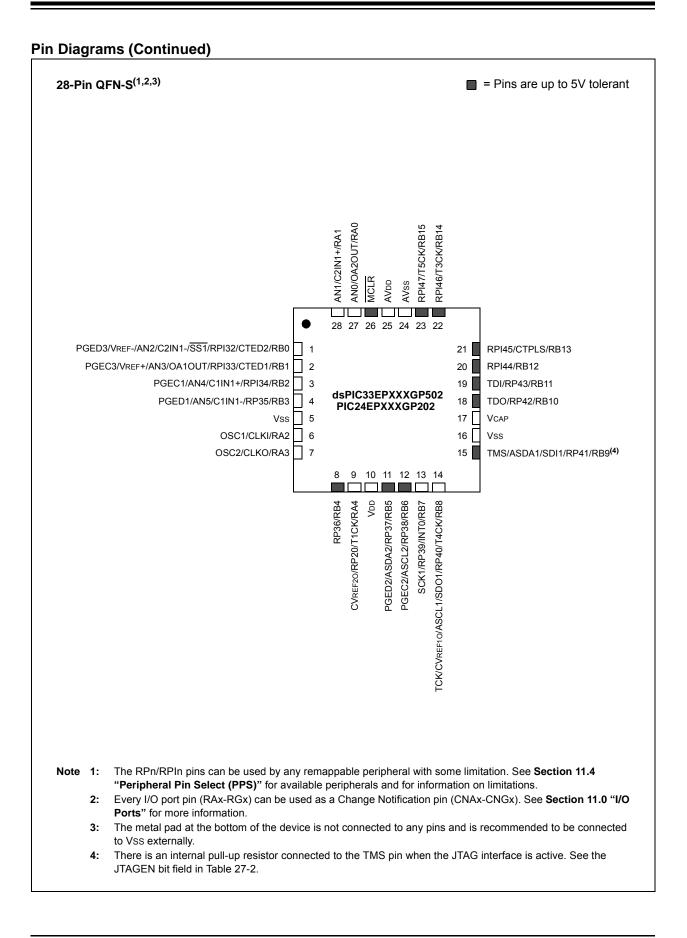

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

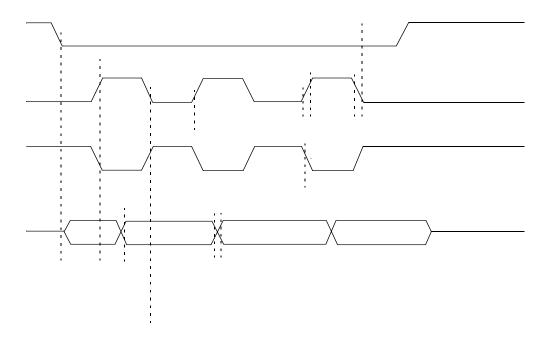

FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS