Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 8x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc203t-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

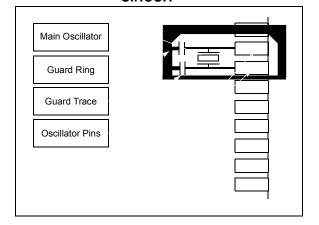

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

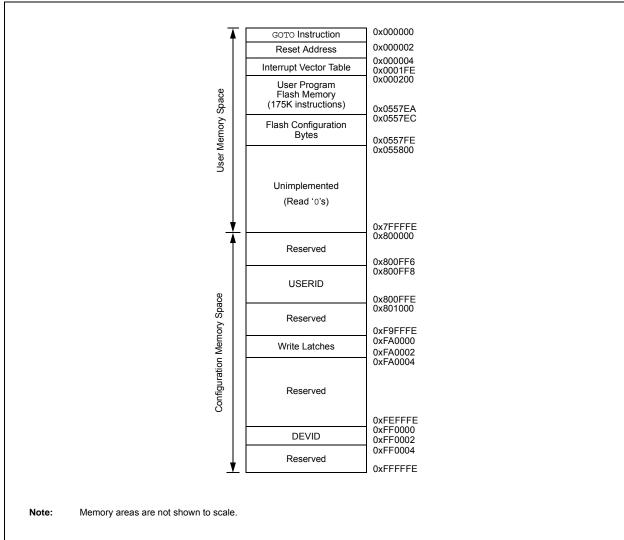

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR ds | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |        |        | INT1R<6:0> |        |       |       | _     | _     | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |        | S      | CK2INR<6:0 | )>     |       |       | _     |       |       | :     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _      | —      | —          | _      | _     | —     | —     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      | _      | -      | _          | _      | —     |       | —     |       |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit 6       | Bit 5     | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|------------|--------|-------|-------|------------|-------------|-----------|-----------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |           |        | INT1R<6:0> |        |       |       | —          | —           | —         | —         | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _         | _      | _          | _      | _     | _     | _          | INT2R<6:0>  |           |           |            |       |       | 0000  |               |

| RPINR3    | 06A6  |        |        |           |        |            | _      | _     |       |            | -           | F2CKR<6:0 | >         |            |       | 0000  |       |               |

| RPINR7    | 06AE  |        |        | IC2R<6:0> |        |            |        |       |       | _          | IC1R<6:0>   |           |           |            |       |       | 0000  |               |

| RPINR8    | 06B0  |        |        | IC4R<6:0> |        |            |        |       | _     |            |             |           | IC3R<6:0> |            |       |       | 0000  |               |

| RPINR11   | 06B6  |        | _      |           |        |            |        |       | _     | _          |             |           | (         | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |        |           |        |            |        |       | _     | FLT1R<6:0> |             |           |           |            |       | 0000  |       |               |

| RPINR14   | 06BC  |        |        |           | (      | QEB1R<6:0  | >      |       |       | _          | QEA1R<6:0>  |           |           |            |       |       | 0000  |               |

| RPINR15   | 06BE  |        |        |           | Н      | OME1R<6:0  | )>     |       |       | _          | INDX1R<6:0> |           |           |            |       | 0000  |       |               |

| RPINR18   | 06C4  |        | _      | _         | _      | _          | _      | _     | _     | _          | U1RXR<6:0>  |           |           |            | 0000  |       |       |               |

| RPINR19   | 06C6  |        | _      | _         | _      | _          | _      | _     | _     | _          | U2RXR<6:0>  |           |           |            |       | 0000  |       |               |

| RPINR22   | 06CC  | _      |        |           | S      | CK2INR<6:( | )>     |       |       | —          |             |           |           | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —         |        | —          | —      |       | —     | —          |             |           |           | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | _      | _         |        | —          | —      |       | —     | —          |             |           | (         | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |        |           | S      | YNCI1R<6:0 | )>     |       |       | —          | —           | —         | —         | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |        |           | D      | CMP1R<6:   | 0>     |       |       | —          |             |           |           |            | _     | 0000  |       |               |

| RPINR39   | 06EE  | _      |        |           | D      | FCMP3R<6:  | 0>     |       |       | _          |             |           | D         | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                  | R/W-0                          | R/W-0                 | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | R/W-0                |

|------------------------|--------------------------------|-----------------------|-----------------------------------|--------------------------------------|-----------------------|----------------------|----------------------|

| NSTDIS                 | OVAERR <sup>(1)</sup>          | OVBERR <sup>(1)</sup> | COVAERR <sup>(1)</sup>            | COVBERR <sup>(1)</sup>               | OVATE <sup>(1)</sup>  | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |

| pit 15                 |                                |                       |                                   |                                      |                       |                      | bit 8                |

|                        |                                |                       |                                   |                                      |                       |                      |                      |

| R/W-0                  | R/W-0                          | R/W-0                 | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | U-0                  |

| SFTACERR <sup>(1</sup> | ) DIV0ERR                      | DMACERR               | MATHERR                           | ADDRERR                              | STKERR                | OSCFAIL              | —                    |

| pit 7                  |                                |                       |                                   |                                      |                       |                      | bit 0                |

|                        |                                |                       |                                   |                                      |                       |                      |                      |

| _egend:                |                                |                       |                                   |                                      |                       |                      |                      |

| R = Readable           |                                | W = Writable          |                                   | U = Unimpleme                        |                       |                      |                      |

| n = Value at           | POR                            | '1' = Bit is set      |                                   | '0' = Bit is clear                   | ed                    | x = Bit is unk       | nown                 |

| bit 15                 | NSTDIS: Inte                   | errupt Nesting        | Disable hit                       |                                      |                       |                      |                      |

|                        |                                | nesting is disa       |                                   |                                      |                       |                      |                      |

|                        | •                              | nesting is ena        |                                   |                                      |                       |                      |                      |

| pit 14                 | -                              | -                     | Overflow Trap F                   | lag bit <sup>(1)</sup>               |                       |                      |                      |

|                        |                                |                       | erflow of Accur                   |                                      |                       |                      |                      |

|                        | =                              |                       | overflow of A                     |                                      |                       |                      |                      |

| pit 13                 |                                |                       | Overflow Trap F                   | •                                    |                       |                      |                      |

|                        |                                |                       | erflow of Accur                   |                                      |                       |                      |                      |

| pit 12                 | -                              | -                     |                                   | Overflow Trap Fla                    | ag bit <sup>(1)</sup> |                      |                      |

|                        | 1 = Trap was                   | caused by ca          | tastrophic over                   | flow of Accumula                     | ator A                |                      |                      |

| pit 11                 |                                |                       |                                   | Overflow Trap Fla                    |                       |                      |                      |

|                        |                                |                       | •                                 | flow of Accumula                     | •                     |                      |                      |

|                        | =                              |                       | -                                 | overflow of Accur                    | nulator B             |                      |                      |

| pit 10                 |                                |                       | erflow Trap Ena                   | able bit <sup>(1)</sup>              |                       |                      |                      |

|                        | 1 = Trap ove<br>0 = Trap is d  | rflow of Accum        | ulator A                          |                                      |                       |                      |                      |

| pit 9                  | OVBTE: Acc                     | umulator B Ov         | erflow Trap En                    | able bit <sup>(1)</sup>              |                       |                      |                      |

|                        | 1 = Trap ove<br>0 = Trap is d  | rflow of Accum        | ulator B                          |                                      |                       |                      |                      |

| oit 8                  | COVTE: Cat                     | astrophic Over        | flow Trap Enat                    | ole bit <sup>(1)</sup>               |                       |                      |                      |

|                        | 1 = Trap on o<br>0 = Trap is d |                       | erflow of Accu                    | mulator A or B is                    | enabled               |                      |                      |

| oit 7                  | SFTACERR:                      | Shift Accumul         | ator Error Statu                  | us bit <sup>(1)</sup>                |                       |                      |                      |

|                        |                                | •                     | •                                 | alid accumulator<br>invalid accumula |                       |                      |                      |

| oit 6                  | DIV0ERR: D                     | ivide-by-Zero I       | Error Status bit                  |                                      |                       |                      |                      |

|                        |                                |                       | used by a divide<br>caused by a d |                                      |                       |                      |                      |

|                        | DMACERR:                       |                       |                                   | -                                    |                       |                      |                      |

| oit 5                  |                                |                       |                                   |                                      |                       |                      |                      |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

### 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|--------|

| F15M                                           | ISK<1:0>                                                                                                             | F14MS                                                                                                                 | K<1:0>                                                                                                                                               | F13MS                                                                                                                     | SK<1:0>                                                                 | F12MS                        | K<1:0> |

| bit 15                                         |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8  |

|                                                |                                                                                                                      | 54446                                                                                                                 | 5444                                                                                                                                                 |                                                                                                                           |                                                                         | 5444.0                       |        |

| R/W-0                                          | R/W-0                                                                                                                | R/W-0                                                                                                                 | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0  |

| F11M                                           | 11MSK<1:0> F10MSK<1:0> F9MSK<1:0> F8MSF                                                                              |                                                                                                                       |                                                                                                                                                      | <<1:0>                                                                                                                    |                                                                         |                              |        |

| bit 7                                          |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C  |

|                                                |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| Legend:                                        |                                                                                                                      |                                                                                                                       |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |        |

| R = Readable bit                               |                                                                                                                      | W = Writable                                                                                                          | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                        | l as '0'                     |        |

| -n = Value at                                  | POR                                                                                                                  | '1' = Bit is set                                                                                                      |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                    | x = Bit is unkr              | nown   |

| bit 15 14                                      | ELEMOK A                                                                                                             | n. Maak Saura                                                                                                         | o for Filtor 15                                                                                                                                      | hita                                                                                                                      |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                 | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                |                                                                         |                              |        |

|                                                | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                          | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                              | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12                                      | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                           | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                         |                              |        |

| bit 15-14<br>bit 13-12<br>bit 11-10<br>bit 9-8 | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source                              | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                | ies as bits<15:                                                         | 14>)                         |        |

| bit 13-12<br>bit 11-10                         | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0                | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Source<br><b>0&gt;:</b> Mask Source | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                      | 14>)<br>14>)                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F12MSK<1:0<br>F11MSK<1:0  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:′                   | 14>)<br>14>)<br>14>)         |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6   | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F11MSK<1:0<br>F11MSK<1:0 | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Source<br>0>: Mask Source<br>0>: Mask Source  | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:<br>ies as bits<15: | 14>)<br>14>)<br>14>)<br>14>) |        |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | <b>`</b>              |                                  |                                |                          |                  |                 |                 |

|---------------|-----------------------|----------------------------------|--------------------------------|--------------------------|------------------|-----------------|-----------------|

| R/W-0         | R-0                   | R-0                              | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |

| TXENn         | TXABTn                | TXLARBn                          | TXERRn                         | TXREQn                   | RTRENn           | TXnPRI1         | TXnPRI0         |

| bit 15        |                       |                                  |                                |                          |                  |                 | bit 8           |

| R/W-0         | R-0                   | R-0                              | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |

| TXENm         | TXABTm <sup>(1)</sup> | TXLARBm <sup>(1)</sup>           | TXERRm <sup>(1)</sup>          | TXREQm                   | RTRENm           | TXmPRI1         | TXmPRI0         |

| bit 7         |                       | 1                                | 1                              |                          |                  |                 | bit (           |

| Legend:       |                       |                                  |                                |                          |                  |                 |                 |

| R = Readable  | e bit                 | W = Writable                     | bit                            | U = Unimpler             | mented bit, read | d as '0'        |                 |

| -n = Value at | POR                   | '1' = Bit is set                 |                                | '0' = Bit is cle         | ared             | x = Bit is unkr | nown            |

| bit 15-8      | See Dofinition        | n for bits<7:0>,                 | Controls Ruffs                 | ar n                     |                  |                 |                 |

| bit 7         |                       | RX Buffer Sele                   |                                |                          |                  |                 |                 |

|               |                       | RA Buller Sele                   |                                |                          |                  |                 |                 |

|               |                       | RBn is a receive                 |                                |                          |                  |                 |                 |

| bit 6         | TXABTm: M             | essage Aborted                   | 1 bit <sup>(1)</sup>           |                          |                  |                 |                 |

|               | 1 = Message           | •                                |                                |                          |                  |                 |                 |

|               | •                     | completed trar                   | nsmission succ                 | essfully                 |                  |                 |                 |

| bit 5         | TXLARBm: N            | Message Lost A                   | Arbitration bit <sup>(1)</sup> | )                        |                  |                 |                 |

|               |                       | lost arbitration                 |                                |                          |                  |                 |                 |

|               | 0 = Message           | did not lose ar                  | bitration while                | being sent               |                  |                 |                 |

| bit 4         | TXERRm: Er            | ror Detected D                   | uring Transmis                 | ssion bit <sup>(1)</sup> |                  |                 |                 |

|               |                       | or occurred wh                   | •                              | •                        |                  |                 |                 |

|               |                       | or did not occu                  |                                | ssage was bei            | ing sent         |                 |                 |

| bit 3         |                       | essage Send F                    | -                              |                          |                  |                 |                 |

|               | sent                  |                                  | -                              |                          | -                | n the message   | is successfully |

|               |                       | the bit to '0' wh                | •                              | 0                        | abort            |                 |                 |

| bit 2         |                       | uto-Remote Tra                   |                                |                          |                  |                 |                 |

|               |                       | emote transmit<br>emote transmit |                                |                          |                  |                 |                 |

| bit 1-0       | TXmPRI<1:0            | >: Message Tra                   | ansmission Pri                 | ority bits               |                  |                 |                 |

|               |                       | message prior                    |                                |                          |                  |                 |                 |

|               |                       | ermediate mes                    |                                |                          |                  |                 |                 |

|               |                       | ermediate mess<br>message priori |                                |                          |                  |                 |                 |

|               | 00 – Lowesi           | messaye priori                   | ıy                             |                          |                  |                 |                 |

| Note 1: Th    | nis bit is cleared    | when TXREQ i                     | s set.                         |                          |                  |                 |                 |

|               |                       |                                  |                                |                          |                  |                 |                 |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

#### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x            | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | Ву    | /te 3             |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x            | R/W-x           | R/W-x |

|                 |       |                  | Ву    | /te 2             |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|--|

|                                   |       |                  | В     | yte 5                              |       |                 |       |  |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |  |

|                                   |       |                  |       | yte 4                              |       |                 |       |  |  |

| bit 7                             |       |                  |       | -                                  |       |                 | bit 0 |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unki | nown  |  |  |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

#### REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|              | R/W-0         | U-0                 | U-0                         | U-0             | R/W-0                                | R/W-0                | R/W-0                |

|--------------|---------------|---------------------|-----------------------------|-----------------|--------------------------------------|----------------------|----------------------|

| CSS31        | CSS30         | —                   | —                           | _               | CSS26 <sup>(2)</sup>                 | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |

| bit 15       | - 1           |                     |                             |                 |                                      |                      | bit 8                |

|              |               |                     |                             |                 |                                      |                      |                      |

| U-0          | U-0           | U-0                 | U-0                         | U-0             | U-0                                  | U-0                  | U-0                  |

| _            |               | _                   | _                           | —               |                                      | _                    |                      |

| bit 7        |               |                     |                             |                 |                                      |                      | bit (                |

|              |               |                     |                             |                 |                                      |                      |                      |

| Legend:      |               |                     |                             |                 |                                      |                      |                      |

| R = Readab   | le bit        | W = Writable        | bit                         | U = Unimple     | emented bit, read                    | d as '0'             |                      |

| -n = Value a | t POR         | '1' = Bit is set    |                             | '0' = Bit is cl | eared                                | x = Bit is unk       | nown                 |

|              |               |                     |                             |                 |                                      |                      |                      |

| bit 15       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | input scan (Ope                      |                      |                      |

|              | •             | •                   |                             | surement for ir | nput scan (Open                      | )                    |                      |

| bit 14       |               | 1 Input Scan S      |                             |                 |                                      |                      |                      |

|              |               |                     |                             |                 | or input scan (CT<br>input scan (CTN |                      |                      |

| bit 13-11    | Unimplemen    | ted: Read as '      | 0'                          |                 |                                      |                      |                      |

| bit 10       | CSS26: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | )<br>A3/AN6 for inp | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 3/AN6 for input     | scan                        |                 |                                      |                      |                      |

| bit 9        | CSS25: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              | 1 = Selects C | 0A2/AN0 for inp     | ut scan                     |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 2/AN0 for input     | scan                        |                 |                                      |                      |                      |

| bit 8        | CSS24: ADC    | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |

|              |               | 0A1/AN3 for inp     |                             |                 |                                      |                      |                      |

|              | 0 = Skips OA  | 1/AN3 for input     | scan                        |                 |                                      |                      |                      |

|              |               |                     |                             |                 |                                      |                      |                      |

## REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| bit 3-0 | Step<br>Command       | OPTION<3:0> | Option Description                                                                                      |

|---------|-----------------------|-------------|---------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)            | 0000        | Reserved.                                                                                               |

|         |                       | 0001        | Reserved.                                                                                               |

|         |                       | 0010        | Disable Step Delay Timer (PTGSD).                                                                       |

|         |                       | 0011        | Reserved.                                                                                               |

|         |                       | 0100        | Reserved.                                                                                               |

|         |                       | 0101        | Reserved.                                                                                               |

|         |                       | 0110        | Enable Step Delay Timer (PTGSD).                                                                        |

|         |                       | 0111        | Reserved.                                                                                               |

|         |                       | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                   |

|         |                       | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                   |

|         |                       | 1010        | Reserved.                                                                                               |

|         |                       | 1011        | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = $0$ to $1$ ). |

|         |                       | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                        |

|         |                       | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                        |

|         |                       | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                        |

| -       |                       | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                          |

|         | PTGADD <sup>(1)</sup> | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                         |

|         |                       | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                         |

|         |                       | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                            |

|         |                       | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                            |

|         |                       | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM).                        |

|         |                       | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                  |

|         |                       | 0110        | Reserved.                                                                                               |

|         |                       | 0111        | Reserved.                                                                                               |

|         | PTGCOPY <b>(1)</b>    | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                       |

|         |                       | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                       |

|         |                       | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                          |

|         |                       | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                          |

|         |                       | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                      |

|         |                       | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                |

|         |                       | 1110        | Reserved.                                                                                               |

|         |                       | 1111        | Reserved.                                                                                               |

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

#### 25.1 Op Amp Application Considerations

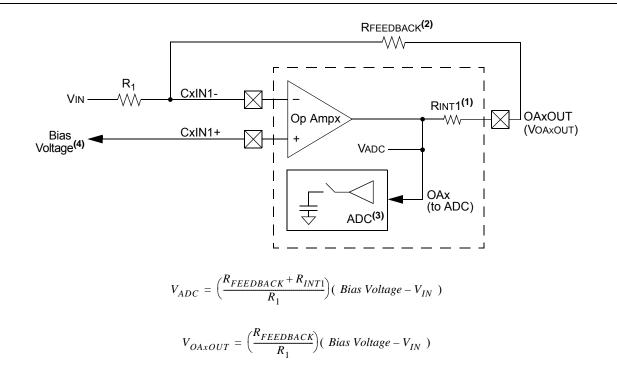

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

#### 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

#### FIGURE 25-6: OP AMP CONFIGURATION A

Note 1: See Table 30-53 for the Typical value.

- 2: See Table 30-53 for the Minimum value for the feedback resistor.

- 3: See Table 30-60 and Table 30-61 for the minimum sample time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

#### 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## TABLE 30-39:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                                |

|--------------------|-----------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                                                                                                                                                                                       | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCK2 Input Frequency                    | —                                                                                                                                                                                                          | —                   | 15   | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCK2 Input Fall Time                            | —                                                                                                                                                                                                          | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP73               | TscR                  | SCK2 Input Rise Time                            | —                                                                                                                                                                                                          | _                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | —                                                                                                                                                                                                          | —                   | _    | ns    | See Parameter DO32 (Note 4)    |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                                                                                                                                                                                          | _                   | _    | ns    | See Parameter DO31 (Note 4)    |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                                                                                                                                                                                          | 6                   | 20   | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                                                                                                                                                                                         | —                   | _    | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                                                                                                                                                                                         | —                   | _    | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                                                                                                                                                                                         | —                   | _    | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                                                                                                                                                                                        | -                   | _    | ns    |                                |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                                                                                                                                                                                         | —                   | 50   | ns    | (Note 4)                       |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                                                                                                                                                                               | —                   |      | ns    | (Note 4)                       |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

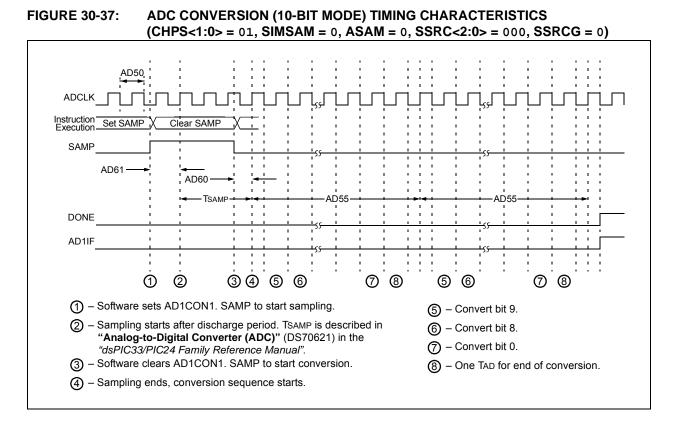

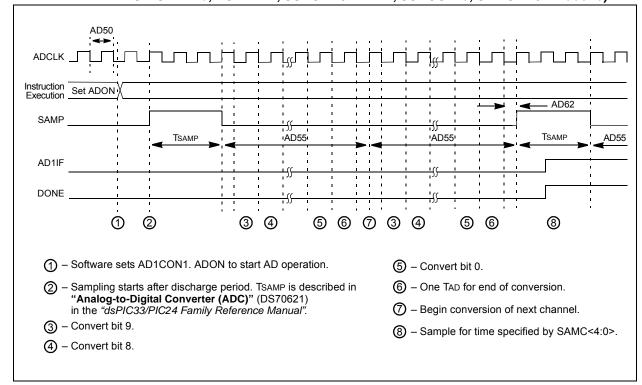

#### FIGURE 30-38: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

DS70000657H-page 464

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACT               | ERISTICS |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |            |      |                                               |  |  |

|--------------------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----------------------------------------------|--|--|

| Parameter<br>No.         | Typical  | Мах  | Units                                                                                                                                  | Conditions |      |                                               |  |  |

| Power-Down Current (IPD) |          |      |                                                                                                                                        |            |      |                                               |  |  |

| HDC60e                   | 1400     | 2500 | μA                                                                                                                                     | +150°C     | 3.3V | Base Power-Down Current (Notes 1, 3)          |  |  |

| HDC61c                   | 15       | —    | μΑ                                                                                                                                     | +150°C     | 3.3V | Watchdog Timer Current: ∆IwDT<br>(Notes 2, 4) |  |  |

#### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

#### TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAG        | CTERISTICS |     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |            |      |         |  |

|------------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------|--|

| Parameter<br>No. | Typical    | Мах | Units                                                                                                                               | Conditions |      |         |  |

| HDC44e           | 12         | 30  | mA                                                                                                                                  | +150°C     | 3.3V | 40 MIPS |  |

#### TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARAC        | CTERISTICS |     | (unless othe | erating Condi<br>rwise stated)<br>nperature -40 |      |         |

|------------------|------------|-----|--------------|-------------------------------------------------|------|---------|

| Parameter<br>No. | Typical    | Max | Units        | Conditions                                      |      |         |

| HDC20            | 9          | 15  | mA           | +150°C                                          | 3.3V | 10 MIPS |

| HDC22            | 16         | 25  | mA           | +150°C                                          | 3.3V | 20 MIPS |

| HDC23            | 30         | 50  | mA           | +150°C                                          | 3.3V | 40 MIPS |

#### TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARA              | CTERISTICS |     | (unless oth   | erwise s | <b>Conditions</b><br>tated)<br>re -40°C ≤ |      |         |

|-----------------------|------------|-----|---------------|----------|-------------------------------------------|------|---------|

| Parameter<br>No.      | Typical    | Мах | Doze<br>Ratio | Units    | Conditions                                |      |         |

| HDC72a                | 24         | 35  | 1:2           | mA       |                                           |      |         |

| HDC72f <sup>(1)</sup> | 14         | —   | 1:64          | mA       | +150°C                                    | 3.3V | 40 MIPS |

| HDC72g <sup>(1)</sup> | 12         |     | 1:128         | mA       |                                           |      |         |

Note 1: Parameters with Doze ratios of 1:64 and 1:128 are characterized, but are not tested in manufacturing.

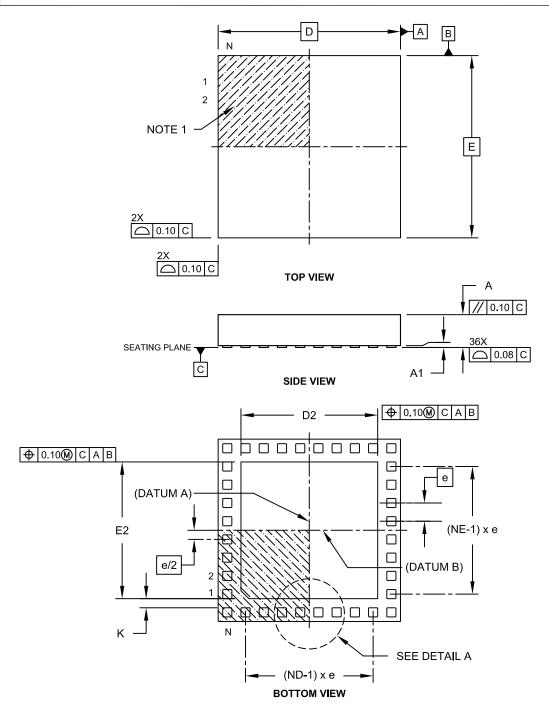

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

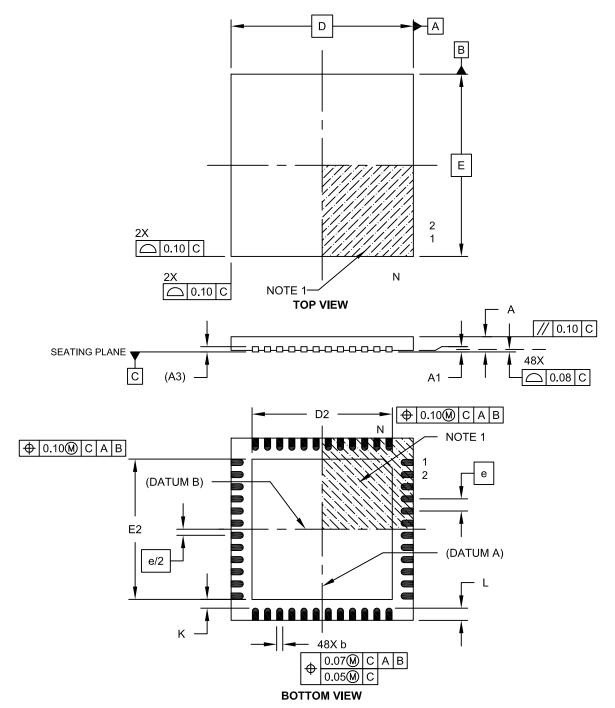

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

#### Ρ

| Packaging                                  |     |

|--------------------------------------------|-----|

| Details                                    |     |

| Marking                                    |     |

| Peripheral Module Disable (PMD)            |     |

| Peripheral Pin Select (PPS)                |     |

| Available Peripherals                      | 175 |

| Available Pins                             | 175 |

| Control                                    |     |

| Control Registers                          |     |

| Input Mapping                              |     |

| Output Selection for Remappable Pins       |     |