Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 60 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 9x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VFTLA Exposed Pad                                                          |

| Supplier Device Package    | 44-VTLA (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc204-e-tl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

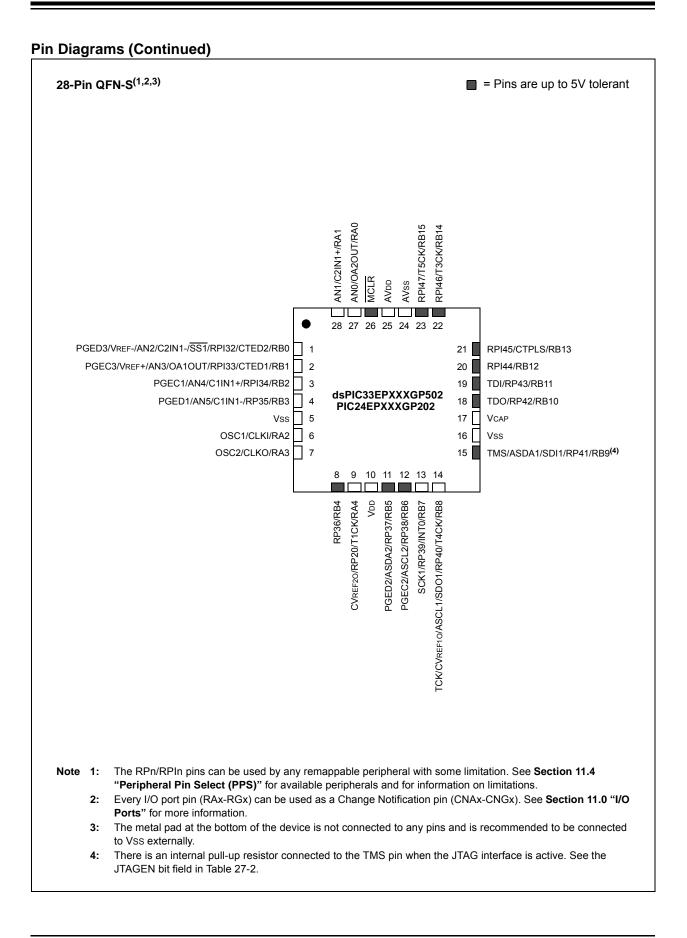

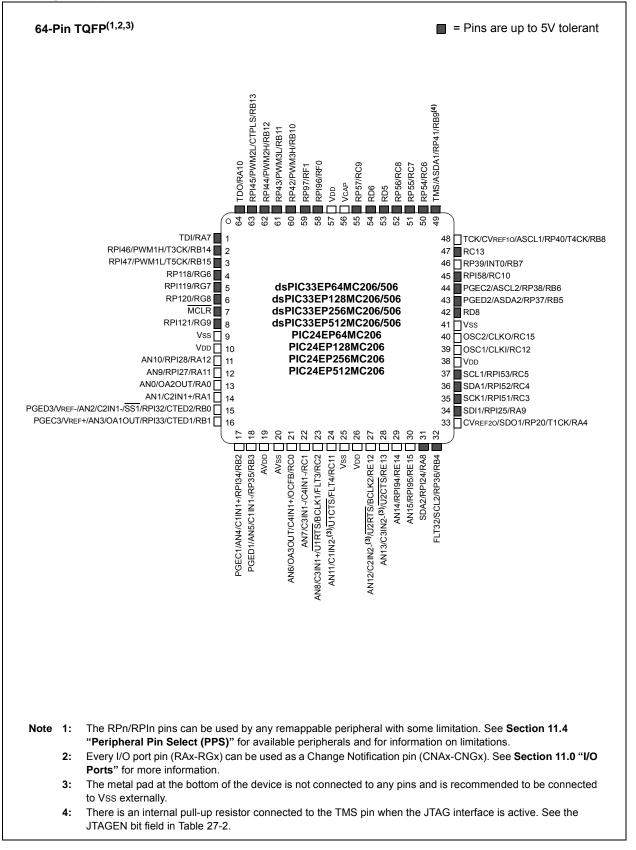

### Pin Diagrams (Continued)

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

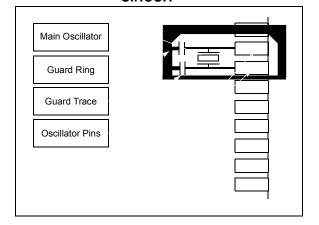

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| R/W-0               | U-0                                                                                                                 | R/W-0                                                                        | R/W-0                   | R/W-0                       | R-0                | R-0                | R-0                |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------|-----------------------------|--------------------|--------------------|--------------------|--|--|--|

| VAR                 | —                                                                                                                   | US1 <sup>(1)</sup>                                                           | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup> | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |  |  |  |

| bit 15              |                                                                                                                     |                                                                              |                         |                             |                    |                    | bit                |  |  |  |

| R/W-0               | R/W-0                                                                                                               | R/W-1                                                                        | R/W-0                   | R/C-0                       | R-0                | R/W-0              | R/W-0              |  |  |  |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>                                                                                                 | SATDW <sup>(1)</sup>                                                         | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                | RND <sup>(1)</sup> | IF(1)              |  |  |  |

| bit 7               | I                                                                                                                   |                                                                              |                         |                             | I                  | 1                  | bit                |  |  |  |

| Legend:             |                                                                                                                     | C = Clearable                                                                | e bit                   |                             |                    |                    |                    |  |  |  |

| R = Readabl         | e bit                                                                                                               | W = Writable                                                                 | bit                     | U = Unimpler                | mented bit, read   | d as '0'           |                    |  |  |  |

| -n = Value at       | POR                                                                                                                 | '1' = Bit is set                                                             | t                       | '0' = Bit is cle            | ared               | x = Bit is unkr    | nown               |  |  |  |

| bit 15              | 1 = Variable                                                                                                        | le Exception Pro<br>exception proce                                          | essing latency          | is enabled                  |                    |                    |                    |  |  |  |

| bit 14              |                                                                                                                     | nted: Read as '                                                              |                         |                             |                    |                    |                    |  |  |  |

| bit 13-12           | -                                                                                                                   | SP Multiply Uns                                                              |                         | Control bits <sup>(1)</sup> |                    |                    |                    |  |  |  |

|                     | 01 = DSP er<br>00 = DSP er                                                                                          | ngine multiplies<br>ngine multiplies<br>ngine multiplies                     | are unsigned are signed |                             |                    |                    |                    |  |  |  |

| bit 11              | •                                                                                                                   | O Loop Terminatives executing Dot<br>t                                       |                         |                             | iteration          |                    |                    |  |  |  |

| bit 10-8            | DL<2:0>: DO Loop Nesting Level Status bits <sup>(1)</sup><br>111 = 7 DO loops are active                            |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     | •                                                                                                                   |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     | •                                                                                                                   |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     | 001 = 1 DO k<br>000 = 0 DO k                                                                                        | oop is active<br>oops are active                                             |                         |                             |                    |                    |                    |  |  |  |

| bit 7               | SATA: ACCA                                                                                                          | A Saturation En                                                              | able bit <sup>(1)</sup> |                             |                    |                    |                    |  |  |  |

|                     | <ul> <li>1 = Accumulator A saturation is enabled</li> <li>0 = Accumulator A saturation is disabled</li> </ul>       |                                                                              |                         |                             |                    |                    |                    |  |  |  |

| bit 6               | SATB: ACCB Saturation Enable bit <sup>(1)</sup>                                                                     |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     |                                                                                                                     | ator B saturatio<br>ator B saturatio                                         |                         |                             |                    |                    |                    |  |  |  |

| bit 5               | SATDW: Dat                                                                                                          | SATDW: Data Space Write from DSP Engine Saturation Enable bit <sup>(1)</sup> |                         |                             |                    |                    |                    |  |  |  |

|                     | <ul> <li>1 = Data Space write saturation is enabled</li> <li>0 = Data Space write saturation is disabled</li> </ul> |                                                                              |                         |                             |                    |                    |                    |  |  |  |

| bit 4               | ACCSAT: Accumulator Saturation Mode Select bit <sup>(1)</sup>                                                       |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     |                                                                                                                     | uration (super s<br>uration (normal                                          | ,                       |                             |                    |                    |                    |  |  |  |

| bit 3               | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(3)</sup>                                                      |                                                                              |                         |                             |                    |                    |                    |  |  |  |

|                     |                                                                                                                     | errupt Priority Le<br>errupt Priority Le                                     |                         |                             |                    |                    |                    |  |  |  |

|                     | nis bit is availabl                                                                                                 |                                                                              | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP         | 50X devices on     | ly.                |  |  |  |

| 2: Th               | nis bit is always                                                                                                   | reau as 0.                                                                   |                         |                             |                    |                    |                    |  |  |  |

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

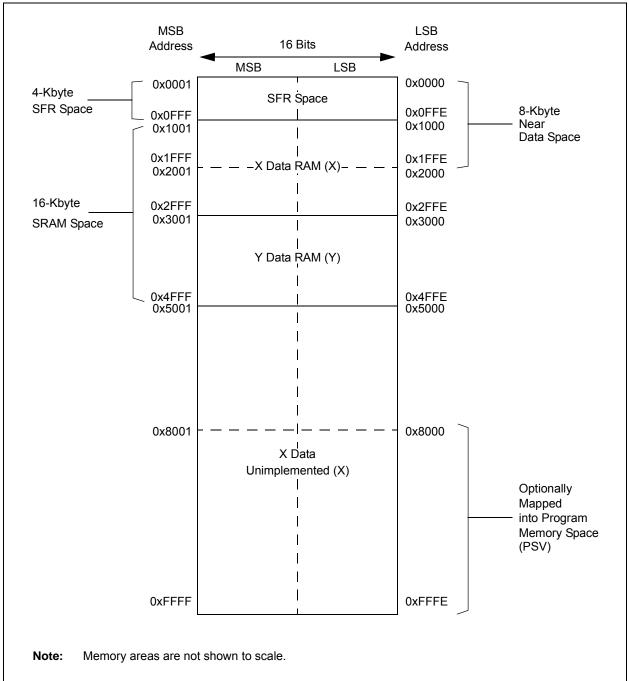

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

| R/W-1        | R/W-0                                             | R/W-0                                                                | U-0          | U-0              | U-0              | U-0             | U-0    |  |  |  |

|--------------|---------------------------------------------------|----------------------------------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|--|

| GIE          | DISI                                              | SWTRAP                                                               |              |                  |                  | _               |        |  |  |  |

| bit 15       |                                                   |                                                                      |              |                  |                  |                 | bit 8  |  |  |  |

|              |                                                   |                                                                      |              |                  |                  |                 |        |  |  |  |

| U-0          | U-0                                               | U-0                                                                  | U-0          | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|              | —                                                 |                                                                      |              |                  | INT2EP           | INT1EP          | INT0EP |  |  |  |

| bit 7        |                                                   |                                                                      |              |                  |                  |                 | bit C  |  |  |  |

| Legend:      |                                                   |                                                                      |              |                  |                  |                 |        |  |  |  |

| R = Readab   | le bit                                            | W = Writable                                                         | bit          | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |

| -n = Value a |                                                   | '1' = Bit is set                                                     |              | '0' = Bit is cle |                  | x = Bit is unki | nown   |  |  |  |

|              |                                                   |                                                                      |              |                  |                  |                 |        |  |  |  |

| bit 15       | GIE: Global                                       | Interrupt Enable                                                     | e bit        |                  |                  |                 |        |  |  |  |

|              | 1 = Interrupts and associated IE bits are enabled |                                                                      |              |                  |                  |                 |        |  |  |  |

|              |                                                   | 0 = Interrupts are disabled, but traps are still enabled             |              |                  |                  |                 |        |  |  |  |

| bit 14       | DISI: DISI                                        | DISI: DISI Instruction Status bit                                    |              |                  |                  |                 |        |  |  |  |

|              |                                                   | 1 = DISI instruction is active<br>0 = DISI instruction is not active |              |                  |                  |                 |        |  |  |  |

| bit 13       | SWTRAP: S                                         | SWTRAP: Software Trap Status bit                                     |              |                  |                  |                 |        |  |  |  |

|              |                                                   | = Software trap is enabled<br>= Software trap is disabled            |              |                  |                  |                 |        |  |  |  |

| bit 12-3     | Unimpleme                                         | nted: Read as '                                                      | 0'           |                  |                  |                 |        |  |  |  |

| bit 2        | INT2EP: Ext                                       | ternal Interrupt 2                                                   | 2 Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |

|              |                                                   | on negative edg                                                      |              |                  |                  |                 |        |  |  |  |

| bit 1        | INT1EP: Ext                                       | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit         |              |                  |                  |                 |        |  |  |  |

|              |                                                   | on negative edg                                                      |              |                  |                  |                 |        |  |  |  |

| bit 0        | INTOEP: Ext                                       | ternal Interrupt C                                                   | Edge Detec   | t Polarity Selec | t bit            |                 |        |  |  |  |

|              |                                                   | on negative edg                                                      |              |                  |                  |                 |        |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

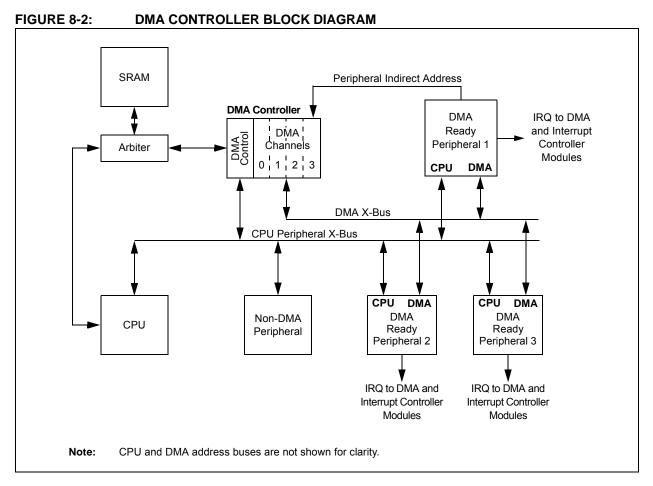

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

### 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

### REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

### bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | STA   | <15:8>                                  |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | STA   | A<7:0>                                  |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

#### 11.7 **Peripheral Pin Select Registers**

### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|------------|-------|-------|-------|-------|-------|

| —      |       | INT1R<6:0> |       |       |       |       |       |

| bit 15 |       |            |       |       |       |       | bit 8 |

|        |       |            |       |       |       |       |       |

| U-0    | U-0   | U-0        | U-0   | U-0   | U-0   | U-0   | U-0   |

| —      | —     | —          | —     | —     | _     | _     | —     |

| bit 7  |       | •          |       | •     |       |       | bit 0 |

|        |       |            |       |       |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| —       | —     | —     | —     | —          | —     | —     | —     |

| bit 15  | •     |       |       |            | •     |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7   | •     |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Leaend: |       |       |       |            |       |       |       |

### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

### 15.2 Output Compare Control Registers

### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0        | U-0                                                | R/W-0                                       | R/W-0             | R/W-0             | R/W-0                  | U-0             | R/W-0         |

|------------|----------------------------------------------------|---------------------------------------------|-------------------|-------------------|------------------------|-----------------|---------------|

| 0-0        | 0-0                                                | OCSIDL                                      | OCTSEL2           | OCTSEL1           | OCTSEL0                | 0-0             | ENFLTB        |

| <br>bit 15 |                                                    | OCSIDE                                      | OCTSEL2           | OCISELI           | OCTSELU                | —               | bit 8         |

| DIL 15     |                                                    |                                             |                   |                   |                        |                 | DIL O         |

| R/W-0      | U-0                                                | R/W-0, HSC                                  | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0           | R/W-0         |

| ENFLT      |                                                    | OCFLTB                                      | OCFLTA            | TRIGMODE          | OCM2                   | OCM1            | OCM0          |

| bit 7      |                                                    | 001218                                      | OOFEIN            | ITTOMODE          | 001112                 | 0.0111          | bit 0         |

|            |                                                    |                                             |                   |                   |                        |                 | 2.1.0         |

| Legend:    |                                                    | HSC = Hardw                                 | are Settable/Cl   | earable bit       |                        |                 |               |

| R = Read   | able bit                                           | W = Writable I                              | bit               | U = Unimplem      | nented bit, read       | as '0'          |               |

| -n = Value | e at POR                                           | '1' = Bit is set                            |                   | '0' = Bit is clea | ared                   | x = Bit is unkn | own           |

|            |                                                    |                                             |                   |                   |                        |                 |               |

| bit 15-14  | Unimplemen                                         | ted: Read as 'o                             | )'                |                   |                        |                 |               |

| bit 13     | OCSIDL: Out                                        | tput Compare x                              | Stop in Idle Mo   | de Control bit    |                        |                 |               |

|            |                                                    | compare x Halts                             |                   |                   |                        |                 |               |

|            | •                                                  | compare x conti                             | •                 |                   | ode                    |                 |               |

| bit 12-10  |                                                    | D>: Output Com                              | pare x Clock Se   | elect bits        |                        |                 |               |

|            | 111 = Periph<br>110 = Reserv                       | eral clock (FP)                             |                   |                   |                        |                 |               |

|            | 101 = PTGO                                         |                                             |                   |                   |                        |                 |               |

|            |                                                    | is the clock so                             | urce of the OC    | k (only the sync  | hronous clock          | is supported)   |               |

|            |                                                    | is the clock so                             |                   |                   |                        |                 |               |

|            |                                                    | is the clock so                             |                   |                   |                        |                 |               |

|            |                                                    | ( is the clock so<br>( is the clock so      |                   |                   |                        |                 |               |

| bit 9      |                                                    | ted: Read as '0                             |                   | -                 |                        |                 |               |

| bit 8      | -                                                  | ult B Input Enab                            |                   |                   |                        |                 |               |

|            |                                                    | ompare Fault B                              |                   | is enabled        |                        |                 |               |

|            | -                                                  | compare Fault B                             |                   | is disabled       |                        |                 |               |

| bit 7      |                                                    | ult A Input Enab                            |                   |                   |                        |                 |               |

|            |                                                    | Compare Fault A<br>Compare Fault A          |                   |                   |                        |                 |               |

| bit 6      | •                                                  | •                                           | ,                 | is disabled       |                        |                 |               |

| bit 5      | -                                                  | i <b>ted:</b> Read as '0<br>VM Fault B Cond |                   |                   |                        |                 |               |

| DIL 5      |                                                    | ult B condition of                          |                   |                   |                        |                 |               |

|            |                                                    | I Fault B condition                         |                   |                   |                        |                 |               |

| bit 4      | OCFLTA: PW                                         | /M Fault A Cond                             | dition Status bit |                   |                        |                 |               |

|            | 1 = PWM Fault A condition on OCFA pin has occurred |                                             |                   |                   |                        |                 |               |

|            | 0 = No PWM                                         | I Fault A condition                         | on on OCFA pi     | n has occurred    |                        |                 |               |

| Note 1:    | OCxR and OCxF                                      | RS are double-b                             | ouffered in PWN   | /I mode only.     |                        |                 |               |

| 2:         | Each Output Cor                                    |                                             |                   | -                 | urce. See <b>Secti</b> | on 24.0 "Perip  | heral Trigger |

|            | Generator (PTG                                     |                                             |                   |                   |                        |                 |               |

|            | PTGO4 = 0C1                                        |                                             |                   |                   |                        |                 |               |

|            | PTGO5 = OC2<br>PTGO6 = OC3                         |                                             |                   |                   |                        |                 |               |

|            | PTGO6 = OC3 $PTGO7 = OC4$                          |                                             |                   |                   |                        |                 |               |

|            |                                                    |                                             |                   |                   |                        |                 |               |

### REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but on | ly '0' can be written to clear t | he bit             |

|-------------------|--------------------------|----------------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit            | , read as '0'      |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared             | x = Bit is unknown |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only ( | )' can be written to clear the l | oit                |

|-------------------|------------------------------|----------------------------------|--------------------|

| R = Readable bit  | W = Writable bit             | U = Unimplemented bit, re-       | ad as '0'          |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared             | x = Bit is unknown |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| REGISTER      | 25-3: CM40                 | CON: COMPA                                                       | RATOR 4 CO        | ONTROL RE        | GISTER             |                                        |                     |  |  |  |

|---------------|----------------------------|------------------------------------------------------------------|-------------------|------------------|--------------------|----------------------------------------|---------------------|--|--|--|

| R/W-0         | R/W-0                      | R/W-0                                                            | U-0               | U-0              | U-0                | R/W-0                                  | R/W-0               |  |  |  |

| CON           | COE                        | CPOL                                                             | —                 | —                | _                  | CEVT                                   | COUT                |  |  |  |

| bit 15        |                            |                                                                  |                   |                  |                    |                                        | bit 8               |  |  |  |

| R/W-0         | DAALO                      | U-0                                                              |                   | U-0              | U-0                |                                        | R/W-0               |  |  |  |

|               | R/W-0                      | 0-0                                                              | R/W-0             | 0-0              | 0-0                | R/W-0                                  |                     |  |  |  |

| EVPOL1        | EVPOL0                     | —                                                                | CREF              | —                | _                  | CCH1 <sup>(1)</sup>                    | CCH0 <sup>(1)</sup> |  |  |  |

| bit 7         |                            |                                                                  |                   |                  |                    |                                        | bit (               |  |  |  |

| Legend:       |                            |                                                                  |                   |                  |                    |                                        |                     |  |  |  |

| R = Readable  | e bit                      | W = Writable                                                     | bit               | U = Unimple      | mented bit, rea    | d as '0'                               |                     |  |  |  |

| -n = Value at |                            | '1' = Bit is se                                                  |                   | '0' = Bit is cle |                    | x = Bit is unkr                        | iown                |  |  |  |

|               |                            |                                                                  | •                 |                  |                    |                                        |                     |  |  |  |

| bit 15        | CON: Comp                  | arator Enable b                                                  | oit               |                  |                    |                                        |                     |  |  |  |

|               |                            | ator is enabled                                                  |                   |                  |                    |                                        |                     |  |  |  |

|               |                            | ator is disabled                                                 |                   |                  |                    |                                        |                     |  |  |  |

| bit 14        | COE: Comp                  | arator Output E                                                  | nable bit         |                  |                    |                                        |                     |  |  |  |

|               |                            | ator output is pr<br>ator output is in                           |                   | xOUT pin         |                    |                                        |                     |  |  |  |

| bit 13        | CPOL: Com                  | parator Output                                                   | Polarity Select   | bit              |                    |                                        |                     |  |  |  |

|               |                            | ator output is in                                                |                   |                  |                    |                                        |                     |  |  |  |

|               | 0 = Compara                | ator output is no                                                | ot inverted       |                  |                    |                                        |                     |  |  |  |

| bit 12-10     | Unimpleme                  | nted: Read as                                                    | '0'               |                  |                    |                                        |                     |  |  |  |

| bit 9         | CEVT: Comparator Event bit |                                                                  |                   |                  |                    |                                        |                     |  |  |  |

|               | interrup                   | ts until the bit is                                              | cleared           | POL<1:0> set     | tings occurred;    | disables future                        | triggers and        |  |  |  |

|               | •                          | ator event did i                                                 |                   |                  |                    |                                        |                     |  |  |  |

| bit 8         |                            | parator Output                                                   |                   |                  |                    |                                        |                     |  |  |  |

|               |                            | <u>When CPOL = 0 (non-inverted polarity):</u><br>1 = VIN+ > VIN- |                   |                  |                    |                                        |                     |  |  |  |

|               |                            | 1 = VIN + > VIN - 0 = VIN + < VIN - 0                            |                   |                  |                    |                                        |                     |  |  |  |

|               | When CPOL                  | When CPOL = 1 (inverted polarity):                               |                   |                  |                    |                                        |                     |  |  |  |

|               | 1 = VIN+ < V               |                                                                  |                   |                  |                    |                                        |                     |  |  |  |

|               | 0 = VIN + > V              | 'IN-                                                             |                   |                  |                    |                                        |                     |  |  |  |

| bit 7-6       |                            | >: Trigger/Ever                                                  |                   | -                |                    |                                        |                     |  |  |  |

|               | 10 = Trigger               |                                                                  | generated only    |                  |                    | or output (while one polarity selected |                     |  |  |  |

|               |                            | L = 1 (inverted)<br>-high transition                             |                   | ator output.     |                    |                                        |                     |  |  |  |

|               |                            | L = 0 (non-inve<br>-low transition                               |                   | ator output.     |                    |                                        |                     |  |  |  |

|               |                            | /event/interrupt<br>(while CEVT =                                |                   | v on low-to-higl | n transition of th | e polarity selecte                     | ed comparato        |  |  |  |

|               |                            | L = 1 (inverted                                                  |                   | ator output.     |                    |                                        |                     |  |  |  |

|               |                            | L = 0 (non-inve<br>-high transition                              |                   | ator output.     |                    |                                        |                     |  |  |  |

|               | 00 = Trigger               | /event/interrupt                                                 | generation is     | disabled         |                    |                                        |                     |  |  |  |

| Note 1: In    | puts that are se           | lected and not a                                                 | available will be | e tied to Vss. S | See the "Pin Dia   | agrams" sectior                        | n for available     |  |  |  |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

### REGISTER 27-1: DEVID: DEVICE ID REGISTER

|        |   | Only bit U = Unimplemented bit |         |                      |   |   |        |

|--------|---|--------------------------------|---------|----------------------|---|---|--------|

|        |   |                                |         |                      |   |   |        |

| bit 7  |   |                                |         |                      |   |   | bit 0  |

|        |   |                                | DEVID   | <7:0> <sup>(1)</sup> |   |   |        |

| R      | R | R                              | R       | R                    | R | R | R      |

| bit 15 |   |                                |         |                      |   |   | bit 8  |

|        |   |                                | DEVID<  | 15:8> <sup>(1)</sup> |   |   |        |

| R      | R | R                              | R       | R                    | R | R | R      |

| bit 23 |   |                                |         |                      |   |   | bit 16 |

|        |   |                                | DEVID<2 | 23:16>(1)            |   |   |        |

| R      | R | R                              | R       | R                    | R | R | R      |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| R           | R             | R                     | R      | R                      | R | R | R       |  |

|-------------|---------------|-----------------------|--------|------------------------|---|---|---------|--|

|             |               |                       | DEVREV | <23:16> <sup>(1)</sup> |   |   |         |  |

| bit 23      |               |                       |        |                        |   |   | bit 16  |  |

|             |               |                       |        |                        |   |   |         |  |

| R           | R             | R                     | R      | R                      | R | R | R       |  |

|             |               |                       | DEVREV | <15:8>(1)              |   |   |         |  |

| bit 15      |               |                       |        |                        |   |   | bit 8   |  |

|             |               |                       |        |                        |   |   | <b></b> |  |

| R           | R             | R                     | R      | R                      | R | R | R       |  |

|             |               |                       | DEVRE\ | /<7:0> <sup>(1)</sup>  |   |   |         |  |

| bit 7       |               |                       |        |                        |   |   | bit 0   |  |

|             |               |                       |        |                        |   |   |         |  |

| Legend: R = | Read-only bit | U = Unimplemented bit |        |                        |   |   |         |  |

### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

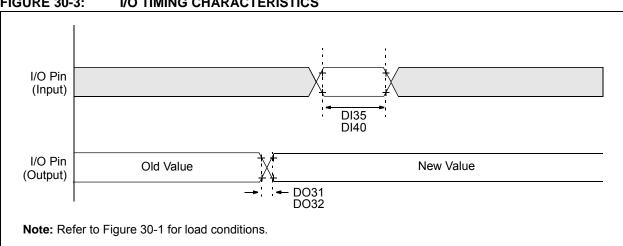

#### **FIGURE 30-3: I/O TIMING CHARACTERISTICS**

### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |            |

|--------------------|--------|-----------------------------------|-------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                  | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DO31               | TioR   | Port Output Rise Time             |                                                       | 5                   | 10   | ns    |            |

| DO32               | TIOF   | Port Output Fall Time             | _                                                     | 5                   | 10   | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                    | —                   | _    | ns    |            |

| DI40               | Trbp   | CNx High or Low Time (input)      | 2                                                     | _                   | _    | Тсү   |            |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

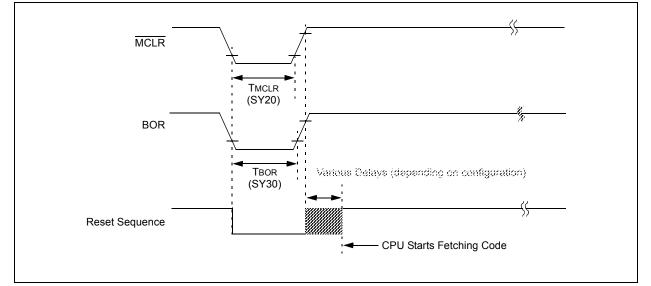

#### FIGURE 30-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

NOTES:

NOTES: