Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

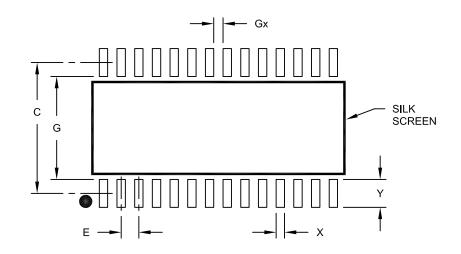

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc204t-e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

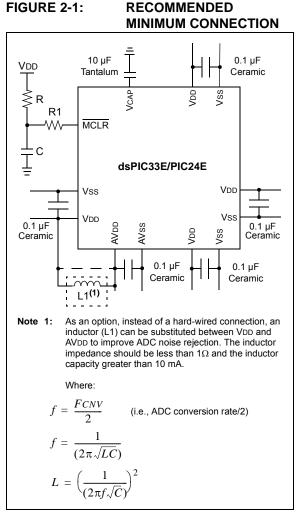

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

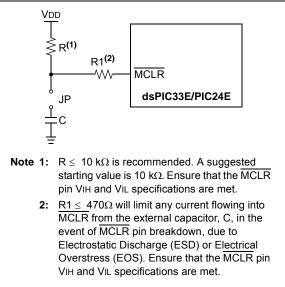

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

| TABLE 4   | 4-9:  | INPUT  |        | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|--------|--------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _      | —      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _      | _      |         | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |        |        |         |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |        |        |         |        |           |        |       | Input Capt   | ture 1 Time  | r        |       |       |       |          |          |       | 0000          |

| IC2CON1   | 0148  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A  |        | _      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC2BUF    | 014C  |        |        |         |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |        |        |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |        | _      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |        |        |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |        |        |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |        | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _      | _      |         | -      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |        |        |         |        |           |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC4TMR    | 015E  |        |        |         |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | —      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | -      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | _      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | _      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | _      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | _      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | _      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0-0     | 0-0   | 0-0   | 0-0   | 0-0        | 0-0   | 0-0   | 0-0   |

|         | —     |       | _     | _          | —     | —     |       |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —       |       |       |       | U2RXR<6:0> | >     |       |       |

| bit 7   |       |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Legend: |       |       |       |            |       |       |       |

|         |       |       |       |            |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

#### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                        |                                                                               |                                          |                                   |

|--------------|------------------------|-------------------------------------------------------------------------------|------------------------------------------|-----------------------------------|

| R = Readal   | ole bit                | W = Writable bit                                                              | U = Unimplemented bit                    | , read as '0'                     |

| -n = Value a | at POR                 | '1' = Bit is set                                                              | '0' = Bit is cleared                     | x = Bit is unknown                |

| bit 15       | TON: Tin               | nery On bit <sup>(1)</sup>                                                    |                                          |                                   |

|              |                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                          |                                   |

| bit 14       | •                      | mented: Read as '0'                                                           |                                          |                                   |

| bit 13       | -                      | imery Stop in Idle Mode bit                                                   | 2)                                       |                                   |

|              |                        | ontinues module operation winues module operation in Id                       | when device enters Idle mode<br>lle mode |                                   |

| bit 12-7     | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

| bit 6        | TGATE:                 | Timery Gated Time Accumu                                                      | lation Enable bit <sup>(1)</sup>         |                                   |

|              | When TC<br>This bit is | <u>CS = 1:</u><br>s ignored.                                                  |                                          |                                   |

|              |                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                          |                                   |

| bit 5-4      | TCKPS<                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>        |                                   |

|              | 11 <b>= 1:2</b> 5      |                                                                               |                                          |                                   |

|              | 10 = 1:64<br>01 = 1:8  | 1                                                                             |                                          |                                   |

|              | 01 = 1.8               |                                                                               |                                          |                                   |

| bit 3-2      | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

| bit 1        | -                      | nery Clock Source Select bit                                                  | (1,3)                                    |                                   |

|              |                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)                     |                                   |

| bit 0        | Unimple                | mented: Read as '0'                                                           |                                          |                                   |

|              |                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e           | ffect on Timery operation; all ti |

|              |                        |                                                                               |                                          |                                   |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

| R/W-0         | R/W-0       | R/W-0                                  | U-0          | U-0              | U-0             | U-0               | U-0    |

|---------------|-------------|----------------------------------------|--------------|------------------|-----------------|-------------------|--------|

| FRMEN         | SPIFSD      | FRMPOL                                 | —            | —                | _               | —                 | _      |

| bit 15        |             |                                        |              |                  |                 |                   | bit 8  |

|               |             |                                        |              |                  |                 |                   |        |

| U-0           | U-0         | U-0                                    | U-0          | U-0              | U-0             | R/W-0             | R/W-0  |

| _             | <u> </u>    | —                                      | _            |                  | _               | FRMDLY            | SPIBEN |

| bit 7         |             |                                        |              |                  |                 |                   | bit 0  |

|               |             |                                        |              |                  |                 |                   |        |

| Legend:       |             |                                        |              |                  |                 |                   |        |

| R = Readable  | e bit       | W = Writable b                         | pit          | U = Unimpler     | nented bit, rea | ad as '0'         |        |

| -n = Value at | POR         | '1' = Bit is set                       |              | '0' = Bit is cle | ared            | x = Bit is unkr   | nown   |

|               |             |                                        |              |                  |                 |                   |        |

| bit 15        | FRMEN: Fra  | med SPIx Suppo                         | ort bit      |                  |                 |                   |        |

|               |             | SPIx support is e<br>SPIx support is d |              | x pin is used as | Frame Sync      | oulse input/outpu | it)    |

| bit 14        | SPIFSD: Fra | me Sync Pulse [                        | Direction Co | ontrol bit       |                 |                   |        |

|               |             | ync pulse input (<br>ync pulse output  |              |                  |                 |                   |        |

| bit 13        | FRMPOL: Fr  | ame Sync Pulse                         | Polarity bit | t                |                 |                   |        |

|               |             | ync pulse is activ                     | •            |                  |                 |                   |        |

|               |             | ync pulse is activ                     |              |                  |                 |                   |        |

| bit 12-2      | -           | nted: Read as '0                       |              |                  |                 |                   |        |

| bit 1         |             | ame Sync Pulse                         | -            |                  |                 |                   |        |

|               |             | ync pulse coincio<br>ync pulse preceo  |              |                  |                 |                   |        |

| bit 0         | SPIBEN: En  | hanced Buffer Er                       | nable bit    |                  |                 |                   |        |

|               |             | d buffer is enable                     |              |                  |                 |                   |        |

|               | 0 = Enhance | d buffer is disabl                     | ed (Standa   | rd mode)         |                 |                   |        |

|               |             |                                        |              |                  |                 |                   |        |

#### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7  | RXOVF6                                                             | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |  |  |

|---------|--------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| bit 7   |                                                                    |        |        |        |        |        | bit 0  |  |  |

|         |                                                                    |        |        |        |        |        |        |  |  |

| Legend: | nd: C = Writable bit, but only '0' can be written to clear the bit |        |        |        |        |        |        |  |  |

| Legend:           | C = Writable bit, but only '0' | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|--------------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit               | U = Unimplemented bit, read                                    | l as '0'           |  |  |  |  |

| -n = Value at POR | '1' = Bit is set               | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown                 |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

| REGISTER 25-5: | CMxMSKCON: COMPARATOR x MASK GATING |

|----------------|-------------------------------------|

|                | CONTROL REGISTER                    |

| R/W-0           |                                                                                                                    |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-------------------|-------------------|--------------|--|--|--|--|

|                 | U-0                                                                                                                | R/W-0                                                                                                 | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0             | R/W-0        |  |  |  |  |

| HLMS            | —                                                                                                                  | OCEN                                                                                                  | OCNEN                                                                    | OBEN             | OBNEN             | OAEN              | OANEN        |  |  |  |  |

| bit 15          |                                                                                                                    |                                                                                                       |                                                                          |                  |                   |                   | bit          |  |  |  |  |

| R/W-0           | R/W-0                                                                                                              | R/W-0                                                                                                 | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0             | R/W-0        |  |  |  |  |

| NAGS            | PAGS                                                                                                               | ACEN                                                                                                  | ACNEN                                                                    | ABEN             | ABNEN             | AAEN              | AANEN        |  |  |  |  |

| bit 7           |                                                                                                                    |                                                                                                       |                                                                          | 1                |                   |                   | bit          |  |  |  |  |

| Legend:         |                                                                                                                    |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

| R = Readable I  | bit                                                                                                                | W = Writable                                                                                          | bit                                                                      | U = Unimple      | mented bit, read  | l as '0'          |              |  |  |  |  |

| -n = Value at P | OR                                                                                                                 | '1' = Bit is set                                                                                      |                                                                          | '0' = Bit is cle |                   | x = Bit is unki   | nown         |  |  |  |  |

|                 |                                                                                                                    |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

| bit 15          | HLMS: High                                                                                                         | or Low-Level N                                                                                        | lasking Select                                                           | bits             |                   |                   |              |  |  |  |  |

|                 | •                                                                                                                  |                                                                                                       | •                                                                        |                  | erted ('0') compa | rator signal from | n propagatin |  |  |  |  |

|                 |                                                                                                                    |                                                                                                       |                                                                          |                  | erted ('1') compa |                   |              |  |  |  |  |

| bit 14          | Unimplemen                                                                                                         | ted: Read as '                                                                                        | 0'                                                                       |                  |                   |                   |              |  |  |  |  |

| bit 13          | OCEN: OR G                                                                                                         | ate C Input Er                                                                                        | able bit                                                                 |                  |                   |                   |              |  |  |  |  |

|                 | 1 = MCI is co                                                                                                      | nnected to OR                                                                                         | gate                                                                     |                  |                   |                   |              |  |  |  |  |

|                 | 0 = MCI is no                                                                                                      | t connected to                                                                                        | OR gate                                                                  |                  |                   |                   |              |  |  |  |  |

| bit 12          |                                                                                                                    | Gate C Input I                                                                                        |                                                                          | e bit            |                   |                   |              |  |  |  |  |

|                 | <ul> <li>1 = Inverted MCI is connected to OR gate</li> <li>0 = Inverted MCI is not connected to OR gate</li> </ul> |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    |                                                                                                       |                                                                          | jate             |                   |                   |              |  |  |  |  |

| bit 11          | OBEN: OR Gate B Input Enable bit<br>1 = MBI is connected to OR gate                                                |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    | nnected to OR<br>t connected to                                                                       | •                                                                        |                  |                   |                   |              |  |  |  |  |

| bit 10          |                                                                                                                    |                                                                                                       | •                                                                        | a hit            |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    | DBNEN: OR Gate B Input Inverted Enable bit L = Inverted MBI is connected to OR gate                   |                                                                          |                  |                   |                   |              |  |  |  |  |

|                 | 0 = Inverted MBI is not connected to OR gate                                                                       |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

| bit 9           |                                                                                                                    | ate A Input En                                                                                        | -                                                                        |                  |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    | 1 = MAI is connected to OR gate                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

|                 | 0 = MAI is no                                                                                                      | t connected to                                                                                        | OR gate                                                                  |                  |                   |                   |              |  |  |  |  |

| bit 8           | OANEN: OR                                                                                                          | Gate A Input I                                                                                        | nverted Enable                                                           | e bit            |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    | nverted MAI is connected to OR gate                                                                   |                                                                          |                  |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    | MAI is not conr                                                                                       | -                                                                        |                  |                   |                   |              |  |  |  |  |

| bit 7           | NAGS: AND Gate Output Inverted Enable bit<br>1 = Inverted ANDI is connected to OR gate                             |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

|                 |                                                                                                                    | <ul> <li>Inverted ANDI is not connected to OR gate</li> </ul> <b>PAGS:</b> AND Gate Output Enable bit |                                                                          |                  |                   |                   |              |  |  |  |  |

| bit 6           |                                                                                                                    |                                                                                                       |                                                                          |                  |                   |                   |              |  |  |  |  |

| bit 6           |                                                                                                                    | onnected to O                                                                                         |                                                                          |                  |                   |                   |              |  |  |  |  |

| bit 6           | 1 = ANDI is c                                                                                                      | •                                                                                                     | R gate                                                                   |                  |                   |                   |              |  |  |  |  |

| bit 6<br>bit 5  | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND                                                                        | onnected to O<br>ot connected t<br>Gate C Input E                                                     | R gate<br>o OR gate<br>inable bit                                        |                  |                   |                   |              |  |  |  |  |

|                 | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND<br>1 = MCI is co                                                       | onnected to O<br>ot connected t<br>Gate C Input E<br>nnected to AN                                    | R gate<br>o OR gate<br>inable bit<br>D gate                              |                  |                   |                   |              |  |  |  |  |

| bit 5           | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND<br>1 = MCI is co<br>0 = MCI is no                                      | onnected to O<br>lot connected t<br>Gate C Input E<br>nnected to AN<br>it connected to                | R gate<br>o OR gate<br>inable bit<br>D gate<br>AND gate                  |                  |                   |                   |              |  |  |  |  |

|                 | 1 = ANDI is c<br>0 = ANDI is n<br>ACEN: AND<br>1 = MCI is co<br>0 = MCI is no<br>ACNEN: AND                        | onnected to O<br>ot connected t<br>Gate C Input E<br>nnected to AN                                    | R gate<br>o OR gate<br>inable bit<br>D gate<br>AND gate<br>Inverted Enab |                  |                   |                   |              |  |  |  |  |

| File<br>Name | Address          | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-8 | Bit 7                   | Bit 6                  | Bit 5                    | Bit 4                   | Bit 3                   | Bit 2    | Bit 1        | Bit 0   |

|--------------|------------------|--------------------------------------|-----------|-------------------------|------------------------|--------------------------|-------------------------|-------------------------|----------|--------------|---------|

| Reserved     | 0057EC           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFEC           | 64                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0157EC           | 128                                  | _         | _                       | _                      | _                        | _                       | _                       | _        | —            | _       |

|              | 02AFEC           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0557EC           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| Reserved     | 0057EE           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFEE           | 64                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0157EE           | 128                                  | _         | _                       | _                      | _                        | _                       | _                       | _        | _            | _       |

|              | 02AFEE           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0557EE           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| FICD         | 0057F0           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFF0           | 64                                   | -         |                         |                        |                          |                         |                         |          |              |         |

|              | 0157F0           | 128                                  |           | Reserved <sup>(3)</sup> | _                      | JTAGEN                   | Reserved <sup>(2)</sup> | Reserved <sup>(3)</sup> | _        | ICS<         | :1.0>   |

|              | 02AFF0           | 256                                  |           |                         |                        | 01110211                 |                         |                         |          |              |         |

|              | 0557F0           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| FPOR         | 0057F2           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 003712<br>00AFF2 | 64                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0157F2           | 128                                  |           | WDTV                    | VIN<1:0>               | ALTI2C2                  | ALTI2C1                 | Reserved <sup>(3)</sup> | _        |              |         |

|              | 013712<br>02AFF2 | 256                                  |           | VUDIV                   |                        | ALTIZOZ ALTIZOT RESErved | ALTIZOT TROSCIVOU       | Received                |          |              | _       |

|              | 02AFF2<br>0557F2 | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| FWDT         | 0057F2           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              |                  |                                      |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFF4           | 64                                   |           |                         |                        |                          | WOTODE                  |                         | WDTDOO   | WDTPOST<3:0> |         |

|              | 0157F4           | 128                                  | —         | FWDTEN                  | WINDIS                 | PLLKEN                   | WDTPRE                  |                         | WDTP05   |              |         |

|              | 02AFF4           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

| 5000         | 0557F4           | 512                                  |           |                         |                        |                          |                         |                         | r        |              |         |

| FOSC         | 0057F6           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFF6           | 64                                   | -         |                         |                        |                          |                         |                         |          |              |         |

|              | 0157F6           | 128                                  | —         | FCKS                    | SM<1:0>                | IOL1WAY                  | -                       | -                       | OSCIOFNC | POSCN        | ID<1:0> |

|              | 02AFF6           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0557F6           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| FOSCSEL      | 0057F8           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFF8           | 64                                   |           |                         | (4)                    |                          |                         |                         |          |              |         |

|              | 0157F8           | 128                                  | —         | IESO                    | PWMLOCK <sup>(1)</sup> | —                        | -                       | -                       | F        | NOSC<2:0>    |         |

|              | 02AFF8           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0557F8           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| FGS          | 0057FA           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFFA           | 64                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0157FA           | 128                                  | —         | —                       | —                      | —                        | —                       | —                       | —        | GCP          | GWRP    |

|              | 02AFFA           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0557FA           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| Reserved     | 0057FC           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFFC           | 64                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0157FC           | 128                                  | —         | -                       | —                      | —                        | —                       | —                       | —        | —            | —       |

|              | 02AFFC           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0557FC           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

| Reserved     | 057FFE           | 32                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 00AFFE           | 64                                   |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0157FE           | 128                                  | _         | -                       | _                      | _                        | —                       | -                       | —        | —            | —       |

|              | 02AFFE           | 256                                  |           |                         |                        |                          |                         |                         |          |              |         |

|              | 0557FE           | 512                                  |           |                         |                        |                          |                         |                         |          |              |         |

#### TABLE 27-1: CONFIGURATION BYTE REGISTER MAP

Legend: — = unimplemented, read as '1'.

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

**2:** This bit is reserved and must be programmed as '0'.

3: These bits are reserved and must be programmed as '1'.

#### **30.1 DC Characteristics**

|                |                             |                       | Maximum MIPS                                                          |

|----------------|-----------------------------|-----------------------|-----------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)     | Temp Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |

|                | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +85°C        | 70                                                                    |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +125°C       | 60                                                                    |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min.        | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | PINT + PI/O |             | W    |      |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (           | ΓJ — TA)/θJ | IA   | W    |

#### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                   | Symbol | Тур. | Max. | Unit | Notes |

|--------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin QFN           | θJA    | 28.0 |      | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP 10x10 mm | θJA    | 48.3 | _    | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN 6x6 mm   | θJA    | 41   | —    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN           | θJA    | 29.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP 10x10 mm | θJA    | 49.8 | _    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin VTLA 6x6 mm   | θJA    | 25.2 | _    | °C/W | 1     |

| Package Thermal Resistance, 36-Pin VTLA 5x5 mm   | θJA    | 28.5 |      | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S         | θJA    | 30.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP          | θJA    | 71.0 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC          | θJA    | 69.7 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP         | θJA    | 60.0 | —    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.