Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc204t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

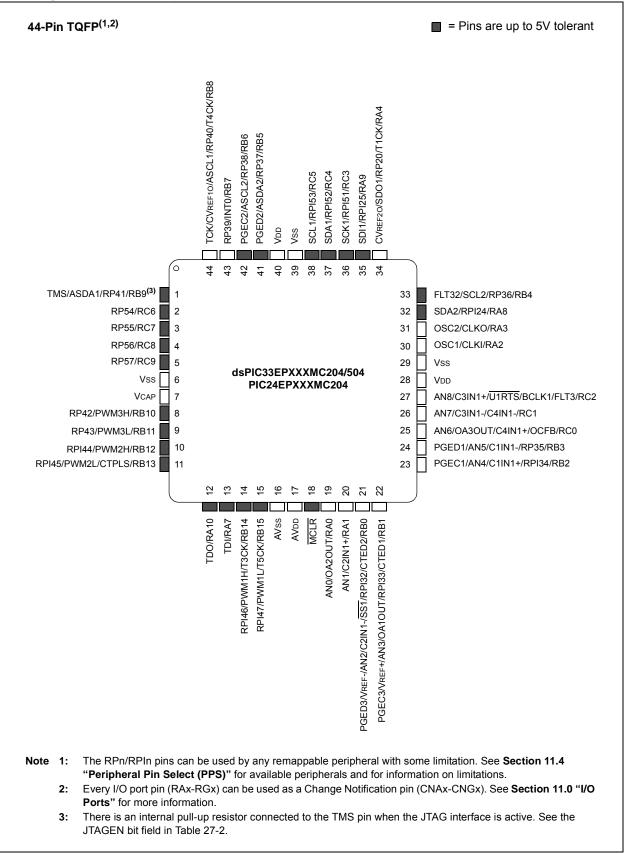

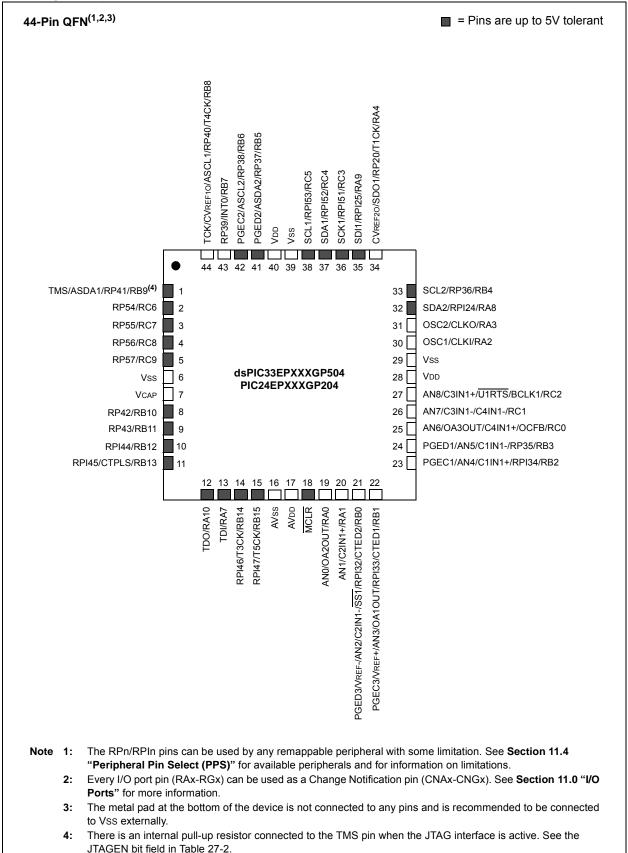

#### Pin Diagrams (Continued)

#### **Pin Diagrams (Continued)**

| IABLE 4   | -10.  | 001    |                                     | JMPARE   |        |           | OUIFU  |       | ARE 4       | REGIS       |              | <u>٢</u> |                 |          |           |          |       |               |

|-----------|-------|--------|-------------------------------------|----------|--------|-----------|--------|-------|-------------|-------------|--------------|----------|-----------------|----------|-----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                              | Bit 13   | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5    | Bit 4           | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

| OC1CON1   | 0900  | —      | -                                   | OCSIDL   | C      | CTSEL<2:0 | )>     | —     | ENFLTB      | ENFLTA      | —            | OCFLTB   | OCFLTA          | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   | IS SYNCSEL<4:0> |          |           | 000C     |       |               |

| OC1RS     | 0904  |        |                                     |          |        |           |        | Outp  | out Compare | e 1 Seconda | ary Register |          |                 |          |           |          |       | xxxx          |

| OC1R      | 0906  |        |                                     |          |        |           |        |       | Output Co   | mpare 1 Re  | gister       |          |                 |          |           |          |       | xxxx          |

| OC1TMR    | 0908  |        |                                     |          |        |           |        |       | Timer V     | alue 1 Regi | ster         |          |                 |          |           |          |       | xxxx          |

| OC2CON1   | 090A  | _      | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA          | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2   | 090C  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   | IS SYNCSEL<4:0> |          |           | 000C     |       |               |

| OC2RS     | 090E  |        | Output Compare 2 Secondary Register |          |        |           |        | xxxx  |             |             |              |          |                 |          |           |          |       |               |

| OC2R      | 0910  |        | Output Compare 2 Register           |          |        |           |        | xxxx  |             |             |              |          |                 |          |           |          |       |               |

| OC2TMR    | 0912  |        |                                     |          |        |           |        |       | Timer V     | alue 2 Regi | ster         |          |                 |          |           |          |       | xxxx          |

| OC3CON1   | 0914  | _      | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA          | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |                 | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS     | 0918  |        |                                     |          |        |           |        | Outp  | out Compare | e 3 Seconda | ary Register |          |                 |          |           |          |       | xxxx          |

| OC3R      | 091A  |        |                                     |          |        |           |        |       | Output Co   | mpare 3 Re  | gister       |          |                 |          |           |          |       | xxxx          |

| OC3TMR    | 091C  |        |                                     |          |        |           |        |       | Timer V     | alue 3 Regi | ster         |          |                 |          |           |          |       | xxxx          |

| OC4CON1   | 091E  | _      | —                                   | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB   | OCFLTA          | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS   |                 | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC4RS     | 0922  |        |                                     |          |        |           |        | Outp  | out Compare | e 4 Seconda | ary Register |          |                 |          |           |          |       | xxxx          |

| OC4R      | 0924  |        |                                     |          |        |           |        |       | Output Co   | mpare 4 Re  | gister       |          |                 |          |           |          |       | xxxx          |

| OC4TMR    | 0926  |        |                                     |          |        |           |        |       | Timer V     | alue 4 Regi | ster         |          |                 |          |           |          |       | xxxx          |

### TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

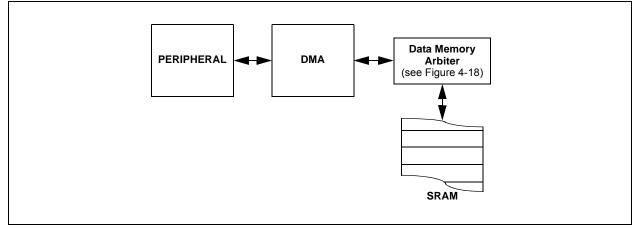

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: DMA CONTROLLER MODULE

| U-0             | U-0                                       | U-0              | U-0             | U-0                  | U-0              | U-0                | R/W-0   |  |

|-----------------|-------------------------------------------|------------------|-----------------|----------------------|------------------|--------------------|---------|--|

| —               | —                                         | —                |                 | —                    | —                | —                  | PLLDIV8 |  |

| bit 15          |                                           |                  |                 |                      |                  |                    | bit 8   |  |

|                 |                                           |                  |                 |                      |                  |                    |         |  |

| R/W-0           | R/W-0                                     | R/W-1            | R/W-1           | R/W-0                | R/W-0            | R/W-0              | R/W-0   |  |

| PLLDIV7         | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3              | PLLDIV2          | PLLDIV1            | PLLDIV0 |  |

| bit 7           |                                           |                  |                 |                      |                  |                    | bit 0   |  |

|                 |                                           |                  |                 |                      |                  |                    |         |  |

| Legend:         |                                           |                  |                 |                      |                  |                    |         |  |

| R = Readable    | bit                                       | W = Writable     | bit             | U = Unimpler         | mented bit, read | as '0'             |         |  |

| -n = Value at P | OR                                        | '1' = Bit is set |                 | '0' = Bit is cleared |                  | x = Bit is unknown |         |  |

|                 |                                           |                  |                 |                      |                  |                    |         |  |

| bit 15-9        | Unimplemen                                | ted: Read as '   | 0'              |                      |                  |                    |         |  |

| bit 8-0         | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted        | as 'M', PLL mul  | tiplier)           |         |  |

|                 | 111111111 =                               | = 513            |                 |                      |                  |                    |         |  |

|                 | •                                         |                  |                 |                      |                  |                    |         |  |

|                 | •                                         |                  |                 |                      |                  |                    |         |  |

|                 | •                                         |                  |                 |                      |                  |                    |         |  |

|                 | 000110000 =                               | = 50 (default)   |                 |                      |                  |                    |         |  |

|                 |                                           |                  |                 |                      |                  |                    |         |  |

|                 | •                                         |                  |                 |                      |                  |                    |         |  |

|                 | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                      |                  |                    |         |  |

|                 |                                           |                  |                 |                      |                  |                    |         |  |

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

#### REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|

|              |                  |                                                          |       | DTCMP3R<6:0       | )>              |                 |       |

| bit 15       |                  |                                                          |       |                   |                 |                 | bit 8 |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| 0-0          | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0       |                 | R/W-0           | R/W-U |

| bit 7        |                  |                                                          |       |                   | 17              |                 | bit 0 |

| bit i        |                  |                                                          |       |                   |                 |                 | bit 0 |

| Legend:      |                  |                                                          |       |                   |                 |                 |       |

| R = Readab   | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR           | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                  |                                                          |       |                   |                 |                 |       |

|              |                  | nput tied to CMI                                         |       |                   |                 |                 |       |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                 |       |

|        |     |       |       | DD20  |         |       |       |

|--------|-----|-------|-------|-------|---------|-------|-------|

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       | RP35  | iR<5:0> |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

#### REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP37  | ′R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP36  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers) |

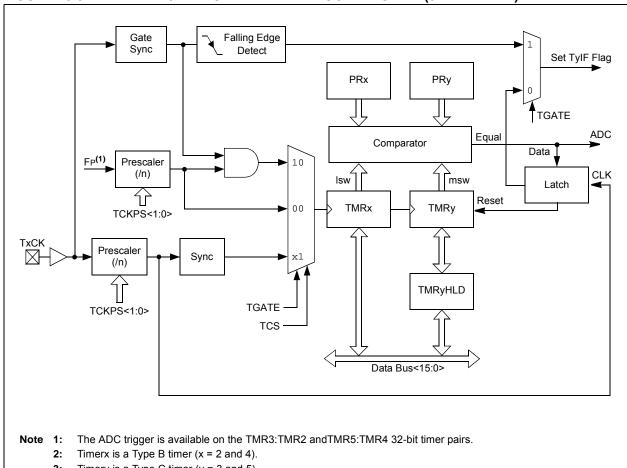

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0      | R/W-0                                                                    | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |

|------------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |

| bit 15     | ·                                                                        |                                                      |                                 |                   | ·                |                        | bit          |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |

| OCTRIG     | G TRIGSTAT                                                               | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |

| bit 7      |                                                                          |                                                      |                                 |                   |                  |                        | bit          |

| Legend:    |                                                                          | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |

| R = Reada  | able bit                                                                 | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |

| -n = Value | at POR                                                                   | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |

|            |                                                                          | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |

| bit 14     | FLTOUT: Fau                                                              |                                                      | . –                             |                   |                  |                        |              |

|            |                                                                          | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |

| bit 13     |                                                                          | ault Output Sta                                      |                                 |                   |                  |                        |              |

|            |                                                                          | is tri-stated on                                     |                                 | 'n                |                  |                        |              |

|            | •                                                                        | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                       | nvert bit                       |                   |                  |                        |              |

|            |                                                                          | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                       | כי                              |                   |                  |                        |              |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |

|            |                                                                          | module operate module operate                        |                                 |                   |                  |                        |              |

| bit 7      |                                                                          | tput Compare x                                       |                                 | Select bit        |                  |                        |              |

|            |                                                                          | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |

|            |                                                                          | nizes OCx with                                       |                                 |                   |                  | S                      |              |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |

| bit 5      |                                                                          | put Compare x                                        |                                 | •                 |                  |                        |              |

|            | 1 = OCx is tr                                                            | • •                                                  | ·                               |                   |                  |                        |              |

|            | 0 = Output C                                                             | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |

| Note 1:    | Do not use the O                                                         | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |

|            | When the OCy m                                                           |                                                      | -                               |                   |                  | module uses t          | he OCv       |

|            | module as a Trigg                                                        |                                                      |                                 |                   |                  |                        |              |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                      |                                 |                   |                  |                        |              |

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0               | R/W-x         | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

|---------------|---------------------------|-------------------|---------------|-----------------------------------------|-------|-------|-------|--|--|

|               | —                         | _                 | SID10         | SID9                                    | SID8  | SID7  | SID6  |  |  |

| bit 15        |                           |                   |               |                                         |       |       | bit 8 |  |  |

| R/W-x         | R/W-x                     | R/W-x             | R/W-x         | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

| SID5          | SID4                      | SID3              | SID2          | SID1                                    | SID0  | SRR   | IDE   |  |  |

| bit 7         |                           |                   |               |                                         | •     |       | bit 0 |  |  |

| Legend:       |                           |                   |               |                                         |       |       |       |  |  |

| R = Readabl   | e bit                     | W = Writable      | bit           | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at | POR                       | '1' = Bit is set  |               | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

|               |                           |                   |               |                                         |       |       |       |  |  |

| bit 15-13     | Unimplemen                | ted: Read as '    | כי            |                                         |       |       |       |  |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | Standard Identifi | ier bits      |                                         |       |       |       |  |  |

| bit 1         | SRR: Substitu             | ute Remote Re     | quest bit     |                                         |       |       |       |  |  |

|               | When IDE =                | 0:                |               |                                         |       |       |       |  |  |

|               | 1 = Message               | will request rer  | note transmis | ssion                                   |       |       |       |  |  |

|               | 0 = Normal m              | nessage           |               |                                         |       |       |       |  |  |

|               | When IDE = 1              | <u>1:</u>         |               |                                         |       |       |       |  |  |

|               | The SRR bit r             | must be set to '  | 1'.           |                                         |       |       |       |  |  |

| bit 0         | IDE: Extende              | d Identifier bit  |               |                                         |       |       |       |  |  |

|               | 1 = Message               | will transmit Ex  | tended Ident  | ifier                                   |       |       |       |  |  |

|               | 0 = Message               | will transmit St  | andard Identi | fier                                    |       |       |       |  |  |

|               |                           |                   |               |                                         |       |       |       |  |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                               | U-0   | U-0              | U-0                                | R/W-x                | R/W-x | R/W-x              | R/W-x |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|-------|--------------------|-------|

| —                                 | —     | —                | _                                  | EID17                | EID16 | EID15              | EID14 |

| bit 15                            |       |                  |                                    |                      |       |                    | bit 8 |

|                                   |       |                  |                                    |                      |       |                    |       |

| R/W-x                             | R/W-x | R/W-x            | R/W-x                              | R/W-x                | R/W-x | R/W-x              | R/W-x |

| EID13                             | EID12 | EID11            | EID10                              | EID9                 | EID8  | EID7               | EID6  |

| bit 7                             |       |                  |                                    |                      |       |                    | bit 0 |

|                                   |       |                  |                                    |                      |       |                    |       |

| Legend:                           |       |                  |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

|                                   |       |                  |                                    |                      |       |                    |       |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

| R/W-x         | R/W-x                             | R/W-x                                                                         | R/W-x         | R/W-x                                   | R/W-x | R/W-x  | R/W-x |  |  |  |

|---------------|-----------------------------------|-------------------------------------------------------------------------------|---------------|-----------------------------------------|-------|--------|-------|--|--|--|

| EID5          | EID4                              | EID3                                                                          | EID2          | EID1                                    | EID0  | RTR    | RB1   |  |  |  |

| bit 15        |                                   |                                                                               |               |                                         |       |        | bit 8 |  |  |  |

|               |                                   |                                                                               |               |                                         |       |        |       |  |  |  |

| U-x           | U-x                               | U-x                                                                           | R/W-x         | R/W-x                                   | R/W-x | R/W-x  | R/W-x |  |  |  |

| —             | —                                 | —                                                                             | RB0           | DLC3                                    | DLC2  | DLC1   | DLC0  |  |  |  |

| bit 7         |                                   |                                                                               |               |                                         |       |        | bit 0 |  |  |  |

| Lonondi       |                                   |                                                                               |               |                                         |       |        |       |  |  |  |

| Legend:       | l. h.:.                           |                                                                               | L.11          |                                         |       | -l (O) |       |  |  |  |

| R = Readab    |                                   | W = Writable                                                                  |               | U = Unimplemented bit, read as '0'      |       |        |       |  |  |  |

| -n = Value a  | t POR                             | '1' = Bit is set                                                              |               | '0' = Bit is cleared x = Bit is unknown |       |        | iown  |  |  |  |

|               |                                   |                                                                               |               |                                         |       |        |       |  |  |  |

| bit 15-10     | EID<5:0>: E                       | xtended Identifi                                                              | er bits       |                                         |       |        |       |  |  |  |

| bit 9         | RTR: Remot                        | RTR: Remote Transmission Request bit                                          |               |                                         |       |        |       |  |  |  |

|               | When IDE = 1:                     |                                                                               |               |                                         |       |        |       |  |  |  |

|               | •                                 | 1 = Message will request remote transmission                                  |               |                                         |       |        |       |  |  |  |

|               |                                   | 0 = Normal message                                                            |               |                                         |       |        |       |  |  |  |

|               |                                   | <u>When IDE = 0:</u><br>The RTR bit is ignored.                               |               |                                         |       |        |       |  |  |  |

| <b>h</b> :+ 0 |                                   |                                                                               |               |                                         |       |        |       |  |  |  |

| bit 8         |                                   | <b>RB1:</b> Reserved Bit 1<br>Jser must set this bit to '0' per CAN protocol. |               |                                         |       |        |       |  |  |  |

|               |                                   |                                                                               | -             | 0001.                                   |       |        |       |  |  |  |

| bit 7-5       | •                                 | nted: Read as '                                                               | 0             |                                         |       |        |       |  |  |  |

| bit 4         | RB0: Reserv                       |                                                                               | <b></b>       |                                         |       |        |       |  |  |  |

|               | User must se                      | et this bit to '0' p                                                          | per CAN proto | ocol.                                   |       |        |       |  |  |  |

| hit 2 0       | DIC 22:00 + Data Langth Code hits |                                                                               |               |                                         |       |        |       |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

#### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|-------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                   |       |                  | Ву    | /te 1                              |       |                    |       |  |

| bit 15            |       |                  |       |                                    |       |                    | bit 8 |  |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |

|                   |       |                  | Ву    | rte 0                              |       |                    |       |  |

| bit 7             |       |                  |       |                                    |       |                    | bit 0 |  |

| Legend:           |       |                  |       |                                    |       |                    |       |  |

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

| _                                                                                                                                                                                                   |                                                                     |                                |                         |                        |                      |                      |                      |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------|-------------------------|------------------------|----------------------|----------------------|----------------------|--|--|--|

| R/W-0                                                                                                                                                                                               | U-0                                                                 | U-0                            | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| ADRC                                                                                                                                                                                                | —                                                                   | —                              | SAMC4 <sup>(1)</sup>    | SAMC3 <sup>(1)</sup>   | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |  |  |  |

| bit 15                                                                                                                                                                                              |                                                                     |                                |                         |                        |                      |                      | bit 8                |  |  |  |

|                                                                                                                                                                                                     |                                                                     |                                |                         |                        |                      |                      |                      |  |  |  |

| R/W-0                                                                                                                                                                                               | R/W-0                                                               | R/W-0                          | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| ADCS7 <sup>(2)</sup>                                                                                                                                                                                | ADCS6 <sup>(2)</sup>                                                | ADCS5 <sup>(2)</sup>           | ADCS4 <sup>(2)</sup>    | ADCS3 <sup>(2)</sup>   | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |  |  |  |

| bit 7                                                                                                                                                                                               | bit 7 bit (                                                         |                                |                         |                        |                      |                      |                      |  |  |  |

| r                                                                                                                                                                                                   |                                                                     |                                |                         |                        |                      |                      |                      |  |  |  |

| Legend:                                                                                                                                                                                             |                                                                     |                                |                         |                        |                      |                      |                      |  |  |  |

| R = Readable b                                                                                                                                                                                      |                                                                     | W = Writable k                 | bit                     | •                      | nented bit, read     | l as '0'             |                      |  |  |  |

| -n = Value at P                                                                                                                                                                                     | OR                                                                  | '1' = Bit is set               |                         | '0' = Bit is clea      | ared                 | x = Bit is unkr      | nown                 |  |  |  |

| bit 15                                                                                                                                                                                              | ADRC: ADC1 Conversion Clock Source bit<br>1 = ADC internal RC clock |                                |                         |                        |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     |                                                                     | ved from syste                 |                         |                        |                      |                      |                      |  |  |  |

| bit 14-13                                                                                                                                                                                           | •                                                                   | ted: Read as '0                |                         |                        |                      |                      |                      |  |  |  |

| bit 12-8                                                                                                                                                                                            |                                                                     | Auto-Sample T                  | ime bits <sup>(1)</sup> |                        |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | 11111 = <b>31</b> T                                                 | AD                             |                         |                        |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | •                                                                   |                                |                         |                        |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | •                                                                   |                                |                         |                        |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | 00001 = 1 TA<br>00000 = 0 TA                                        |                                |                         |                        |                      |                      |                      |  |  |  |

| bit 7-0                                                                                                                                                                                             | ADCS<7:0>:                                                          | ADC1 Convers                   | ion Clock Sele          | ct bits <sup>(2)</sup> |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | 11111111 = <sup>-</sup><br>•                                        | TP • (ADCS<7:                  | 0> + 1) = TP •          | 256 = Tad              |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | •                                                                   |                                |                         |                        |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | 00000010 = -                                                        | TP • (ADCS<7:                  | 0> + 1) = TP •          | 3 = TAD                |                      |                      |                      |  |  |  |

|                                                                                                                                                                                                     | 0000001 =                                                           | TP • (ADCS<7:<br>TP • (ADCS<7: | 0> + 1) = TP •          | 2 <b>=</b> Tad         |                      |                      |                      |  |  |  |

| <ul> <li>Note 1: This bit is only used if SSRC&lt;2:0&gt; (AD1CON1&lt;7:5&gt;) = 111 and SSRCG (AD1CON1&lt;4&gt;) = 0.</li> <li>2: This bit is not used if ADRC (AD1CON3&lt;15&gt;) = 1.</li> </ul> |                                                                     |                                |                         |                        |                      |                      |                      |  |  |  |

#### REGISTER 23-3: AD1CON3: ADC1 CONTROL REGISTER 3

#### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4   | <b>CREF:</b> Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                      |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |

|         |                                                                                                                                                                                                                                                               |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

#### 27.2 User ID Words

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain four User ID Words, located at addresses, 0x800FF8 through 0x800FFE. The User ID Words can be used for storing product information such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

The User ID Words register map is shown in Table 27-3.

TABLE 27-3:USER ID WORDS REGISTER<br/>MAP

| File Name | Address Bits 23-16 |   | Bits 15-0 |

|-----------|--------------------|---|-----------|

| FUID0     | 0x800FF8           | _ | UID0      |

| FUID1     | 0x800FFA           | _ | UID1      |

| FUID2     | 0x800FFC           | _ | UID2      |

| FUID3     | 0x800FFE           | _ | UID3      |

**Legend:** — = unimplemented, read as '1'.

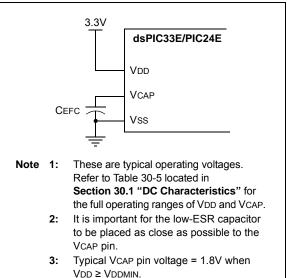

#### 27.3 On-Chip Voltage Regulator

All of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family incorporate an onchip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5 located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE

REGULATOR<sup>(1,2,3)</sup>

## 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.