Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 9x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc204t-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

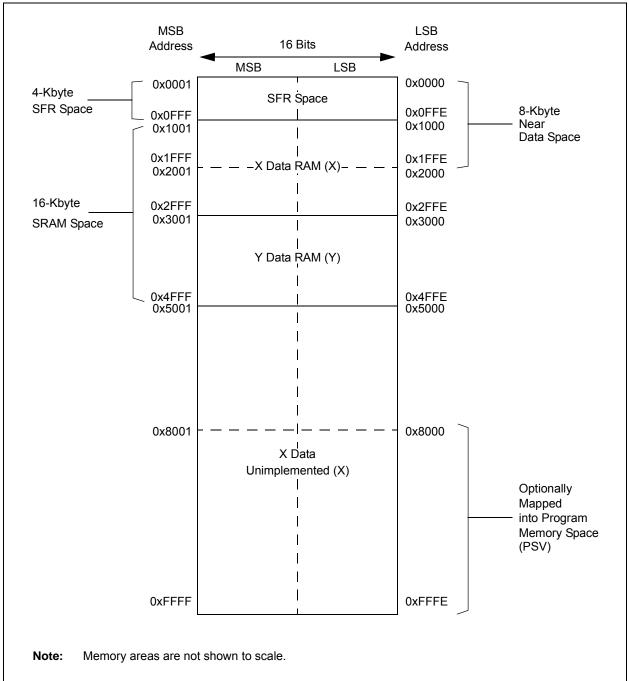

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

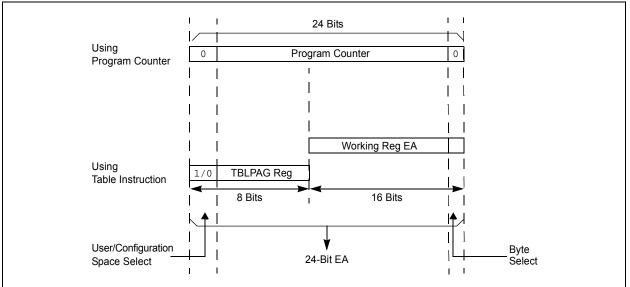

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

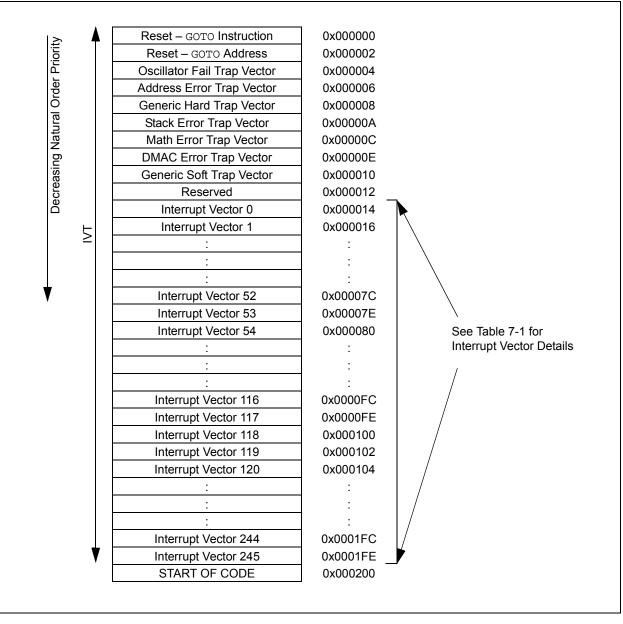

#### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                | U-0                                                                    | U-0                             | U-0                   | U-0              | U-0              | U-0             | U-0            |  |  |  |

|----------------------|------------------------------------------------------------------------|---------------------------------|-----------------------|------------------|------------------|-----------------|----------------|--|--|--|

| FORCE <sup>(1)</sup> |                                                                        | _                               | _                     | —                |                  | _               |                |  |  |  |

| bit 15               |                                                                        |                                 |                       |                  |                  |                 | bit 8          |  |  |  |

|                      |                                                                        |                                 |                       |                  |                  |                 |                |  |  |  |

| R/W-0                | R/W-0                                                                  | R/W-0                           | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0          |  |  |  |

| IRQSEL7              | IRQSEL6                                                                | IRQSEL5                         | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0<br>bit |  |  |  |

| bit 7                |                                                                        |                                 |                       |                  |                  |                 |                |  |  |  |

| Legend:              |                                                                        | S = Settable b                  | oit                   |                  |                  |                 |                |  |  |  |

| R = Readable         | bit                                                                    | W = Writable                    | bit                   | U = Unimpler     | mented bit, read | d as '0'        |                |  |  |  |

| -n = Value at F      | POR                                                                    | '1' = Bit is set                |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown           |  |  |  |

|                      |                                                                        |                                 |                       |                  |                  |                 |                |  |  |  |

| bit 15               | FORCE: Force                                                           | e DMA Transfe                   | er bit <sup>(1)</sup> |                  |                  |                 |                |  |  |  |

|                      | 1 = Forces a single DMA transfer (Manual mode)                         |                                 |                       |                  |                  |                 |                |  |  |  |

|                      | 0 = Automatic DMA transfer initiation by DMA request                   |                                 |                       |                  |                  |                 |                |  |  |  |

| bit 14-8             | Unimplemen                                                             | ted: Read as 'd                 | )'                    |                  |                  |                 |                |  |  |  |

| bit 7-0              | IRQSEL<7:0>                                                            | -: DMA Periphe                  | eral IRQ Num          | ber Select bits  |                  |                 |                |  |  |  |

|                      |                                                                        | ECAN1 – TX D                    |                       | 2)               |                  |                 |                |  |  |  |

|                      |                                                                        | IC4 – Input Ca                  |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | IC3 – Input Ca                  |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | ECAN1 – RX D<br>SPI2 Transfer I | -                     |                  |                  |                 |                |  |  |  |

|                      |                                                                        | UART2TX – UA                    |                       | itter            |                  |                 |                |  |  |  |

|                      |                                                                        | UART2RX – U                     |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | TMR5 – Timer5                   |                       |                  |                  |                 |                |  |  |  |

|                      | 00011011 =                                                             | TMR4 – Timer4                   | 1                     |                  |                  |                 |                |  |  |  |

|                      |                                                                        | OC4 – Output (                  |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | OC3 – Output (                  |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | ADC1 – ADC1                     |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | UART1TX – UA                    |                       |                  |                  |                 |                |  |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver<br>00001010 = SPI1 – Transfer Done |                                 |                       |                  |                  |                 |                |  |  |  |

|                      | 00001000 = TMR3 - Timer3                                               |                                 |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | TMR2 – Timer2                   |                       |                  |                  |                 |                |  |  |  |

|                      |                                                                        | OC2 – Output (                  |                       |                  |                  |                 |                |  |  |  |

|                      | 00000101 = IC2 – Input Capture 2                                       |                                 |                       |                  |                  |                 |                |  |  |  |

|                      | 00000010 =                                                             | OC1 – Output (                  | Compare 1             |                  |                  |                 |                |  |  |  |

|                      |                                                                        | IC1 – Input Ca                  |                       |                  |                  |                 |                |  |  |  |

|                      | 00000000 =                                                             | INT0 – Externa                  | I Interrupt 0         |                  |                  |                 |                |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                                      | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------------------------------------------------------------------|-------|--------------|-------|--------------|------------------|----------|-------|

|                                                                            |       |              | PAD   | <15:8>       |                  |          |       |

| bit 15                                                                     |       |              |       |              |                  |          | bit 8 |

|                                                                            |       |              |       |              |                  |          |       |

| R/W-0                                                                      | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                                                            |       |              | PAE   | )<7:0>       |                  |          |       |

| bit 7                                                                      |       |              |       |              |                  |          | bit 0 |

|                                                                            |       |              |       |              |                  |          |       |

| Legend:                                                                    |       |              |       |              |                  |          |       |

| R = Readable                                                               | bit   | W = Writable | bit   | U = Unimplen | nented bit, read | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |              |       |              |                  | nown     |       |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0                                                                        | R/W-0          | R/W-0 | R/W-0            | R/W-0            | R/W-0     | R/W-0 |

|-----------------|----------------------------------------------------------------------------|----------------|-------|------------------|------------------|-----------|-------|

| —               |                                                                            |                |       | CNT<             | 13:8> <b>(2)</b> |           |       |

| bit 15          |                                                                            |                |       |                  |                  |           | bit 8 |

| R/W-0           | R/W-0                                                                      | R/W-0          | R/W-0 | R/W-0            | R/W-0            | R/W-0     | R/W-0 |

|                 |                                                                            |                | CNT<  | <7:0> <b>(2)</b> |                  |           |       |

| bit 7           |                                                                            |                |       |                  |                  |           | bit 0 |

| Legend:         |                                                                            |                |       |                  |                  |           |       |

| R = Readable b  | oit                                                                        | W = Writable b | bit   | U = Unimplen     | nented bit, rea  | id as '0' |       |

| -n = Value at P | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |       |                  |                  |           | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

#### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# **10.0 POWER-SAVING FEATURES**

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | Sleep mode |  |

|--------|-------------|---|-----|-----|--------|------|------------|--|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | Idle mode  |  |

#### 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

#### 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | U-0                                                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|--|

|                                              | _                                                                                                                                                                            | _                                                                                                                                                                                                                            | _                                                                                                                                | _                                 | _                        | _                           | _    |  |

| bit 15                                       |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |  |

|                                              |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |  |

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | R/W-0                                                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |  |

| _                                            | -                                                                                                                                                                            | _                                                                                                                                                                                                                            | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup>                                 | PTGMD                             | _                        | _                           | _    |  |

| bit 7                                        |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                              | W = Writable<br>'1' = Bit is set                                                                                                                                                                                             |                                                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |  |

| bit 15-5<br>bit 4                            | DMA0MD: DM<br>1 = DMA0 mo<br>0 = DMA0 mo<br>DMA1MD: DM<br>1 = DMA1 mo<br>0 = DMA1 mo<br>DMA2MD: DM<br>1 = DMA2 mo<br>0 = DMA2 mo<br>DMA3MD: DM<br>1 = DMA3 mo<br>0 = DMA3 mo | ted: Read as '<br>MA0 Module Di<br>odule is disable<br>odule is enable<br>MA1 Module Di<br>odule is disable<br>MA2 Module Di<br>odule is disable<br>odule is enable<br>MA3 Module Di<br>odule is disable<br>odule is disable | sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d |                                   |                          |                             |      |  |

| bit 3                                        | <b>PTGMD:</b> PTG Module Disable bit<br>1 = PTG module is disabled<br>0 = PTG module is enabled                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |  |

| bit 2-0                                      | Unimplement                                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                               | 0'                                                                                                                               |                                   |                          |                             |      |  |

| Note 1: T                                    | his single bit ena                                                                                                                                                           | ables and disal                                                                                                                                                                                                              | oles all four DM                                                                                                                 | A channels.                       |                          |                             |      |  |

#### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

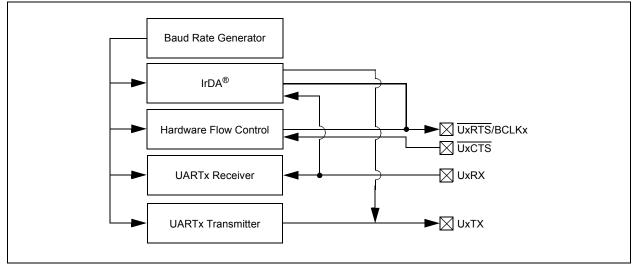

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

#### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

#### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

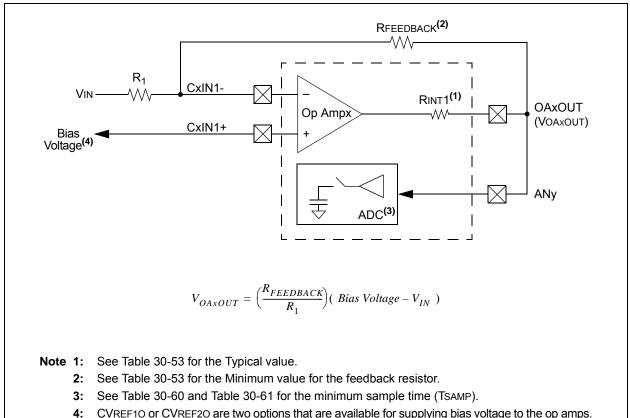

#### 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

## 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                                  | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |

|--------------------|----------------------|--------|--------------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|--|

| 25                 | DAW                  | DAW Wn |                                                  | Wn = decimal adjust Wn                      | 1             | 1                             | С                        |  |

| 26                 | DEC                  | DEC    | f                                                | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC    | f,WREG                                           | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC    | Ws,Wd                                            | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 27                 | DEC2                 | DEC2   | f                                                | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC2   | f,WREG                                           | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | DEC2   | Ws,Wd                                            | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 28                 | DISI                 | DISI   | #lit14                                           | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |  |

| 29                 | DIV                  | DIV.S  | Wm,Wn                                            | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.SD | Wm,Wn                                            | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.U  | Wm,Wn                                            | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |  |

|                    |                      | DIV.UD | Wm,Wn                                            | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |  |

| 30                 | DIVF                 | DIVF   | Wm , Wn <sup>(1)</sup>                           | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |  |

| 31                 | DO                   | DO     | #lit15,Expr <sup>(1)</sup>                       | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |  |

|                    |                      | DO     | Wn, Expr(1)                                      | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |  |

| 32                 | ED                   | ED     | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 33                 | EDAC                 | EDAC   | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>               | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 34                 | EXCH                 | EXCH   | Wns,Wnd                                          | Swap Wns with Wnd                           | 1             | 1                             | None                     |  |

| 35                 | FBCL                 | FBCL   | Ws,Wnd                                           | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |  |

| 36                 | FF1L                 | FF1L   | Ws,Wnd                                           | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |  |

| 37                 | FF1R                 | FF1R   | Ws,Wnd                                           | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |  |

| 38                 | GOTO                 | GOTO   | Expr                                             | Go to address                               | 2             | 4                             | None                     |  |

|                    |                      | GOTO   | Wn                                               | Go to indirect                              | 1             | 4                             | None                     |  |

|                    |                      | GOTO.L | Wn                                               | Go to indirect (long address)               | 1             | 4                             | None                     |  |

| 39                 | INC                  | INC    | f                                                | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC    | f,WREG                                           | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC    | Ws,Wd                                            | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 40                 | INC2                 | INC2   | f                                                | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC2   | f,WREG                                           | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |  |

|                    |                      | INC2   | Ws,Wd                                            | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |  |

| 41                 | IOR                  | IOR    | f                                                | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR    | f,WREG                                           | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR    | #lit10,Wn                                        | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR    | Wb,Ws,Wd                                         | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |  |

|                    |                      | IOR    | Wb,#lit5,Wd                                      | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |  |

| 42                 | LAC                  | LAC    | Wso,#Slit4,Acc                                   | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 43                 | LNK                  | LNK    | #lit14                                           | Link Frame Pointer                          | 1             | 1                             | SFA                      |  |

| 44                 | LSR                  | LSR    | f                                                | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | LSR    | f,WREG                                           | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | LSR    | Ws,Wd                                            | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |  |

|                    |                      | LSR    | Wb,Wns,Wnd                                       | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |  |

|                    |                      | LSR    | Wb,#lit5,Wnd                                     | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |  |

| 45                 | MAC                  | MAC    | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

|                    |                      | MAC    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd(1)                       | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTERISTICS |           |                                                                  | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |      |      |       |                 |  |  |

|--------------------|-----------|------------------------------------------------------------------|----------------------------------------------------------|------|------|-------|-----------------|--|--|

| Param<br>No.       | Symbol    | Characteristic                                                   | Min.                                                     | Тур. | Max. | Units | Conditions      |  |  |

| Operati            | ng Voltag | e                                                                |                                                          |      |      |       |                 |  |  |

| DC10               | Vdd       | Supply Voltage                                                   | 3.0                                                      |      | 3.6  | V     |                 |  |  |

| DC16               | VPOR      | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | -                                                        | _    | Vss  | V     |                 |  |  |

| DC17               | Svdd      | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.03                                                     | _    | —    | V/ms  | 0V-1V in 100 ms |  |  |

#### TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-5: FILTER CAPACITOR (CEFC) SPECIFICATIONS

|              | Standard Operating Conditions (unless otherwise stated):Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                   |     |    |  |    |                                                       |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|----|--|----|-------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol Characteristics Min Typ Max Units Comments                                                                                                                                        |                                                   |     |    |  |    |                                                       |  |  |  |

|              | Cefc                                                                                                                                                                                     | External Filter Capacitor<br>Value <sup>(1)</sup> | 4.7 | 10 |  | μF | Capacitor must have a low series resistance (< 1 Ohm) |  |  |  |

**Note 1:** Typical VCAP voltage = 1.8 volts when VDD  $\geq$  VDDMIN.

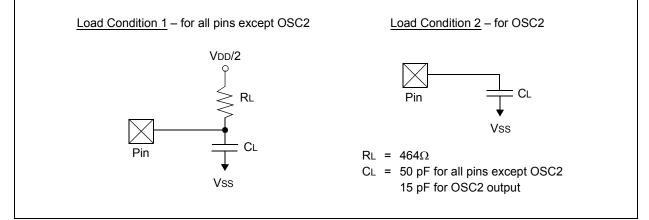

## 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X AC characteristics and timing parameters.

#### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended<br>Operating voltage VDD range as described in <b>Section 30.1 "DC</b> |

|                    | Characteristics".                                                                                                                                                                                       |

#### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    | _    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                           |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | 1 EXTERNAL CLOCK TIMING REQUI | REMENTS <sup>(1)</sup> |

|-------------------|-------------------------------|------------------------|

|-------------------|-------------------------------|------------------------|

|              |           |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                             |

|--------------|-----------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No. | Symbol    | Charao                                                       | cteristic <sup>(2)</sup>                                                                                                                                                                                                                                                                | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TA10         | ТтхН      | T1CK High<br>Time                                            | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|              |           |                                                              | Asynchronous                                                                                                                                                                                                                                                                            | 35                                     | _    | —             | ns    |                                                                             |

| TA11         | ΤτχL      | T1CK Low<br>Time                                             | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|              |           |                                                              | Asynchronous                                                                                                                                                                                                                                                                            | 10                                     | _    | _             | ns    |                                                                             |

| TA15         | ΤτχΡ      | T1CK Input<br>Period                                         | Synchronous mode                                                                                                                                                                                                                                                                        | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60         | Ft1       |                                                              | ange (oscillator<br>etting bit, TCS                                                                                                                                                                                                                                                     | DC                                     |      | 50            | kHz   |                                                                             |

| TA20         | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                                                                                                                                         | 0.75 Tcy + 40                          | —    | 1.75 Tcy + 40 | ns    |                                                                             |

**Note 1:** Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

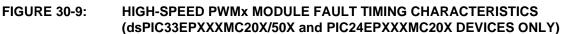

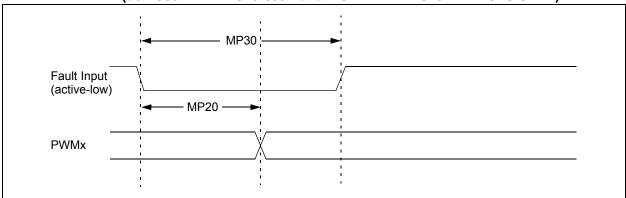

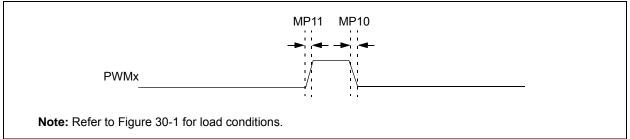

#### FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                    |

|--------------------|--------|-------------------------------------|-------------------------------------------------------|------|------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>       | Min.                                                  | Тур. | Max. | Units | Conditions         |

| MP10               | TFPWM  | PWMx Output Fall Time               |                                                       | —    | _    | ns    | See Parameter DO32 |

| MP11               | TRPWM  | PWMx Output Rise Time               | _                                                     | —    | _    | ns    | See Parameter DO31 |

| MP20               | Tfd    | Fault Input ↓ to PWMx<br>I/O Change | _                                                     | _    | 15   | ns    |                    |

| MP30               | Tfh    | Fault Input Pulse Width             | 15                                                    | —    | _    | ns    |                    |

**Note 1:** These parameters are characterized but not tested in manufacturing.

NOTES: