Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 70 MIPs                                                                       |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                         |

| RAM Size                   | 4K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

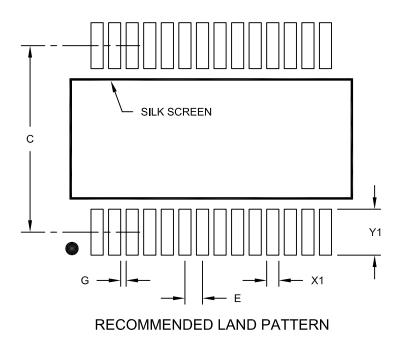

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc206-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | —      | —      | _      | CMPMD  | _      | _      | CRCMD  | _     | —     | _      | —      | —      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _      | _      | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVID7       | 0760  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-1        | R/W-0                                                                                                                            | R/W-0                                     | U-0           | U-0              | U-0              | U-0             | U-0    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------|------------------|------------------|-----------------|--------|

| GIE          | DISI                                                                                                                             | SWTRAP                                    |               |                  |                  | _               |        |

| bit 15       |                                                                                                                                  |                                           |               |                  |                  |                 | bit 8  |

|              |                                                                                                                                  |                                           |               |                  |                  |                 |        |

| U-0          | U-0                                                                                                                              | U-0                                       | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0  |

|              | —                                                                                                                                |                                           |               |                  | INT2EP           | INT1EP          | INT0EP |

| bit 7        |                                                                                                                                  |                                           |               |                  |                  |                 | bit C  |

| Legend:      |                                                                                                                                  |                                           |               |                  |                  |                 |        |

| R = Readab   | le bit                                                                                                                           | W = Writable                              | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value a |                                                                                                                                  | '1' = Bit is set                          |               | '0' = Bit is cle |                  | x = Bit is unki | nown   |

|              |                                                                                                                                  |                                           |               |                  |                  |                 |        |

| bit 15       | GIE: Global                                                                                                                      | Interrupt Enable                          | e bit         |                  |                  |                 |        |

|              | 1 = Interrupt                                                                                                                    | s and associate                           | d IE bits are | enabled          |                  |                 |        |

|              |                                                                                                                                  | s are disabled, I                         | •             | still enabled    |                  |                 |        |

| bit 14       | DISI: DISI                                                                                                                       | nstruction Statu                          | s bit         |                  |                  |                 |        |

|              |                                                                                                                                  | struction is active<br>struction is not a | -             |                  |                  |                 |        |

| bit 13       | SWTRAP: S                                                                                                                        | Software Trap St                          | atus bit      |                  |                  |                 |        |

|              |                                                                                                                                  | e trap is enabled<br>e trap is disabled   |               |                  |                  |                 |        |

| bit 12-3     | Unimpleme                                                                                                                        | nted: Read as '                           | 0'            |                  |                  |                 |        |

| bit 2        | INT2EP: Ext                                                                                                                      | ternal Interrupt 2                        | 2 Edge Detec  | t Polarity Selec | t bit            |                 |        |

|              | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge                                                                 |                                           |               |                  |                  |                 |        |

| bit 1        | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit                                                                     |                                           |               |                  |                  |                 |        |

|              | 1 = Interrupt on negative edge<br>0 = Interrupt on positive edge                                                                 |                                           |               |                  |                  |                 |        |

| bit 0        | INTOEP: Ext                                                                                                                      | ternal Interrupt C                        | Edge Detec    | t Polarity Selec | t bit            |                 |        |

|              | INT0EP: External Interrupt 0 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                           |               |                  |                  |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

# 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |

| bit 13        | Unimplemented: Read as '0'<br>ROSSLP: Reference Oscillator Run in Sleep bit                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |

### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

NOTES:

# 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

| R/W-0                          | U-0                                                                        | U-0                                                                                                                        | U-0                                                              | U-0              | U-0                       | R/W-0              | R/W-0   |  |

|--------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|---------------------------|--------------------|---------|--|

| CHPCLKEN                       | —                                                                          | —                                                                                                                          | —                                                                | —                | —                         | CHOPC              | LK<9:8> |  |

| bit 15                         |                                                                            |                                                                                                                            |                                                                  |                  |                           |                    | bit 8   |  |

|                                |                                                                            |                                                                                                                            |                                                                  |                  |                           |                    |         |  |

| R/W-0                          | R/W-0                                                                      | R/W-0                                                                                                                      | R/W-0                                                            | R/W-0            | R/W-0                     | R/W-0              | R/W-0   |  |

|                                |                                                                            |                                                                                                                            | CHOPC                                                            | LK<7:0>          |                           |                    |         |  |

| bit 7                          |                                                                            |                                                                                                                            |                                                                  |                  |                           |                    | bit 0   |  |

|                                |                                                                            |                                                                                                                            |                                                                  |                  |                           |                    |         |  |

| Legend:                        |                                                                            |                                                                                                                            |                                                                  |                  |                           |                    |         |  |

| R = Readable I                 | bit                                                                        | W = Writable                                                                                                               | bit                                                              | U = Unimplei     | mented bit, read          | as '0'             |         |  |

| -n = Value at P                | OR                                                                         | '1' = Bit is set                                                                                                           |                                                                  | '0' = Bit is cle | eared                     | x = Bit is unknown |         |  |

| bit 15<br>bit 14-10<br>bit 9-0 | 1 = Chop clos<br>0 = Chop clos<br>Unimplemen<br>CHOPCLK<9<br>The frequence | Enable Chop<br>ck generator is<br>ck generator is<br>ted: Read as '<br>9:0>: Chop Clo<br>y of the chop c<br>ncy = (FP/PCL) | enabled<br>disabled<br>0'<br>ck Divider bits<br>lock signal is g | given by the fo  | ollowing expressi<br>+ 1) | on:                |         |  |

# REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|------------------------------------|-------|----------------|-------|------------------|-----------------|-----------------|-------|

|                                    |       |                | MDC   | <15:8>           |                 |                 |       |

| bit 15                             |       |                |       |                  |                 |                 | bit 8 |

|                                    |       |                |       |                  |                 |                 |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                                    |       |                | MD    | C<7:0>           |                 |                 |       |

| bit 7                              |       |                |       |                  |                 |                 | bit 0 |

|                                    |       |                |       |                  |                 |                 |       |

| Legend:                            |       |                |       |                  |                 |                 |       |

| R = Readable                       | bit   | W = Writable b | bit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

# 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | R/W-x                                                                | U-0                           | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

|--------------|----------------------------------------------------------------------|-------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| —            | WAKFIL                                                               |                               | —                |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |  |

| bit 15       |                                                                      |                               |                  |                  |                  |                 | bit     |  |  |  |  |

|              |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

| R/W-x        | R/W-x                                                                | R/W-x                         | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

| SEG2PHTS     | S SAM                                                                | SEG1PH2                       | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |  |

| bit 7        |                                                                      |                               |                  |                  |                  |                 | bit     |  |  |  |  |

| Legend:      |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

| R = Readab   | le bit                                                               | W = Writable                  | bit              | U = Unimpler     | nented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value a |                                                                      | '1' = Bit is set              |                  | '0' = Bit is cle |                  | x = Bit is unkr | nown    |  |  |  |  |

|              |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 15       | Unimplemen                                                           | nted: Read as '               | 0'               |                  |                  |                 |         |  |  |  |  |

| bit 14       | WAKFIL: Sel                                                          | lect CAN Bus L                | ine Filter for V | Vake-up bit      |                  |                 |         |  |  |  |  |

|              |                                                                      | N bus line filter             |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      | line filter is not            |                  | e-up             |                  |                 |         |  |  |  |  |

| bit 13-11    | -                                                                    | nted: Read as '               |                  |                  |                  |                 |         |  |  |  |  |

| bit 10-8     | SEG2PH<2:0>: Phase Segment 2 bits                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 111 = Length is 8 x TQ                                               |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Length                                                         | n is 1 x To                   |                  |                  |                  |                 |         |  |  |  |  |

| bit 7        | -                                                                    |                               | nt 2 Time Sele   | ct bit           |                  |                 |         |  |  |  |  |

|              | SEG2PHTS: Phase Segment 2 Time Select bit<br>1 = Freely programmable |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      | n of SEG1PHx I                | bits or Informa  | tion Processin   | g Time (IPT), w  | hichever is gre | ater    |  |  |  |  |

| bit 6        | SAM: Sample                                                          | e of the CAN B                | us Line bit      |                  |                  |                 |         |  |  |  |  |

|              |                                                                      | s sampled threes sampled once |                  |                  |                  |                 |         |  |  |  |  |

| bit 5-3      | SEG1PH<2:0                                                           | <b>0&gt;:</b> Phase Segr      | nent 1 bits      |                  |                  |                 |         |  |  |  |  |

|              | 111 = Length is 8 x TQ                                               |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Length                                                         |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 2-0      |                                                                      | >: Propagation                | Time Segmen      | t bits           |                  |                 |         |  |  |  |  |

|              | 111 = Length                                                         | IIS8XIQ                       |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                      |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                    |                               |                  |                  |                  |                 |         |  |  |  |  |

# REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 23.1 Key Features

# 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

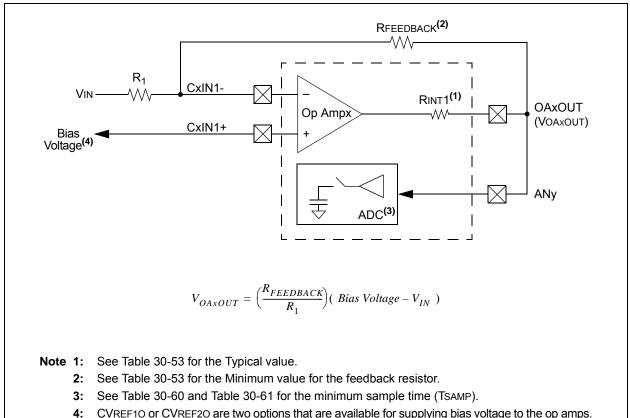

### 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

# 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

| Field                                                                                       | Description                                                                                                                                                                                                                                                          |  |  |  |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Wm,Wn                                                                                       | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                                          |  |  |  |

| Wm*Wm                                                                                       | Multiplicand and Multiplier working register pair for Square instructions $\in$ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                    |  |  |  |

| Wm*Wn                                                                                       | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                        |  |  |  |

| Wn                                                                                          | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                                |  |  |  |

| Wnd                                                                                         | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                                    |  |  |  |

| Wns                                                                                         | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                                         |  |  |  |

| WREG W0 (working register used in file register instructions)                               |                                                                                                                                                                                                                                                                      |  |  |  |

| Ws                                                                                          | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |  |  |  |

| Wso         Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] } |                                                                                                                                                                                                                                                                      |  |  |  |

| Wx                                                                                          | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |  |  |  |

| Wxd                                                                                         | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |  |  |  |

| Wy                                                                                          | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |  |  |  |

| Wyd                                                                                         | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |  |  |  |

| TABLE 28-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED) | ) |

|-------------|-------------------------------------------------|---|

|             | ······································          | , |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | 1 EXTERNAL CLOCK TIMING REQUI | REMENTS <sup>(1)</sup> |

|-------------------|-------------------------------|------------------------|

|-------------------|-------------------------------|------------------------|

| AC CHARACTERISTICS |           |                                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                             |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(2)</sup>                                                                      |                                                                                                                                                                                                                                                                                         | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 35                                     | _    | —             | ns    |                                                                             |

| TA11               | ΤτχL      | T1CK Low<br>Time                                                                                   | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 10                                     | _    | _             | ns    |                                                                             |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                               | Synchronous mode                                                                                                                                                                                                                                                                        | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                                                                                                                                                                                                                                                                                         | DC                                     |      | 50            | kHz   |                                                                             |

| TA20               | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                       |                                                                                                                                                                                                                                                                                         | 0.75 Tcy + 40                          | —    | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

| AC CHARACTERISTICS                        |        |                           | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |          |          |                   |                                                  |  |  |  |

|-------------------------------------------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------------|--------------------------------------------------|--|--|--|

| Param<br>No.                              | Symbol | Characteristic            | Min Typ Max U                                                                                                                             |          |          | Units             | Conditions                                       |  |  |  |

| ADC Accuracy (12-Bit Mode) <sup>(1)</sup> |        |                           |                                                                                                                                           |          |          |                   |                                                  |  |  |  |

| HAD20a                                    | Nr     | Resolution <sup>(3)</sup> | 12                                                                                                                                        | 2 Data B | its      | bits              |                                                  |  |  |  |

| HAD21a                                    | INL    | Integral Nonlinearity     | -5.5                                                                                                                                      | _        | 5.5      | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD22a                                    | DNL    | Differential Nonlinearity | -1                                                                                                                                        | _        | 1        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD23a                                    | Gerr   | Gain Error                | -10                                                                                                                                       |          | 10       | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD24a                                    | EOFF   | Offset Error              | -5                                                                                                                                        | —        | 5        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

|                                           |        | Dynamic I                 | Performa                                                                                                                                  | nce (12- | Bit Mode | e) <sup>(2)</sup> |                                                  |  |  |  |

| HAD33a                                    | Fnyq   | Input Signal Bandwidth    | _                                                                                                                                         | _        | 200      | kHz               |                                                  |  |  |  |

# TABLE 31-12: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

# TABLE 31-13: ADC MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS |        |                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |           |                      |                   |                                                  |

|--------------------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|-------------------|--------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic            | Min Typ Max Units                                                                                                                   |           | Units                | Conditions        |                                                  |

|                    |        | ADC A                     | ccuracy                                                                                                                             | (10-Bit I | Mode) <sup>(1)</sup> |                   |                                                  |

| HAD20b             | Nr     | Resolution <sup>(3)</sup> | 10                                                                                                                                  | ) Data B  | its                  | bits              |                                                  |

| HAD21b             | INL    | Integral Nonlinearity     | -1.5                                                                                                                                | _         | 1.5                  | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD22b             | DNL    | Differential Nonlinearity | -0.25                                                                                                                               | -         | 0.25                 | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD23b             | Gerr   | Gain Error                | -2.5                                                                                                                                |           | 2.5                  | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| HAD24b             | EOFF   | Offset Error              | -1.25                                                                                                                               | _         | 1.25                 | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

|                    |        | Dynamic P                 | erforma                                                                                                                             | nce (10-  | Bit Mode             | e) <sup>(2)</sup> |                                                  |

| HAD33b             | Fnyq   | Input Signal Bandwidth    | _                                                                                                                                   | _         | 400                  | kHz               |                                                  |

Note 1: These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

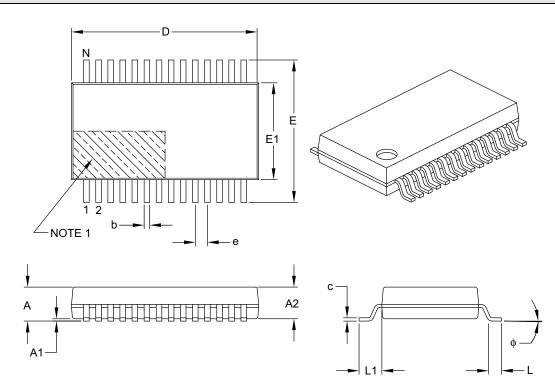

### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |       |       |  |  |

|--------------------------|------------------|-------------|-------|-------|--|--|

| Dime                     | Dimension Limits |             |       | MAX   |  |  |