Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 70 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                  |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep64mc206t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

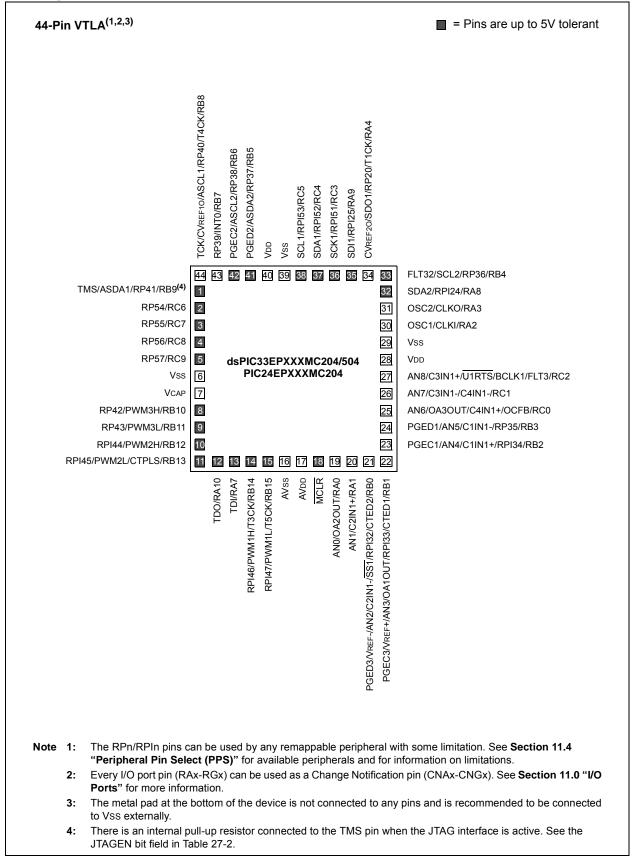

## Pin Diagrams (Continued)

### 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: Cl                                          | PU STATUS I                                                                                                                       | REGISTER                    |                          |                    |                   |               |  |  |  |  |

|------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|--|--|--|--|

| R/W-0                  | R/W-0                                                | R/W-0                                                                                                                             | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |  |  |  |  |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                    | SA <sup>(1,4)</sup>                                                                                                               | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |  |  |  |  |

| bit 15                 |                                                      |                                                                                                                                   |                             |                          |                    |                   | bit 8         |  |  |  |  |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                               | R/W-0 <sup>(2,3)</sup>                                                                                                            | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |  |  |  |  |

| IPL2                   | IPL1                                                 | IPL0                                                                                                                              | RA                          | N                        | OV                 | Z                 | С             |  |  |  |  |

| bit 7                  | ·                                                    | •                                                                                                                                 |                             | •                        |                    |                   | bit (         |  |  |  |  |

| Legend:                |                                                      | C = Clearable                                                                                                                     | e bit                       |                          |                    |                   |               |  |  |  |  |

| R = Readab             | le bit                                               | W = Writable                                                                                                                      | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |  |  |  |  |

| -n = Value a           | t POR                                                | '1'= Bit is set                                                                                                                   |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |  |  |  |  |

|                        |                                                      |                                                                                                                                   |                             |                          |                    |                   |               |  |  |  |  |

| bit 15                 | OA: Accumul                                          | ator A Overflov                                                                                                                   | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                         | ator A has over                                                                                                                   | flowed                      |                          |                    |                   |               |  |  |  |  |

|                        | 0 = Accumula                                         | ator A has not o                                                                                                                  | verflowed                   |                          |                    |                   |               |  |  |  |  |

| bit 14                 | OB: Accumul                                          | ator B Overflov                                                                                                                   | v Status bit <sup>(1)</sup> |                          |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                         | ator B has over                                                                                                                   | flowed                      |                          |                    |                   |               |  |  |  |  |

|                        |                                                      | ator B has not c                                                                                                                  |                             |                          |                    |                   |               |  |  |  |  |

| bit 13                 | SA: Accumul                                          | ator A Saturatio                                                                                                                  | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |  |  |  |  |

|                        |                                                      | <ul> <li>1 = Accumulator A is saturated or has been saturated at some time</li> <li>0 = Accumulator A is not saturated</li> </ul> |                             |                          |                    |                   |               |  |  |  |  |

| bit 12                 | SB: Accumul                                          | ator B Saturatio                                                                                                                  | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |  |  |  |  |

|                        | 1 = Accumula                                         | ator B is saturat<br>ator B is not sat                                                                                            | ted or has bee              |                          | some time          |                   |               |  |  |  |  |

| bit 11                 |                                                      |                                                                                                                                   |                             | vorflow Status           | ы#(1)              |                   |               |  |  |  |  |

|                        |                                                      | <b>OAB:</b> OA    OB Combined Accumulator Overflow Status bit <sup>(1)</sup><br>1 = Accumulators A or B have overflowed           |                             |                          |                    |                   |               |  |  |  |  |

|                        | 0 = Neither Accumulators A or B have overflowed      |                                                                                                                                   |                             |                          |                    |                   |               |  |  |  |  |

| bit 10                 |                                                      | B Combined Ad                                                                                                                     |                             |                          | (1)                |                   |               |  |  |  |  |

|                        |                                                      |                                                                                                                                   |                             |                          | urated at some     | time              |               |  |  |  |  |

|                        | 0 = Neither A                                        | ccumulators A                                                                                                                     | or B are satur              | ated                     |                    |                   |               |  |  |  |  |

| bit 9                  | DA: DO Loop                                          | Active bit <sup>(1)</sup>                                                                                                         |                             |                          |                    |                   |               |  |  |  |  |

|                        | 1 = DO <b>loop is</b>                                | s in progress                                                                                                                     |                             |                          |                    |                   |               |  |  |  |  |

|                        | 0 = DO <b>loop</b> is                                | s not in progres                                                                                                                  | S                           |                          |                    |                   |               |  |  |  |  |

| bit 8                  | DC: MCU AL                                           | U Half Carry/Bo                                                                                                                   | orrow bit                   |                          |                    |                   |               |  |  |  |  |

|                        |                                                      | out from the 4th sult occurred                                                                                                    | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |  |  |  |  |

|                        | 0 = No carry                                         |                                                                                                                                   |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |  |  |  |  |

|                        | his bit is available                                 |                                                                                                                                   |                             |                          |                    |                   | -             |  |  |  |  |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1. |                                                                                                                                   |                             |                          |                    |                   |               |  |  |  |  |

### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

| TABLE 4   | -12:                                                                           | PWM RI   | EGISTE            | R MAP  | FOR de | sPIC33E | PXXXN  | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE  | S ONI       | _Y    |            |       |               |

|-----------|--------------------------------------------------------------------------------|----------|-------------------|--------|--------|---------|--------|----------|----------|---------|-------|--------|---------|-------------|-------|------------|-------|---------------|

| File Name | Addr.                                                                          | Bit 15   | Bit 14            | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4   | Bit 3       | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON     | 0C00                                                                           | PTEN     | —                 | PTSIDL | SESTAT | SEIEN   | EIPU   | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>    | SEVTPS<3:0> |       |            |       | 0000          |

| PTCON2    | 0C02                                                                           | _        | —                 | _      | _      | _       | —      | —        | —        | —       | _     | —      | _       | —           |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04                                                                           |          | PTPER<15:0> 00.   |        |        |         |        |          |          |         |       |        | 00F8    |             |       |            |       |               |

| SEVTCMP   | 0C06                                                                           |          |                   |        |        |         |        |          | SEVTCMP< | 5:0>    |       |        |         |             |       |            |       | 0000          |

| MDC       | 0C0A                                                                           |          |                   |        |        |         |        |          | MDC<15:  | )>      |       |        |         |             |       |            |       | 0000          |

| CHOP      | 0C1A                                                                           | CHPCLKEN | _                 | _      | _      | _       | _      |          |          |         |       | CHOPCI | _K<9:0> |             |       |            |       | 0000          |

| PWMKEY    | 0C1E                                                                           |          | PWMKEY<15:0> 0000 |        |        |         |        |          |          |         | 0000  |        |         |             |       |            |       |               |

| Legend: - | Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |          |                   |        |        |         |        |          |          |         |       |        |         |             |       |            |       |               |

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |            |         |                                                       |                                                | I OIT U |        |           |          |        | 1102- |        |       |          |       |       |               |

|-----------|-------|---------|------------|---------|-------------------------------------------------------|------------------------------------------------|---------|--------|-----------|----------|--------|-------|--------|-------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15  | Bit 14     | Bit 13  | Bit 12                                                | Bit 11                                         | Bit 10  | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT     | TRGSTAT | FLTIEN                                                | CLIEN                                          | TRGIEN  | ITB    | MDCS      | DTC<     | :1:0>  | DTCP  | _      | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON1    | 0C22  | PENH    | PENL       | POLH    | POLL                                                  | PMOD                                           | <1:0>   | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA | T<1:0> | CLDA  | T<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON1   | 0C24  | _       |            | (       | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> |                                                |         |        |           |          |        | 0000  |        |       |          |       |       |               |

| PDC1      | 0C26  |         | PDC1<15:0> |         |                                                       |                                                |         |        |           |          |        | FFF8  |        |       |          |       |       |               |

| PHASE1    | 0C28  |         |            |         | PHASE1<15:0>                                          |                                                |         |        |           |          |        |       |        | 0000  |          |       |       |               |

| DTR1      | 0C2A  | _       | _          |         |                                                       |                                                |         |        |           | DTR1<13: | 0>     |       |        |       |          |       |       | 0000          |

| ALTDTR1   | 0C2C  | _       | _          |         |                                                       |                                                |         |        | А         | LTDTR1<1 | 3:0>   |       |        |       |          |       |       | 0000          |

| TRIG1     | 0C32  |         |            |         |                                                       |                                                |         |        | TRGCMP<18 | 5:0>     |        |       |        |       |          |       |       | 0000          |

| TRGCON1   | 0C34  |         | TRGDI      | V<3:0>  |                                                       | _                                              | _       | _      | _         | _        | _      |       |        | TRG   | STRT<5:0 | >     |       | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF        | PLR     | PLF                                                   | FLTLEBEN                                       | CLLEBEN | _      | _         | _        | _      | BCH   | BCL    | BPHH  | BPHL     | BPLH  | BPLL  | 0000          |

| LEBDLY1   | 0C3C  | _       | _          | —       | LEB<11:0>C                                            |                                                |         |        |           |          |        | 0000  |        |       |          |       |       |               |

| AUXCON1   | 0C3E  | —       | —          | _       |                                                       | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN |         |        |           |          |        |       | 0000   |       |          |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

### **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0        | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |  |  |  |

|--------|------------|-------|-------|-------|-------|-------|-------|--|--|--|

| —      | —          |       |       | —     | —     | —     | —     |  |  |  |

| bit 15 |            |       |       |       |       |       | bit 8 |  |  |  |

|        |            |       |       |       |       |       |       |  |  |  |

| U-0    | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

| —      | U1RXR<6:0> |       |       |       |       |       |       |  |  |  |

| bit 7  |            |       |       |       |       |       | bit 0 |  |  |  |

|        |            |       |       |       |       |       |       |  |  |  |

### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0-0     | 0-0   | 0-0   | 0-0   | 0-0        | 0-0   | 0-0   | 0-0   |

|         | —     |       | _     | _          | —     | —     |       |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —       |       |       |       | U2RXR<6:0> | >     |       |       |

| bit 7   |       |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Legend: |       |       |       |            |       |       |       |

|         |       |       |       |            |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                                                                                                                              | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------------------------|--------|--------------------|-------|--|--|

| —               | —                                                                                                                                                |                  |       | RP57                               | R<5:0> |                    |       |  |  |

| bit 15          |                                                                                                                                                  |                  |       |                                    |        |                    | bit 8 |  |  |

|                 |                                                                                                                                                  |                  |       |                                    |        |                    |       |  |  |

| U-0             | U-0                                                                                                                                              | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |  |

| _               | —                                                                                                                                                |                  |       | RP56                               | R<5:0> |                    |       |  |  |

| bit 7           |                                                                                                                                                  |                  |       |                                    |        |                    | bit 0 |  |  |

|                 |                                                                                                                                                  |                  |       |                                    |        |                    |       |  |  |

| Legend:         |                                                                                                                                                  |                  |       |                                    |        |                    |       |  |  |

| R = Readable I  | bit                                                                                                                                              | W = Writable     | bit   | U = Unimplemented bit, read as '0' |        |                    |       |  |  |

| -n = Value at P | OR                                                                                                                                               | '1' = Bit is set | :     | '0' = Bit is clea                  | ared   | x = Bit is unknown |       |  |  |

|                 |                                                                                                                                                  |                  |       |                                    |        |                    |       |  |  |

| bit 15-14       | Unimplemen                                                                                                                                       | ted: Read as '   | 0'    |                                    |        |                    |       |  |  |

| bit 13-8        | it 13-8 <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers) |                  |       |                                    |        |                    |       |  |  |

| bit 7-6         | Unimplemen                                                                                                                                       | ted: Read as '   | 0'    |                                    |        |                    |       |  |  |

### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

#### 18.3 SPIx Control Registers

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 SPIEN SPISIDL SPIBEC<2:0> \_\_\_\_\_ bit 15 R/W-0 R/W-0 R/W-0 R/C-0, HS R/W-0 R/W-0 R-0, HS, HC R-0, HS, HC SRMPT SPIROV SRXMPT SISEL2 SISEL1 SISEL0 SPITBF SPIRBF bit 7 Legend: C = Clearable bit HS = Hardware Settable bit HC = Hardware Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables the module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables the module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues the module operation when device enters Idle mode 0 = Continues the module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPIx transfers that are pending. Slave mode: Number of SPIx transfers that are unread. SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) bit 7 1 = SPIx Shift register is empty and Ready-To-Send or receive the data 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit

#### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register 0 = No overflow has occurred SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

- 1 = RX FIFO is empty

- 0 = RX FIFO is not empty

#### bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

- 111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

- 110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

- 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

- 100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

- 011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

- 010 = Interrupt when the SPIx receive buffer is 3/4 or more full

- 001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

- 000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

bit 5

bit 8

bit 0

# 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

## REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGHOL | _D<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------|-------|-------|-------|

|       |       |       | PTGHO | LD<7:0> |       |       |       |

| bit 7 |       |       |       |         |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| R/W-0         | R/W-0              | R/W-0                              | U-0                 | U-0              | R/W-0            | R/W-0               | R/W-0               |

|---------------|--------------------|------------------------------------|---------------------|------------------|------------------|---------------------|---------------------|

| CON           | COE <sup>(2)</sup> | CPOL                               | _                   | —                | OPMODE           | CEVT                | COUT                |

| bit 15        |                    |                                    |                     |                  |                  |                     | bit 8               |

|               |                    |                                    |                     |                  |                  |                     |                     |

| R/W-0         | R/W-0              | U-0                                | R/W-0               | U-0              | U-0              | R/W-0               | R/W-0               |

| EVPOL1        | EVPOL0             | —                                  | CREF <sup>(1)</sup> | _                | —                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| bit 7         |                    |                                    |                     |                  |                  |                     | bit (               |

| Legend:       |                    |                                    |                     |                  |                  |                     |                     |

| R = Readabl   | e bit              | W = Writable                       | bit                 | U = Unimple      | mented bit, read | as '0'              |                     |

| -n = Value at | POR                | '1' = Bit is set                   |                     | '0' = Bit is cle | eared            | x = Bit is unkr     | nown                |

|               |                    |                                    |                     |                  |                  |                     |                     |

| bit 15        | CON: Op Am         | p/Comparator                       | Enable bit          |                  |                  |                     |                     |

|               |                    | comparator is e                    |                     |                  |                  |                     |                     |

|               |                    | comparator is d                    |                     |                  |                  |                     |                     |

| bit 14        |                    | arator Output Ei                   |                     |                  |                  |                     |                     |

|               |                    | tor output is pre                  |                     | CxOUT pin        |                  |                     |                     |

|               | -                  | tor output is int                  | -                   |                  |                  |                     |                     |

| bit 13        | •                  | parator Output I                   | •                   | t bit            |                  |                     |                     |

|               |                    | tor output is inv                  |                     |                  |                  |                     |                     |

|               | -                  | tor output is no                   |                     |                  |                  |                     |                     |

| bit 12-11     | •                  | ted: Read as '                     |                     |                  |                  |                     |                     |

| bit 10        |                    | p Amp/Compar                       | •                   | n Mode Select    | t bit            |                     |                     |

|               |                    | perates as an o<br>perates as a co |                     |                  |                  |                     |                     |

| bit 9         | •                  | arator Event bi                    | •                   |                  |                  |                     |                     |

|               | 1 = Compara        |                                    | rding to the E      | VPOL<1:0> s      | ettings occurred | ; disables futur    | e triggers and      |

|               |                    | ator event did n                   |                     |                  |                  |                     |                     |

| bit 8         | COUT: Comp         | parator Output b                   | oit                 |                  |                  |                     |                     |

|               |                    | = 0 (non-invert                    |                     |                  |                  |                     |                     |

|               | 1 = VIN+ > VI      | N-                                 | • • • • •           |                  |                  |                     |                     |

|               | 0 = VIN + < VI     |                                    |                     |                  |                  |                     |                     |

|               |                    | = 1 (inverted p                    | olarity):           |                  |                  |                     |                     |

|               | 1 = VIN + < VI     |                                    |                     |                  |                  |                     |                     |

|               | 0 = VIN + > VI     | N-                                 |                     |                  |                  |                     |                     |

### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3)

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4   | <b>CREF:</b> Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                      |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |

|         |                                                                                                                                                                                                                                                               |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

# 26.3 Programmable CRC Registers

### REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0                            | U-0                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R-0                                                                                      | R-0                                                | R-0             | R-0            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|----------------|

| CRCEN                            | —                                                                                                                                                                                                                                                             | CSIDL                                                                                                                                                                                                                                                                  | VWORD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VWORD3                                                                                   | VWORD2                                             | VWORD1          | VWORD0         |

| bit 15                           | ·                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                          |                                                    |                 | bit 8          |

| R-0                              | R-1                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                    | U-0                                                | U-0             | U-0            |

| CRCFUL                           | CRCMPT                                                                                                                                                                                                                                                        | CRCISEL                                                                                                                                                                                                                                                                | CRCGO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LENDIAN                                                                                  | _                                                  | _               | _              |

| bit 7                            | •                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                          |                                                    |                 | bit (          |

| Legend:                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                          |                                                    |                 |                |

| R = Readable                     | e bit                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                           | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U = Unimplen                                                                             | nented bit, read                                   | d as '0'        |                |