# E. Renesas Electronics America Inc - M30281FATHP#U3AAD1 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                   |

| Core Size                  | -                                                                                   |

| Speed                      | -                                                                                   |

| Connectivity               | -                                                                                   |

| Peripherals                | -                                                                                   |

| Number of I/O              | -                                                                                   |

| Program Memory Size        | -                                                                                   |

| Program Memory Type        | -                                                                                   |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | -                                                                                   |

| Voltage - Supply (Vcc/Vdd) | -                                                                                   |

| Data Converters            | -                                                                                   |

| Oscillator Type            | -                                                                                   |

| Operating Temperature      | -                                                                                   |

| Mounting Type              | -                                                                                   |

| Package / Case             | -                                                                                   |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30281fathp-u3aad1 |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Quick Reference to Pages Classified by Address

|                    |                                          |          | i    |                  |                                                         |             | 1        |

|--------------------|------------------------------------------|----------|------|------------------|---------------------------------------------------------|-------------|----------|

| Address            | Register                                 | Symbol   | Page | Address          | Register                                                | Symbol      | Page     |

| 018016             |                                          |          |      | 024016           |                                                         |             |          |

| 018116             |                                          |          |      | 024116           |                                                         |             |          |

| 018216             |                                          |          |      | 024216           |                                                         |             |          |

| 018316             |                                          |          |      | 024316           |                                                         |             |          |

| 018416             |                                          |          |      | 024416           |                                                         |             |          |

| 018516             |                                          |          |      | 024516           |                                                         |             |          |

| 018616             |                                          |          |      | 024616           |                                                         |             |          |

| 018716             |                                          |          |      | 024716           |                                                         |             |          |

| to                 |                                          |          |      | 024816           |                                                         |             |          |

| 01AF16             |                                          |          |      | 024916           |                                                         |             |          |

| 01B016             |                                          |          |      | 024A16           |                                                         |             |          |

| 01B116             |                                          |          |      | 024C16           |                                                         |             |          |

| 01B216             |                                          |          |      | 024D16           |                                                         |             |          |

| 01B316             | Flash memory control register 4 (Note 2) | FMR4     | 304  | 024E16           |                                                         |             |          |

| 01B416             |                                          |          |      | 024F16           |                                                         |             |          |

| 01B516             | Flash memory control register 1 (Note 2) | FMR1     | 303  | 025016           |                                                         |             |          |

| 01B616             |                                          |          |      | 025116           |                                                         |             |          |

| 01B7 <sub>16</sub> | Flash memory control register 0 (Note 2) | FMR0     | 303  | 025216           |                                                         |             |          |

| 01B816             |                                          |          |      | 025316           |                                                         |             |          |

| 01B916             |                                          |          |      | 025416           |                                                         |             |          |

| 01BA16             |                                          |          |      | 025516           |                                                         |             |          |

| 01BB16             |                                          |          |      | 025616           |                                                         |             |          |

| 01BC16             |                                          |          |      | 025716           |                                                         |             |          |

| 01BD16             |                                          |          |      | 025816           |                                                         |             |          |

| to                 |                                          |          |      | 025916           |                                                         |             |          |

| 019F16             |                                          |          |      | 025A16           | Three-phase protect control register                    | TPRC        | 128      |

| 020016             |                                          |          |      | 025B16           | <u> </u>                                                |             |          |

| 020116             |                                          |          |      | 025C16           | On-chip oscillator control register                     | ROCR        | 39       |

| 020216             |                                          |          |      | 025D16           | Pin assignment control register                         | PACR        | 166, 289 |

| 020316             |                                          |          |      | 025E16           | Peripheral clock select register                        | PCLKR       | 41       |

| 020416             |                                          |          |      | 025F16           | Low-power consumption control register 1                | LPCC1       | 359      |

| 020516             |                                          |          |      | 026016           |                                                         | 2. 00.      |          |

| 020616             |                                          |          |      | 026116           |                                                         |             |          |

| 020716             |                                          |          |      | 026216           |                                                         |             |          |

| 020816             |                                          |          |      | 026316           |                                                         |             |          |

| 020916             |                                          |          |      | 026416           |                                                         |             |          |

| 020A16             |                                          |          |      | 026516           |                                                         |             |          |

| 020B16             |                                          |          |      | 026616           |                                                         |             |          |

| 020C16             |                                          |          |      | 026716           |                                                         |             |          |

| 020D16             |                                          |          |      | 026816           |                                                         |             |          |

| 020E16             |                                          |          |      | 026916           |                                                         |             |          |

| 020F16             |                                          |          |      | 026A16           |                                                         |             |          |

| 021016             | Low-power consumption control register 0 | LPCC0    | 359  | 026B16           |                                                         |             |          |

| 021116             |                                          | 21 000   | 000  | 026C16           |                                                         |             |          |

| 021216             |                                          |          |      | 026D16           |                                                         |             |          |

| 021316             |                                          |          |      | to               |                                                         |             |          |

| 021016             |                                          |          |      | 02DF16           |                                                         |             |          |

| 021516             |                                          |          |      | 02DF16           |                                                         |             |          |

| 021616             |                                          |          |      |                  | I <sup>2</sup> C0 data shift register                   | S00         | 247      |

| 021716             |                                          |          |      | 02E116           |                                                         |             |          |

| 021816             |                                          |          |      |                  | I <sup>2</sup> C0 address register                      | S0D0        | 246      |

| 021016             |                                          |          |      | 02E316           | I <sup>2</sup> C0 control register 0                    | S1D0        | 240      |

| 021010<br>021A16   |                                          |          |      | 02E416           | I <sup>2</sup> C0 clock control register                | S20         | 240      |

| 021A16             |                                          |          |      |                  | I <sup>2</sup> C0 start/stop condition control register |             | 252      |

| 021B16<br>021C16   |                                          |          |      |                  | I <sup>2</sup> C0 control register 1                    | S3D0        | 252      |

| 021C16             |                                          |          |      |                  | I <sup>2</sup> C0 control register 2                    | S4D0        | 250      |

| 021D16<br>021E16   |                                          |          |      | 02E716           | I <sup>2</sup> C0 status register                       | S4D0<br>S10 | 231      |

| 021E16<br>021F16   |                                          | <u> </u> |      | 02E816<br>02E916 |                                                         | 510         | 249      |

| 021F16             |                                          |          |      | 02E916<br>02EA16 |                                                         |             |          |

| 021016             |                                          |          |      | 02EA16<br>02EB16 |                                                         |             |          |

|                    |                                          |          |      |                  |                                                         |             |          |

| to<br>02FD16       |                                          |          |      | to<br>02FE16     |                                                         |             |          |

|                    |                                          |          |      |                  |                                                         |             |          |

| 02FE16             |                                          |          |      | 02FE16           |                                                         |             |          |

| 02FF16             |                                          |          |      | 02FF16           |                                                         |             |          |

Note 1: The blank areas are reserved and cannot be accessed by users. Note 2: This register is included in the flash memory version.

|                                                                                     | b4 b3                                                                                                                                                                                                                                         | b2 t                                                                                                                                         | b1 b0                                                                                                                                                 | Symbo<br>PM2                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | After Reset<br>XXX000002                                                                                                                                                                              |             |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                                                                                     |                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                       | Bit Symbol                                                                                                                                                                                                                                                                           | Bit Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                                                                                                                              | RV          |

|                                                                                     |                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                       | PM20                                                                                                                                                                                                                                                                                 | Specifying wait when<br>accessing SFR during PLL<br>operation <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0: 2 waits<br>1: 1 wait                                                                                                                                                                               | RV          |

|                                                                                     |                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                       | PM21                                                                                                                                                                                                                                                                                 | System clock protective $bit^{(3,4)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0: Clock is protected by PRCR<br>register<br>1: Clock modification disabled                                                                                                                           | RV          |

|                                                                                     |                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                       | PM22                                                                                                                                                                                                                                                                                 | WDT count source protective bit <sup>(3,5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0: CPU clock is used for the<br>watchdog timer count source<br>1: On-chip oscillator clock is used<br>for the watchdog timer count<br>source                                                          | RV          |

|                                                                                     |                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                       | (b3)                                                                                                                                                                                                                                                                                 | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Set to "0"                                                                                                                                                                                            | RV          |

|                                                                                     |                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                       | PM24                                                                                                                                                                                                                                                                                 | P85/NMI configuration bit <sup>(6,7)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0: P85 function (NMI disable)<br>1: NMI function                                                                                                                                                      | RV          |

|                                                                                     |                                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                       |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |             |

| 1. Write<br>2. The                                                                  | PM20 b                                                                                                                                                                                                                                        | bit bec                                                                                                                                      | ome e                                                                                                                                                 | effective when                                                                                                                                                                                                                                                                       | Nothing is assigned. When writ<br>When read,its content is indete<br>PRC1 bit in the PRCR register to<br>PLC07 bit in the PLC0 register i                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | L<br>e, set to"0".<br>rminate<br>0 "1" (write enable).<br>is set to "1" (PLL on). Change the PI                                                                                                       |             |

| 2. The<br>whe<br>3. Onc<br>4. Writi<br>5. Setti<br>- Th<br>Pl<br>- Th<br>so<br>- Th | PM20 t<br>en the P<br>the this b<br>ing to the<br>CM02 the<br>CM05 the<br>CM07 the<br>CM07 the<br>CM10 the<br>CM10 the<br>CM10 the<br>CM10 the<br>CM20 the<br>All bits<br>here the<br>ing the<br>the on-cl<br>LL clock<br>the on-cl<br>burce. | bit bec<br>LC07<br>it is see<br>follo<br>bit in the<br>bit in the<br>bit in the<br>bit in the<br>PM21<br>PM22<br>hip ose<br>(syse<br>hip ose | come e<br>bit is set to "1<br>owing<br>ne CM<br>ne CM<br>ne CM<br>ne CM<br>ne CM<br>pe CM<br>pe CM<br>pe CM<br>bit is<br>bit to<br>cillator<br>tem cl | er setting the<br>effective when<br>set to "0" (PLL<br>", it cannot be<br>bits has no ef<br>10 register<br>10 register (CF<br>11 register (CF<br>12 register (CF<br>12 register (CPL<br>set to "1", do<br>"1" results in 1<br>r continues os<br>ock of count set<br>r starts oscilla | When read,its content is indete<br>PRC1 bit in the PRCR register to<br>PLC07 bit in the PLC0 register i<br>off). Set the PM20 bit to "0" (2 v<br>e set to "0" by program.<br>fect when the PM21 bit is set to "<br>ain clock is not halted)<br>PU clock source does not change<br>prode is not entered)<br>PU clock source does not change<br>cillation stop, re-oscillation detec<br>frequency synthesizer setting do<br>not execute the WAIT instruction<br>the following conditions:<br>cillating even if the CM21 bit in the<br>source selected by the CM21 bit<br>ting, and the on-chip oscillator clo | e, set to"0".<br>rminate<br>0 "1" (write enable).<br>is set to "1" (PLL on). Change the PI<br>vaits) when PLL clock > 16 MHz.<br>(1":<br>(1":<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | )<br>lock ( |

Figure 6.2 PM2 Register

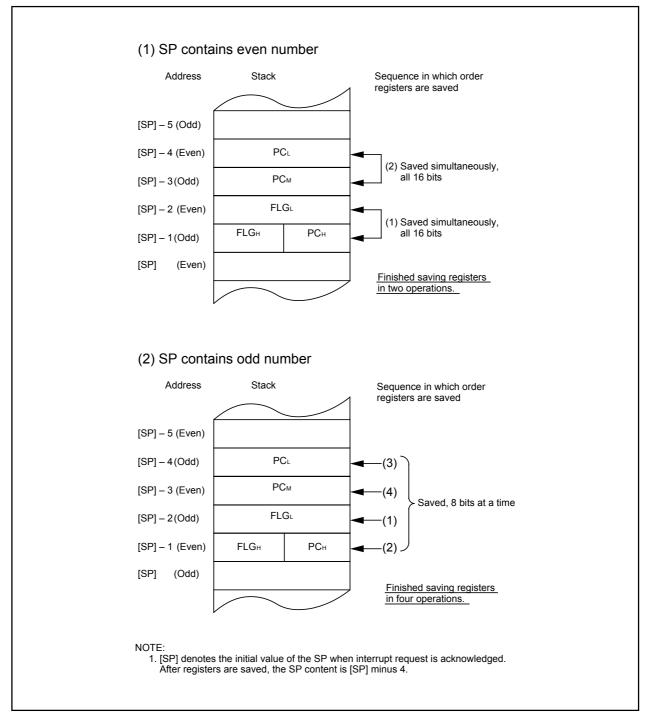

The operation of saving registers carried out in the interrupt sequence is dependent on whether the  $SP^{(1)}$ , at the time of acceptance of an interrupt request, is even or odd. If the stack pointer <sup>(1)</sup> is even, the FLG register and the PC are saved, 16 bits at a time. If odd, they are saved in two steps, 8 bits at a time. **Figure 9.8** shows the operation of the saving registers.

NOTE:

1. When any INT instruction in software numbers 32 to 63 has been executed, this is the SP indicated by the U flag. Otherwise, it is the ISP.

Figure 9.8 Operation of Saving Register

# 9.9 Address Match Interrupt

An address match interrupt request is generated immediately before executing the instruction at the address indicated by the RMADi register (i=0 to 1). Set the start address of any instruction in the RMADi register. Use bits AIER1 and AIER0 in the AIER register to enable or disable the interrupt. Note that the address match interrupt is unaffected by the I flag and IPL. For address match interrupts, the value of the PC that is saved to the stack area varies depending on the instruction being executed (refer to "**Saving Registers**").

(The value of the PC that is saved to the stack area is not the correct return address.) Therefore, follow one of the methods described below to return from the address match interrupt.

• Rewrite the content of the stack and then use the REIT instruction to return.

• Restore the stack to its previous state before the interrupt request was accepted by using the POP or similar other instruction and then use a jump instruction to return.

**Table 9.6** shows the value of the PC that is saved to the stack area when an address match interrupt request is accepted.

Figure 9.13 shows registers AIER, RMAD0, and RMAD1.

#### Table 9.6 Value of the PC that is saved to the stack area when an address match interrupt request is accepted.

|                                                                                           | Instruction a                                                                                   | at the addre                                  | ss indicated by the RN                                         | /IADi regist                | er                             | Value of the PC that is saved to the stack area      |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------|-----------------------------|--------------------------------|------------------------------------------------------|

| 2-byte op-co<br>1-byte op-co<br>ADD.B:S<br>OR.B:S<br>STNZ.B<br>CMP.B:S<br>JMPS<br>MOV.B:S | de instruction<br>de instructions w<br>#IMM8,dest<br>#IMM8,dest<br>#IMM8,dest<br>#IMM8<br>#IMM8 | SUB.B:S<br>MOV.B:S<br>STZX.B<br>PUSHM<br>JSRS | #IMM8,dest<br>#IMM8,dest<br>#IMM81,#IMM82,dest<br>src<br>#IMM8 | AND.B:S<br>STZ.B<br>POPM de | #IMM8,dest<br>#IMM8,dest<br>st | The address<br>indicated by the<br>RMADi register +2 |

| Instructions ot                                                                           | her than the abo                                                                                | ve                                            |                                                                |                             |                                | The address<br>indicated by the<br>RMADi register +1 |

Value of the PC that is saved to the stack area : Refer to "Saving Registers".

Op-code is an abbreviation of Operation Code. It is a portion of instruction code.

Refer to Chapter 4 Instruction Code/Number of Cycles in M16C/60, M16C/20 Series Software Manual. Op-code is shown as a bold-framed figure directly below the Syntax.

#### Table 9.7 Relationship Between Address Match Interrupt Sources and Associated Registers

| Address match interrupt sources | Address match interrupt enable bit | Address match interrupt register |

|---------------------------------|------------------------------------|----------------------------------|

| Address match interrupt 0       | AIER0                              | RMAD0                            |

| Address match interrupt 1       | AIER1                              | RMAD1                            |

| 7         66         b5         b4         b3         b2         b1         b0           0         1         0         1         0         1         0 | ter<br>Symbol<br>TA1MR<br>TA2MR<br>TA4MR<br>Bit Symbol                       | Address<br>039716<br>039816<br>039A16<br>Bit Name                                                                                                                        | After Reset<br>0016<br>0016<br>0016<br>Function                                                                                                                                                                                                                                                                                                                                                                                   | RW                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                                                                                                                                        | TMOD0                                                                        |                                                                                                                                                                          | Set to 102 (one-shot timer mode) for the                                                                                                                                                                                                                                                                                                                                                                                          | RW                                                       |

|                                                                                                                                                        | TMOD0                                                                        | Operation mode select bit                                                                                                                                                | three-phase motor control timer function                                                                                                                                                                                                                                                                                                                                                                                          | RW                                                       |

|                                                                                                                                                        | MR0                                                                          | Pulse output function select bit                                                                                                                                         | Set to 0 for the three-phase motor control timer function                                                                                                                                                                                                                                                                                                                                                                         | RW                                                       |

|                                                                                                                                                        | MR1                                                                          | External trigger select bit                                                                                                                                              | No effect for the three-phase motor control timer function                                                                                                                                                                                                                                                                                                                                                                        | RW                                                       |

| ۱ <u>ـــــ</u>                                                                                                                                         | MR2                                                                          | Trigger select bit                                                                                                                                                       | Set to 1 (selected by event/trigger select register) for the three-phase motor control timer function                                                                                                                                                                                                                                                                                                                             | RW                                                       |

|                                                                                                                                                        | MR3                                                                          | Set to 0 for the three-pha                                                                                                                                               | se motor control timer function                                                                                                                                                                                                                                                                                                                                                                                                   | RW                                                       |

|                                                                                                                                                        | TCK0                                                                         | Count source select bit                                                                                                                                                  | b7 b6<br>0 0 : f1 or f2<br>0 1 : f8                                                                                                                                                                                                                                                                                                                                                                                               | RW                                                       |

| l                                                                                                                                                      |                                                                              |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|                                                                                                                                                        | TCK1                                                                         |                                                                                                                                                                          | 1 0 : f32<br>1 1 : fC32                                                                                                                                                                                                                                                                                                                                                                                                           | RW                                                       |

| Timer B2 Mode Regi<br><u>b7 b6 b5 b4 b3 b2 b1 b0</u> 0 0 0                                                                                             | ster<br>Symbol<br>TB2MR                                                      | Address<br>039D16                                                                                                                                                        | 1 1 : fc32<br>After Reset<br>00XX00002                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | Ster<br>Symbol<br>TB2MR<br>Bit Symbol                                        |                                                                                                                                                                          | 1 1 : fc32<br>After Reset                                                                                                                                                                                                                                                                                                                                                                                                         | RW                                                       |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | ster<br>Symbol<br>TB2MR<br>Bit Symbol<br>TMOD0                               | 039D16                                                                                                                                                                   | 1 1 : fc32         After Reset         00XX00002         Function         Set to 002 (timer mode) for the three-                                                                                                                                                                                                                                                                                                                  | RW                                                       |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | Ster<br>Symbol<br>TB2MR<br>Bit Symbol<br>TMOD0<br>TMOD1                      | 039D16<br>Bit Name                                                                                                                                                       | 1 1 : fc32<br>After Reset<br>00XX00002<br>Function                                                                                                                                                                                                                                                                                                                                                                                | RW<br>RW<br>RW                                           |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | Ster<br>Symbol<br>TB2MR<br>Bit Symbol<br>TMOD0<br>TMOD1<br>MR0               | 039D16<br>Bit Name<br>Operation mode select bit<br>No effect for the three-pha                                                                                           | 1 1 : fc32         After Reset         00XX00002         Function         Set to 002 (timer mode) for the three-phase motor control timer function         ase motor control timer function.                                                                                                                                                                                                                                      | RW<br>RW<br>RW<br>RW                                     |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | Ster<br>Symbol<br>TB2MR<br>Bit Symbol<br>TMOD0<br>TMOD1                      | 039D16<br>Bit Name<br>Operation mode select bit<br>No effect for the three-pha                                                                                           | 1 1 : fc32         After Reset         00XX00002         Function         Set to 002 (timer mode) for the three-phase motor control timer function                                                                                                                                                                                                                                                                                | RW<br>RW<br>RW<br>RW                                     |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | Ster<br>Symbol<br>TB2MR<br>Bit Symbol<br>TMOD0<br>TMOD1<br>MR0               | 039D16<br>Bit Name<br>Operation mode select bit<br>No effect for the three-pha<br>If necessary, set to 0. Wh                                                             | 1 1 : fc32         After Reset         00XX00002         Function         Set to 002 (timer mode) for the three-phase motor control timer function         ase motor control timer function.                                                                                                                                                                                                                                      | RW<br>RW<br>RW<br>RW                                     |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | ster<br>Symbol<br>TB2MR<br>Bit Symbol<br>TMOD0<br>TMOD1<br>MR0<br>MR1        | 039D16<br>Bit Name<br>Operation mode select bit<br>No effect for the three-pha<br>If necessary, set to 0. Wh<br>Set to 0 for the three-phas                              | 1 1 : fc32         After Reset<br>00XX00002         Function         Set to 002 (timer mode) for the three-<br>phase motor control timer function         ase motor control timer function.         then read, the contents are undefined         e motor control timer function         e motor control timer function         e motor control timer function         e motor control timer function, write 0.         undefined | RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW<br>RW |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                | ster<br>Symbol<br>TB2MR<br>Bit Symbol<br>TMOD0<br>TMOD1<br>MR0<br>MR1<br>MR2 | 039D16<br>Bit Name<br>Operation mode select bit<br>No effect for the three-pha<br>If necessary, set to 0. Wh<br>Set to 0 for the three-phas<br>When write in three-phase | 1 1 : fc32         After Reset         00XX00002         Function         Set to 002 (timer mode) for the three-phase motor control timer function         ase motor control timer function.         ien read, the contents are undefined         e motor control timer function         e motor control timer function         e motor control timer function                                                                    | RW<br>RW<br>RW<br>RW<br>RW                               |

Figure 12.32 TA1MR, TA2MR, TA4MR, and TB2MR Registers

**Table 14.3** lists pin functions for the case where the multiple transfer clock output pin select function is deselected. **Table 14.4** lists the P64 pin functions during clock synchronous serial I/O mode. Note that for a period from when the UARTi operation mode is selected to when transfer starts, the TxDi pin outputs an "H". (If the N-channel open-drain output is selected, this pin is in a high-impedance state.)

| Table 14.3 Pin Functions | When Not Select Multiple Transfer | Clock Output Pin Function) <sup>(1)</sup> |

|--------------------------|-----------------------------------|-------------------------------------------|

|                          |                                   | ••••••••••••••••••••••••••••••••••••••    |

| Pin Name                             | Function              | Method of Selection                                                                                                                                                                                  |

|--------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxDi (i = 0 to 2)<br>(P63, P67, P70) | Serial data output    | (Outputs dummy data when performing reception only)                                                                                                                                                  |

| RxDi<br>(P62, P66, P71)              | Serial data input     | Set the PD6_2 bit and PD6_6 bit in the PD6 register, and PD7_1 bit in the PD7 register to 0 (Can be used as an input port when performing transmission only)                                         |

| CLKi                                 | Transfer clock output | Set the CKDIR bit in the UiMR register to 0                                                                                                                                                          |

| (P61, P65, P72)                      | Transfer clock input  | Set the CKDIR bit in the UiMR register to 1<br>Set the PD6_1 bit and PD6_5 bit in the PD6 register, and the PD7_2 bit in the<br>PD7 register to 0                                                    |

| CTSi/RTSi<br>(P60, P64, P73)         | CTS input             | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 0<br>Set the PD6_0 bit and PD6_4 bit in the PD6 register is set to 0, the PD7_3 bit<br>in the PD7 register to 0 |

|                                      | RTS output            | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 1                                                                                                               |

|                                      | I/O port              | Set the CRD bit in the UiC0 register to 1                                                                                                                                                            |

NOTE:

1: When the U1MAP bit in PACR register is 1 (P73 to P70), UART1 pin is assgined to P73 to P70.

#### Table 14.4 P64 Pin Functions<sup>(1)</sup>

|                      |      |          | Bit Se | et Value         |        |                     |

|----------------------|------|----------|--------|------------------|--------|---------------------|

| Pin Function         | U1C0 | register | U      | ICON registe     | er     | PD6 register        |

|                      | CRD  | CRS      | RCSP   | CLKMD1           | CLKMD0 | PD6_4               |

| P64                  | 1    | —        | 0      | 0                | —      | Input: 0, Output: 1 |

| CTS1                 | 0    | 0        | 0      | 0                |        | 0                   |

| RTS1                 | 0    | 1        | 0      | 0                |        | —                   |

| CTS <sub>0</sub> (2) | 0    | 0        | 1      | 0                |        | 0                   |

| CLKS1                | —    |          |        | 1 <sup>(3)</sup> | 1      | —                   |

NOTES:

1. When the U1MAP bit in PACR register is 1 (P73 to P70), this table lists the P70 functions.

In addition to this, set the CRD bit in the U0C0 register to 0 (CT00/RT00 enabled) and the CRS bit in the U0C0 register to 1 (RTS0 selected).

3. When the CLKMD1 bit is set to 1 and the CLKMD0 bit is set to 0, the following logic levels are output: • High if the CLKPOL bit in the U1C0 register is set to 0

• Low if the CLKPOL bit in the U1C0 register is set to 1

## 14.1.1.1 Counter Measure for Communication Error Occurs

If a communication error occurs while transmitting or receiving in clock synchronous serial I/O mode, follow the procedures below.

•Resetting the UiRB register (i=0 to 2)

- (1) Set the RE bit in the UiC1 register to 0 (reception disabled)

- (2) Set bits SMD2 to SMD0 in the UiMR register to 0002 (Serial I/O disabled)

- (3) Set bits SMD2 to SMD0 in the UiMR register to 0012 (Clock synchronous serial I/O mode)

- (4) Set the RE bit in the UiC1 register to 1 (reception enabled)

•Resetting the UiTB register (i=0 to 2)

- (1) Set bits SMD2 to SMD0 in the UiMR register to 0002 (Serial I/O disabled)

- (2) Set bits SMD2 to SMD0 in the UiMR register to 0012 (Clock synchronous serial I/O mode)

- (3) 1 is written to TE bit in the UiC1 register (reception enabled), regardless to the TE bit.

**Table 14.7** lists the functions of the input/output pins in UART mode. **Table 14.8** lists the P64 pin functions during UART mode. Note that for a period from when the UARTi operation mode is selected to when transfer starts, the TxDi pin outputs an "H". (If the N-channel open-drain output is selected, this pin is in a high-impedance state.)

| Pin Name                             | Function             | Method of Selection                                                                                                                                                                        |

|--------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxDi (i = 0 to 2)<br>(P63, P67, P70) | Serial data output   | (Outputs "H" when performing reception only)                                                                                                                                               |

| RxDi<br>(P62, P66, P71)              | Serial data input    | PD6_2 bit, PD6_6 bit in the PD6 register and the PD7_1 bit in the PD7 register (Can be used as an input port when performing transmission only)                                            |

| CLKi                                 | Input/output port    | Set the CKDIR bit in the UiMR register to 0                                                                                                                                                |

| (P61, P65, P72)                      | Transfer clock input | Set the CKDIR bit in the UiMR register to 1<br>Set the PD6_1 bit and PD6_5 bit in the PD6 register to 0, PD7_2 bit in the PD7<br>register to 0                                             |

| CTSi/RTSi<br>(P60, P64, P73)         | CTS input            | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 0<br>Set the PD6_0 bit and PD6_4 bit in the PD6 register to 0, the PD7_3 bit in the<br>PD7 register 0 |

|                                      | RTS output           | Set the CRD bit in the UiC0 register to 0<br>Set the CRS bit in the UiC0 register to 1                                                                                                     |

|                                      | Input/output port    | Set the CRD bit in the UiC0 register 1                                                                                                                                                     |

#### Table 14.7 I/O Pin Functions in UART mode<sup>(1)</sup>

NOTE:

1. When the U1MAP bit in PACR register is set to 1 (P73 to P70), UART1 pin is assgined to P73 to P70.

|                                 |      |          | Bit Se | et Value |                     |

|---------------------------------|------|----------|--------|----------|---------------------|

| Pin Function                    | U1C0 | register | UCON   | register | PD6 register        |

|                                 | CRD  | CRS      | RCSP   | CLKMD1   | PD6_4               |

| P64                             | 1    |          | 0      | 0        | Input: 0, Output: 1 |

| CTS1                            | 0    | 0        | 0      | 0        | 0                   |

| RTS1                            | 0    | 1        | 0      | 0        |                     |

| CTS <sub>0</sub> <sup>(2)</sup> | 0    | 0        | 1      | 0        | 0                   |

#### Table 14.8 P64 Pin Functions in UART mode <sup>(1)</sup>

NOTES:

1. When the U1MAP bit in PACR register is 1 (P73 to P70), this table lists the P70 functions.

2. In addition to this, set the CRD bit in the U0C0 register to 0 (CTS0/RTS0 enabled) and the CRS bit in the U0C0 register to 1 (RTS0 selected).

### 14.1.2.2 Counter Measure for Communication Error

If a communication error occurs while transmitting or receiving in UART mode, follow the procedure below.

- Resetting the UiRB register (i=0 to 2)

- (1) Set the RE bit in the UiC1 register to 0 (reception disabled)

- (2) Set the RE bit in the UiC1 register to 1 (reception enabled)

- Resetting the UiTB register (i=0 to 2)

- (1) Set bits SMD2 to SMD0 in UiMR register 0002 (Serial I/O disabled)

- (2) Set bits SMD2 to SMD0 in UiMR register 0012, 1012, 1102

- (3) 1 is written to TE bit in the UiC1 register (reception enabled), regardless of the TE bit

# 14.1.2.3 LSB First/MSB First Select Function

As shown in **Figure 14.18**, use the UFORM bit in the UiC0 register to select the transfer format. This function is valid when transfer data is 8 bits long.

| CLKi                                                          |                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxDi                                                          | ST ( D0 ) D1 ) D2 ) D3 ) D4 ) D5 ) D6 ) D7 ) P ) SP                                                                                                                                                                                                                                                                                               |

| RXDi                                                          | ST / D0 / D1 / D2 / D3 / D4 / D5 / D6 / D7 / P / SP                                                                                                                                                                                                                                                                                               |

| (2) When the                                                  | e UFORM bit in the UiC0 register is set to 1 (MSB first)                                                                                                                                                                                                                                                                                          |

| CLKi                                                          |                                                                                                                                                                                                                                                                                                                                                   |

| TXDi                                                          | ST / D7 / D6 / D5 / D4 / D3 / D2 / D1 / D0 / P / SP                                                                                                                                                                                                                                                                                               |

| RXDi                                                          | ST ( D7 ) D6 ) D5 ) D4 ) D3 ) D2 ) D1 ) D0 ) P ) SP                                                                                                                                                                                                                                                                                               |

| ST : Start bit<br>P : Parity bit<br>SP : Stop bit<br>= 0 to 2 |                                                                                                                                                                                                                                                                                                                                                   |

| edge and to<br>to 0 (no rev                                   | s to the case where the CKPOL bit in the UiC0 register is set to 0 (transmit data output at the falling he receive data taken in at the rising edge of the transfer clock), the UiLCH bit in the UiC1 register is set verse), the STPS bit in the UiMR register is set to 0 (1 stop bit) and the PRYE bit in the UiMR register is arity enabled). |

Figure 14.18 Transfer Format

# 14.1.4 Special Mode 2 (UART2)

Multiple slaves can be serially communicated from one master. Transfer clock polarity and phase are selectable. **Table 14.15** lists the specifications of Special Mode 2. **Table 14.16** lists the registers used in Special Mode 2 and the register values set. **Figure 14.26** shows communication control example for Special Mode 2.

| Item                         | Specification                                                                                 |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Transfer data format         | Transfer data length: 8 bits                                                                  |  |  |  |  |

| Transfer clock               | Master mode                                                                                   |  |  |  |  |

|                              | the CKDIR bit in the U2MR register is set to 0 (internal clock) : fj/ (2(n+1))                |  |  |  |  |

|                              | fj = f1sio, f2sio, f8sio, f32sio. n: Setting value in the U2BRG register 0016 to FF16         |  |  |  |  |

|                              | Slave mode                                                                                    |  |  |  |  |

|                              | CKDIR bit is set to 1 (external clock selected) : Input from CLK2 pin                         |  |  |  |  |

| Transmit/receive control     | Controlled by input/output ports                                                              |  |  |  |  |

| Transmission start condition | Before transmission can start, the following requirements must be met <sup>(1)</sup>          |  |  |  |  |

|                              | <ul> <li>The TE bit in the U2C1 register is set to 1 (transmission enabled)</li> </ul>        |  |  |  |  |

|                              | - The TI bit in the U2C1 register is set to 0 (data present in U2TB register)                 |  |  |  |  |

| Reception start condition    | Before reception can start, the following requirements must be met (1)                        |  |  |  |  |

|                              | <ul> <li>The RE bit in the U2C1 register is set to 1 (reception enabled)</li> </ul>           |  |  |  |  |

|                              | <ul> <li>The TE bit in the U2C1 register is set to 1 (transmission enabled)</li> </ul>        |  |  |  |  |

|                              | – The TI bit in the U2C1 register is set to 0 (data present in the U2TB register)             |  |  |  |  |

| Interrupt request            | For transmission, one of the following conditions can be selected                             |  |  |  |  |

| generation timing            | – The U2IRS bit in the U2C1 register is set to 0 (transmit buffer empty): when trans          |  |  |  |  |

|                              | ferring data from the U2TB register to the UART2 transmit register (at start of transmission) |  |  |  |  |

|                              | – The U2IRS bit is set to 1 (transfer completed): when the serial I/O finished sending        |  |  |  |  |

|                              | data from the UART2 transmit register                                                         |  |  |  |  |

|                              | For reception                                                                                 |  |  |  |  |

|                              | When transferring data from the UART2 receive register to the U2RB register (at               |  |  |  |  |

|                              | completion of reception)                                                                      |  |  |  |  |

| Error detection              | • Overrun error <sup>(2)</sup>                                                                |  |  |  |  |

|                              | This error occurs if the serial I/O started receiving the next data before reading the        |  |  |  |  |

|                              | U2RB register and received the 7th bit in the the next data                                   |  |  |  |  |

| Select function              | Clock phase setting                                                                           |  |  |  |  |

|                              | Selectable from four combinations of transfer clock polarities and phases                     |  |  |  |  |

Table 14.15 Special Mode 2 Specifications

NOTES:

- 1. When an external clock is selected, the conditions must be met while if the CKPOL bit in the U2C0 register is set to 0 (transmit data output at the falling edge and the receive data taken in at the rising edge of the transfer clock), the external clock is in the high state; if the CKPOL bit in the U2C0 register is set to 1 (transmit data output at the rising edge and the receive data taken in at the falling edge of the transfer clock), the external clock is in the low state.

- 2. If an overrun error occurs, bits 8 to 0 in the U2RB register are undefined. The IR bit in the S2RIC register remains unchanged.

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Symbol<br>ADTRG | Address<br>CON 03D216                                   | After Reset<br>0016                                         |    |

|-------------------------------------------------------|-----------------|---------------------------------------------------------|-------------------------------------------------------------|----|

|                                                       | Bit Symbol      | Bit Name                                                | Function                                                    | RW |

|                                                       | SSE             | A/D operation mode select bit 2                         | Simultaneous sample sweep mode or delayed trigger mode 0, 1 | RW |

|                                                       | DTE             | A/D operation mode select bit 3                         | Delayed trigger mode 0, 1                                   | RW |

|                                                       | HPTRG0          | AN0 trigger select bit                                  | See Table 15.11                                             | RW |

| · · · · · · · · · · · · · · · · · · ·                 | HPTRG1          | AN1 trigger select bit                                  | See Table 15.11                                             | RW |

| <u></u>                                               | (b7-b4)         | Nothing is assigned. If nec When read, the content is ( |                                                             | -  |

Figure 15.23 ADTRGCON Register in Delayed Trigger Mode 0

#### Table 15.11 Trigger Select Bit Setting in Delayed Trigger Mode 0

| TRG | TRG1 | HPTRG0 | HPTRG1 | Trigger                |