# E. Renesas Electronics America Inc - M30281FATHP#U3AAE8 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                   |

| Core Size                  | -                                                                                   |

| Speed                      | -                                                                                   |

| Connectivity               | -                                                                                   |

| Peripherals                | -                                                                                   |

| Number of I/O              | -                                                                                   |

| Program Memory Size        | -                                                                                   |

| Program Memory Type        | -                                                                                   |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | -                                                                                   |

| Voltage - Supply (Vcc/Vdd) | -                                                                                   |

| Data Converters            | -                                                                                   |

| Oscillator Type            | -                                                                                   |

| Operating Temperature      | -                                                                                   |

| Mounting Type              | -                                                                                   |

| Package / Case             | -                                                                                   |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30281fathp-u3aae8 |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

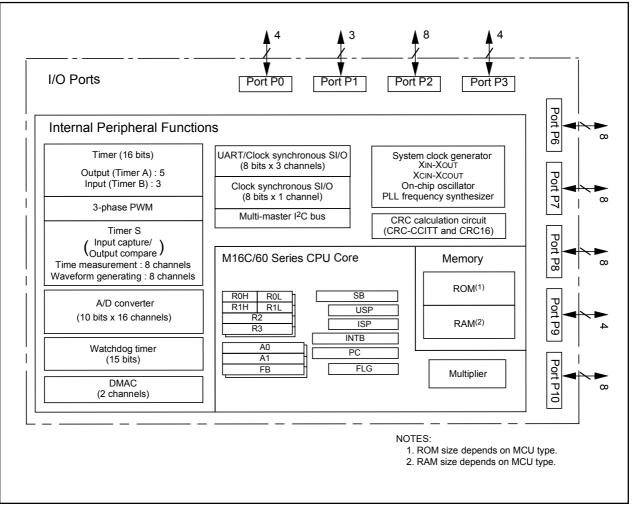

#### Figure 1.2 is a block diagram of the M16C/28 Group (T-ver./V-ver.), 64-pin package.

Figure 1.2 M16C/28 Group (T-ver./V-ver.), 64-Pin Package Block Diagram

# 7. Clock Generation Circuits

The MCU has four clock generation circuits as follows:

- (1) Main clock oscillation circuit

- (2) Sub clock oscillation circuit

- (3) On-chip oscillator

- (4) PLL frequency synthesizer

Table 7.1 lists the specifications of the clock generation circuit. Figure 7.1 shows the clock generation circuits. Figures 7.2 to 7.7 show the clock-associated registers.

| Item                               | Main Clock<br>Oscillation Circuti                                  | Sub Clock<br>Oscillation Circuit                     | Variable On-chip Oscillator                                                                                                                                                     | PLL Frequency<br>Synthesizer                                                   |

|------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Use of clock                       | - CPU clock source<br>- Peripheral function<br>clock source        | - CPU clock source<br>- Timer A, B's clock<br>source | <ul> <li>CPU clock source</li> <li>Peripheral function clock source</li> <li>CPU and peripheral function<br/>clock sources when the main<br/>clock stops oscillating</li> </ul> | <ul> <li>CPU clock source</li> <li>Peripheral function clock source</li> </ul> |

| Clock frequency                    | 0 to 20 MHz                                                        | 32.768 kHz                                           | Selectable source frequency:<br>f1(ROC), f2(ROC), f3(ROC)<br>Selectable divider:<br>by 2, by 4, by 8                                                                            | 10 to 20 MHz                                                                   |

| Usable oscillator                  | <ul> <li>Ceramic oscillator</li> <li>Crystal oscillator</li> </ul> | - Crystal oscillator                                 |                                                                                                                                                                                 |                                                                                |

| Pins to connect oscillator         | Xin, Xout                                                          | XCIN, XCOUT                                          |                                                                                                                                                                                 |                                                                                |

| Oscillation stop, restart function | Available                                                          | Available                                            | Available                                                                                                                                                                       | Available                                                                      |

| Oscillator status after reset      | Oscillating                                                        | Stopped                                              | Oscillating<br>(CPU clock source)                                                                                                                                               | Stopped                                                                        |

| Other                              | Externally derived clock can be input                              |                                                      |                                                                                                                                                                                 |                                                                                |

**Table 7.1 Clock Generation Circuit Specifications**

#### 7.8.1 Operation When CM27 bit = 0 (Oscillation Stop Detection Reset)

When main clock stop is detected when the CM20 bit is 1 (oscillation stop, re-oscillation detection function enabled), the MCU is initialized, coming to a halt (oscillation stop reset; refer to "SFR", "Reset"). This status is reset with hardware reset 1. Also, even when re-oscillation is detected, the MCU can be initialized and stopped; it is, however, necessary to avoid such usage. (During main clock stop, do not set the CM20 bit to 1 and the CM27 bit to 0.)

#### 7.8.2 Operation When CM27 bit = 1 (Oscillation Stop and Re-oscillation Detect Interrupt)

When the main clock corresponds to the CPU clock source and the CM20 bit is 1 (oscillation stop and reoscillation detect function enabled), the system is placed in the following state if the main clock comes to a halt:

- Oscillation stop and re-oscillation detect interrupt request occurs.

- The on-chip oscillator starts oscillation, and the on-chip oscillator clock becomes the CPU clock and clock

source for peripheral functions in place of the main clock.

- CM21 bit = 1 (on-chip oscillator clock for CPU clock source)

- CM22 bit = 1 (main clock stop detected)

- CM23 bit = 1 (main clock stopped)

When the PLL clock corresponds to the CPU clock source and the CM20 bit is 1, the system is placed in the following state if the main clock comes to a halt: Since the CM21 bit remains unchanged, set it to 1 (on-chip oscillator clock) inside the interrupt routine.

- Oscillation stop and re-oscillation detect interrupt request occurs.

- CM22 bit = 1 (main clock stop detected)

- CM23 bit = 1 (main clock stopped)

- CM21 bit remains unchanged

When the CM20 bit is 1, the system is placed in the following state if the main clock re-oscillates from the stop condition:

- Oscillation stop and re-oscillation detect interrupt request occurs.

- CM22 bit = 1 (main clock re-oscillation detected)

- CM23 bit = 0 (main clock oscillation)

- CM21 bit remains unchanged

#### 7.8.3 How to Use Oscillation Stop and Re-oscillation Detect Function

- The oscillation stop and re-oscillation detect interrupt shares the vector with the watchdog timer interrupt. If the oscillation stop, re-oscillation detection and watchdog timer interrupts both are used, read the CM22 bit in an interrupt routine to determine which interrupt source is requesting the interrupt.

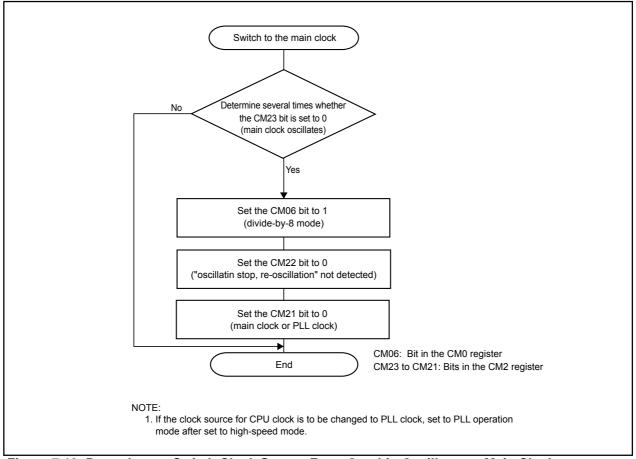

- Where the main clock re-oscillated after oscillation stop, return the main clock to the CPU clock and peripheral function clock source by program. **Figure 7.13** shows the procedure for switching the clock source from the on-chip oscillator to the main clock.

- Simultaneously with oscillation stop, re-oscillation detection interrupt occurrence, the CM22 bit becomes 1. When the CM22 bit is set at 1, oscillation stop, re-oscillation detection interrupt are disabled. By setting the CM22 bit to 0 by program, oscillation stop, re-oscillation detection interrupt are enabled.

- If the main clock stops during low speed mode where the CM20 bit is 1, an oscillation stop, re-oscillation

detection interrupt request is generated. At the same time, the on-chip oscillator starts oscillating. In

this case, although the CPU clock is derived from the sub clock as it was before the interrupt occurred,

the peripheral function clocks now are derived from the on-chip oscillator clock.

- To enter wait mode while using the oscillation stop, re-oscillation detection function, set the CM02 bit to 0 (peripheral function clocks not turned off during wait mode).

- Since the oscillation stop, re-oscillation detection function is provided in preparation for main clock stop due to external factors, set the CM20 bit to 0 (Oscillation stop, re-oscillation detection function disabled) where the main clock is stopped or oscillated by program, that is where the stop mode is selected or the CM05 bit is altered.

- This function cannot be used if the main clock frequency is 2 MHz or less. In that case, set the CM20 bit to 0.

Figure 7.13 Procedure to Switch Clock Source From On-chip Oscillator to Main Clock

RENESAS

# 9. Interrupts

Note

The SI/O4 interrupt of peripheral function interrupts is not available in the 64-pin package.

#### 9.1 Type of Interrupts

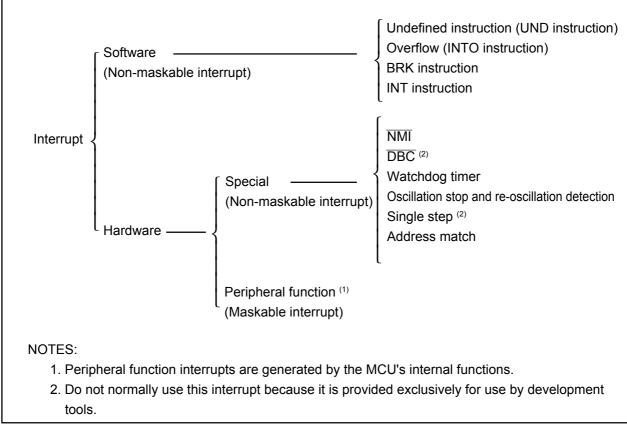

Figure 9.1 shows types of interrupts.

#### Figure 9.1 Interrupts

- Maskable Interrupt: An interrupt which can be enabled (disabled) by the interrupt enable flag (I flag) or

whose interrupt priority <u>can be changed</u> by priority level.

- Non-maskable Interrupt: An interrupt which cannot be enabled (disabled) by the interrupt enable flag (I flag) or whose interrupt priority <u>cannot be changed</u> by priority level.

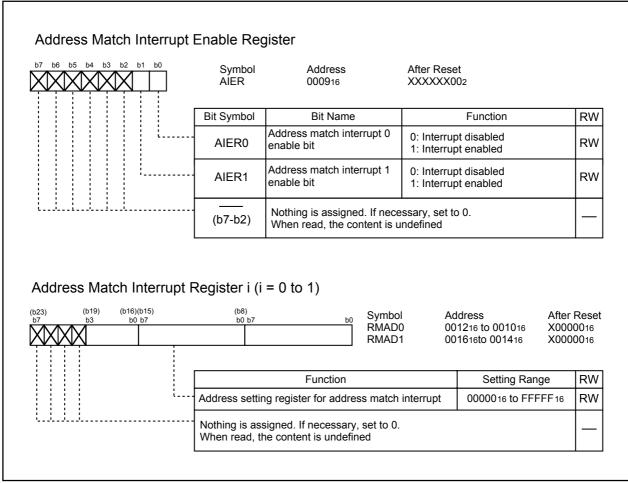

Figure 9.13 AIER Register, RMAD0 and RMAD1 Registers

### **11.1 Transfer Cycles**

The transfer cycle consists of a memory or SFR read (source read) bus cycle and a write (destination write) bus cycle. The number of read and write bus cycles is affected by the source and destination addresses of transfer. Furthermore, the bus cycle itself is extended by a software wait.

#### 11.1.1 Effect of Source and Destination Addresses

If the transfer unit is 16 bits and the source address of transfer begins with an odd address, the source read cycle consists of one more bus cycle than when the source address of transfer begins with an even address.

Similarly, if the transfer unit is 16 bits and the destination address of transfer begins with an odd address, the destination write cycle consists of one more bus cycle than when the destination address of transfer begins with an even address.

#### 11.1.2 Effect of Software Wait

For memory or SFR accesses in which one or more software wait states are inserted, the number of bus cycles required for that access increases by an amount equal to software wait states.

**Figure 11.5** shows the example of the cycles for a source read. For convenience, the destination write cycle is shown as one cycle and the source read cycles for the different conditions are shown. In reality, the destination write cycle is subject to the same conditions as the source read cycle, with the transfer cycle changing accordingly. When calculating transfer cycles, take into consideration each condition for the source read and the destination write cycle, respectively. For example, when data is transferred in 16 bit units and when both the source address and destination address are an odd address ((2) in **Figure 11.5**), two source read bus cycles and two destination write bus cycles are required.

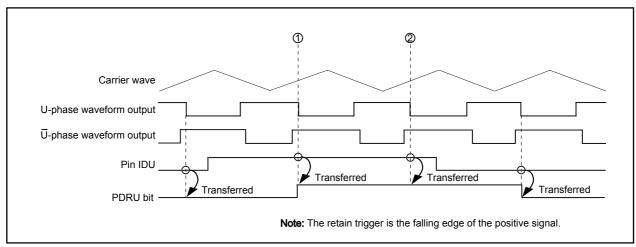

| b6 b5 b4 b3 b2 b1 b0 | Symbol<br>INVC0 | Address<br>034816                                                | After Reset<br>0016                                                                                                                                                                                                               |    |

|----------------------|-----------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                      | Bit Symbol      | Bit Name                                                         | Function                                                                                                                                                                                                                          | RW |

|                      | INV00           | Effective interrupt output<br>polarity select bit <sup>(3)</sup> | <ul> <li>0: ICTB2 counter is incremented by 1 on<br/>the rising edge of timer A1 reload control<br/>signal</li> <li>1: ICTB2 counter is incremented by 1 on<br/>the falling edge of timer A1 reload control<br/>signal</li> </ul> | RW |

|                      | INV01           | Effective interrupt output specification bit <sup>(2, 3)</sup>   | 0: ICTB2 counter incremented by 1 at a<br>timer B2 underflow<br>1: Selected by INV00 bit                                                                                                                                          | RW |

|                      | INV02           | Mode select bit <sup>(4)</sup>                                   | 0: Three-phase motor control timer<br>function unused<br>1: Three-phase motor control timer<br>function (5)                                                                                                                       | RW |

|                      | INV03           | Output control bit <sup>(6)</sup>                                | 0: Three-phase motor control timer output<br>disabled (5)<br>1: Three-phase motor control timer output<br>enabled                                                                                                                 | RW |

|                      | INV04           | Positive and negative<br>phases concurrent output<br>disable bit | 0: Simultaneous active output enabled<br>1: Simultaneous active output disabled                                                                                                                                                   | RW |

|                      | INV05           | Positive and negative<br>phases concurrent output<br>detect flag | 0: Not detected yet<br>1: Already detected <sup>(7)</sup>                                                                                                                                                                         | RW |

|                      | INV06           | Modulation mode select bit <sup>(8)</sup>                        | 0: Triangular wave modulation mode<br>1: Sawtooth wave modulation mode <sup>(9)</sup>                                                                                                                                             | RW |

|                      | INV07           | Software trigger select bit                                      | Setting this bit to 1 generates a transfer<br>trigger. If the INV06 bit is 1, a trigger for the<br>dead time timer is also generated. The<br>value of this bit when read is 0                                                     | RW |

NOTES:

1. Write to this register after setting the PRC1 bit in the PRCR register to 1 (write enable). Note also that bits INV00 to INV02, bits INV04 and INV06 can only be rewritten when timers A1, A2, A4 and B2 are idle.

2. If this bit needs to be set to 1, set any value in the ICTB2 register before writing to it.

3. Effective when the INV11 bit in the INV1 register is 1 (three-phase mode 1). If INV11 is set to 0 (three-phase mode 0), the ICTB2 counter is incremented by 1 each time the timer B2 underflows, regardless of whether the INV00 and INV01 bits are set. When setting the INV01 bit to 1, the first interrupt is generated when the timer B2 underflows n-1 times, if n is the value set in the ICTB2 counter. Subsequent interrupts are generated every n times the timer B2 underflow.

4. Setting the INV02 bit to 1 activates the dead time timer, U/V/W-phase output control circuits and ICTB2 counter.

5. When the INV02 bit is set to 1 and the INV03 bit is set to 0, 0, U, ∇, V, ₩, W pins, including pins shared with other output functions, enter a high-impedance state. When INV03 is set to 1, U/V/W corresponding pins generate the three-phase PWM output.

6. The INV03 bit is set to 0 in the following cases:

When reset

• When positive and negative go active (INV05 = 1) simultaneously while INV04 bit is 1

• When set to 0 by program

• When input on the  $\overline{\text{SD}}$  pin changes state from "H" to "L" regardless of the value of the INVCR1 bit. (The INV03 bit cannot be set to 1 when  $\overline{\text{SD}}$  input is "L".) INV03 is set to 0 when both bits INV05 and INV04 are set to 1.

| Item                                                                                               | INV06=0                                                                                               | INV06=1                                                                                                |  |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Mode                                                                                               | Triangular wave modulation mode                                                                       | Sawtooth wave modulation mode                                                                          |  |

| Timing at which transferred from registers<br>IDB0 to IDB1 to three-phase output shift<br>register | Transferred only once synchronously with the transfer trigger after writing to registers IDB0 to IDB1 | Transferred every transfer trigger                                                                     |  |

| Timing at which dead time timer trigger is generated when INV16 bit is 0                           | Synchronous with the falling edge of timer A1, A2, or A4 one-shot pulse                               | Synchronous with the transfer<br>trigger and the falling edge of timer<br>A1, A2, or A4 one-shot pulse |  |

| INV13 bit                                                                                          | Effective when INV11 is set to 1 and INV06 is set to 0                                                | No effect                                                                                              |  |

Transfer trigger: Timer B2 underflow, write to the INV07 bit or write to the TB2 register when the INV10 bit is set to 1.

9: If the INV06 bit is set to 1, set the INV11 bit to 0 (three-phase mode 0) and set the PWCON bit to 0 (timer B2 reloaded by a timer B2 underflow)

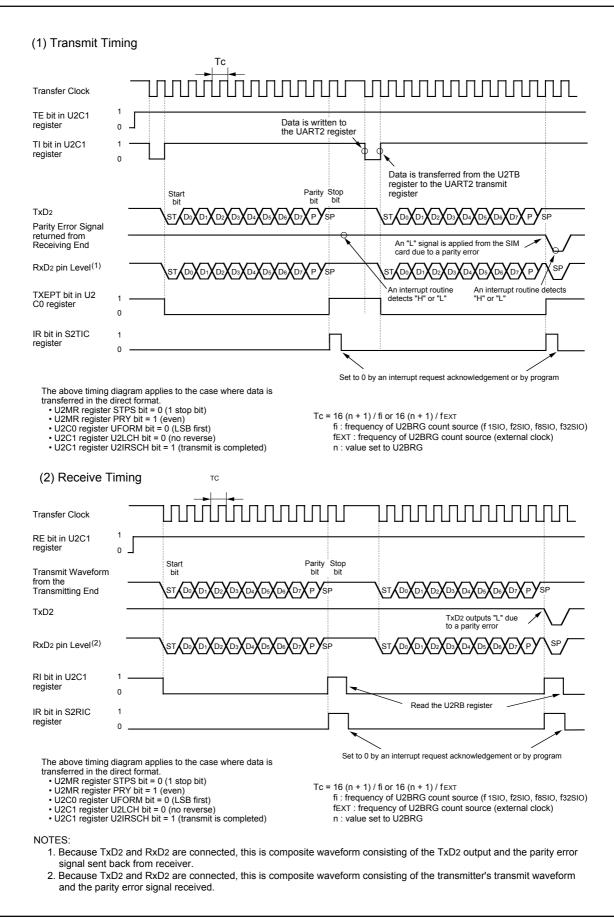

10. When the PFCi (i = 0 to 5) bit in the PFCR register is set to 1 (three-phase PWM output), individual pins are enabled to output.

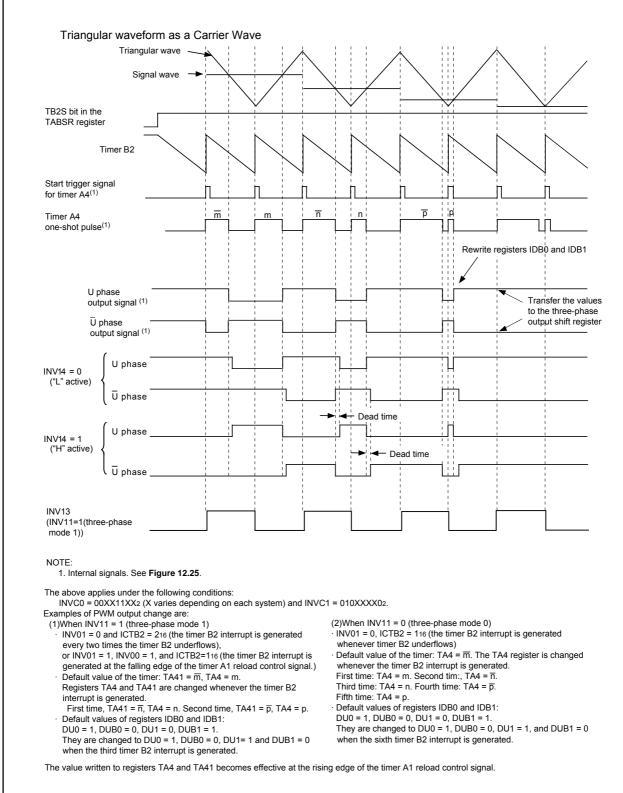

#### Figure 12.26 INVC0 Register

The three-phase motor control timer function is enabled by setting the INV02 bit in the INVC0 register to 1. When this function is on, timer B2 is used to control the carrier wave, and timers A4, A1 and A2 are used to control three-phase PWM outputs (U,  $\overline{U}$ , V,  $\overline{V}$ , W and  $\overline{W}$ ). The dead time is controlled by a dedicated dead-time timer. **Figure 12.33** shows the example of triangular modulation waveform, and **Figure 12.34** shows the example of sawtooth modulation waveform.

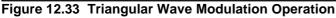

#### 12.3.1 Position-Data-Retain Function

This function is used to retain the position data synchronously with the three-phase waveform output. There are three position-data input pins for U, V, and W phases.

A trigger to retain the position data (hereafter, this trigger is referred to as "retain trigger") can be selected by the PDRT bit in the PDRF register. This bit selects the retain trigger to be the falling edge of each positive phase, or the rising edge of each positive phase.

#### 12.3.1.1 Operation of the Position-data-retain Function

**Figure 12.35** shows a usage example of the position-data-retain function (U phase) when the retain trigger is selected as the falling edge of the positive signal.

- (1) At the falling edge of the U-phase waveform ouput, the state at pin IDU is transferred to the PDRU bit in the PDRF register.

- (2) Until the next falling edge of the Uphase waveform output, the above value is retained.

Figure 12.35 Usage Example of Position-data-retain Function (U phase )

| b7 b6 b5 b4 b3 b2 b1 b | 0 Symbol<br>PFCR | Addres<br>035816                       |                                                                                       |    |

|------------------------|------------------|----------------------------------------|---------------------------------------------------------------------------------------|----|

|                        | Bit Symbol       | Bit Name                               | Function                                                                              | RW |

|                        | PFC0             | Port P8₀ output function select bit    | 0: Input/Output port P8₀<br>1: Three-phase PWM output<br>(U phase output)             | RW |

|                        | PFC1             | Port P81 output function select bit    | 0: Input/Output port P81<br>1: Three-phase PWM output<br>(Ū phase output)             | RW |

|                        | ··· PFC2         | Port P72 output function select bit    | 0: Input/Output port P72<br>1: Three-phase PWM output<br>(V phase output)             | RW |

|                        | PFC3             | Port P7₃ output<br>function select bit | 0: Input/Output port P7 <sub>3</sub><br>1: Three-phase PWM output<br>(V phase output) | RW |

|                        | PFC4             | Port P74 output function select bit    | 0: Input/Output port P74<br>1: Three-phase PWM output<br>(W phase output)             | RW |

|                        | PFC5             | Port P7₅ output<br>function select bit | 0: Input/Output port P7₅<br>1: Three-phase PWM output<br>(₩ phase output)             | RW |

| (b7-b6)                |                  | Nothing is assigne these contents are  | d. When write, set to 0. When read,<br>0                                              |    |

timer.

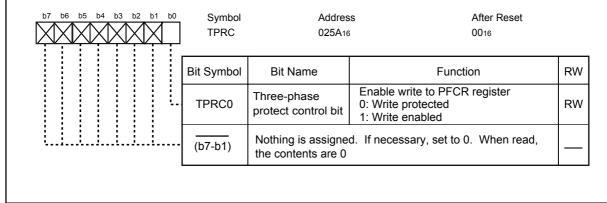

### Three-phase Protect Control Register

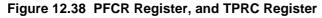

Figure 13.9 G1IR Register

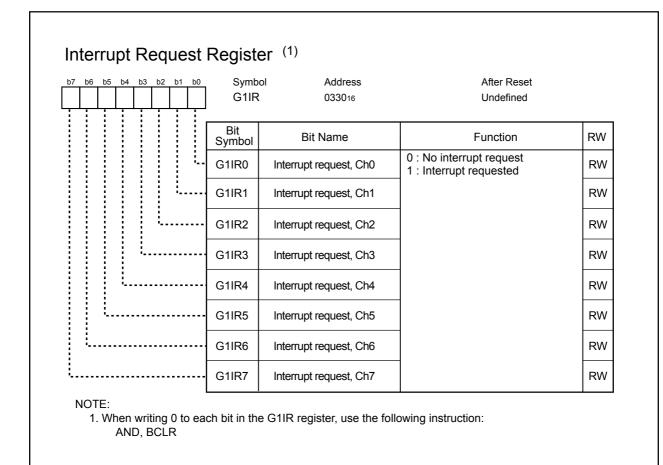

Figure 14.2 Block diagram of UARTi (i = 0, 1) transmit/receive unit

#### Table 14.13 I<sup>2</sup>C bus Mode Functions

|                                                                                            | Clock                                                                                                               | I <sup>2</sup> C bus mode (SMD2 to SMD0 €⊉)1ICM = 1)                                    |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| Function                                                                                   | synchronous                                                                                                         | IICM2 = 0                                                                               |                                | IICM2 = 1                                                                                                                                                                                                                                              |                                                                                                                                     |  |

| FUNCTION                                                                                   | serial I/O mode<br>(SMD2 to SMD0 =                                                                                  | (NACK/ACK interrupt)                                                                    |                                | (UART transmit/ receive interrupt)                                                                                                                                                                                                                     |                                                                                                                                     |  |

|                                                                                            | 0012, IICM = 0)                                                                                                     | CKPH = 0<br>(no clock delay)                                                            | CKPH = 1<br>(clock delay)      | CKPH = 0<br>(no clock delay)                                                                                                                                                                                                                           | CKPH = 1<br>(clock delay)                                                                                                           |  |

| Interrupt source<br>for number 10 <sup>(1)</sup><br>(See <b>Fig.14.23</b> )                | -                                                                                                                   |                                                                                         |                                | ndition detection (Refer to <b>Table 14.14</b> )                                                                                                                                                                                                       |                                                                                                                                     |  |

| Interrupt source<br>for number 15 <sup>(1)</sup><br>(See <b>Fig.14.23</b> )                | UART2 transmit<br>operation - transmit<br>operation is started<br>or completed<br>(selected by U2IRS                | (NACK) - at the rising edge of 9th bit of SCL2                                          |                                | UART2 transmit<br>operation - at the<br>rising edge of 9th bit<br>of SCL2                                                                                                                                                                              | UART2 transmit<br>operation - at the<br>next falling edge<br>after the 9th bit of<br>SCL2                                           |  |

| Interrupt source<br>for number 16 <sup>(1)</sup><br>(See <b>Fig.14.23</b> )                | UART2 receive<br>timing - when 8th bit<br>is received,<br>CKPOL = 0<br>(rising edge)<br>CKPOL = 1<br>(falling edge) | Acknowledgment detection (ACK) -<br>at the rising edge of 9th bit of SCL2               |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Data transfer<br>timing from the<br>UART receive<br>shift register to<br>the U2RB register | CKPOL = 0<br>(rising edge)<br>CKPOL = 1<br>(falling edge)                                                           | At the rising edge                                                                      | e of 9th bit of SCL2           | Falling edge of 9th bit<br>of SCL2                                                                                                                                                                                                                     | Falling edge and rising edge<br>of 9th bit of SCL2                                                                                  |  |

| UART2 transmit<br>output delay                                                             | No delay                                                                                                            | Delay                                                                                   |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Function of P70                                                                            | TxD2 output                                                                                                         | SDA2 input and output                                                                   |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Function of P71                                                                            | RxD2 input                                                                                                          | SCL2 input and output                                                                   |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Function of P72                                                                            | Select CLK2 input<br>or output                                                                                      | - (Not used in I <sup>2</sup> C bus mode)                                               |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Noise filter width                                                                         | 15ns                                                                                                                | 200n                                                                                    |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Reading RxD2,<br>SCL2 pin levels                                                           | Can be read if the corresponding port direction bit is set to 0                                                     | Can be read regardless of the corresponding port direction bit                          |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| Default value of<br>TxD2, SDA2<br>output                                                   | CKPOL = 0 (H)<br>CKPOL = 1 (L)                                                                                      | Value set in the port register before entering I <sup>2</sup> C bus mode <sup>(1)</sup> |                                |                                                                                                                                                                                                                                                        |                                                                                                                                     |  |

| SCL2 default and<br>end values                                                             | -                                                                                                                   | Acknowledgment detection (ACK)                                                          |                                | UART2 receive operation - at the falling edge of 9th bit of SCL2                                                                                                                                                                                       |                                                                                                                                     |  |

| DMA1 source<br>(See <b>Fig.14.23</b> )                                                     | UART2 receive<br>operation                                                                                          | Н                                                                                       | L                              | Н                                                                                                                                                                                                                                                      | L                                                                                                                                   |  |

| Storing receive<br>data                                                                    | 1st to 8th bits are<br>stored into bits 7 to<br>0 in the U2RB<br>register                                           | 1st to 8th bits are<br>to 0 in the U2RB                                                 | stored into bits 7<br>register | 1st to 7th bits are stored into the bit 6 to bit 0 in         the U2RB register, with 8th bit stored in the bit 8 in         the U2RB register         1st to 8th bits are stored         into bits 7 to 0 in the U2RB         register <sup>(3)</sup> |                                                                                                                                     |  |

| Reading receive<br>data                                                                    | The U2RB register stat                                                                                              | tus is read                                                                             |                                |                                                                                                                                                                                                                                                        | Bit 6 to bit 0 in the U2RB<br>register are read as bit 7 to<br>bit 1. Bit 8 in the U2RB<br>register is read as bit 0 <sup>(4)</sup> |  |

NOTES:

- 1. If the interrupt source is changed, the IR bit in the interrupt control register for the changed interrupt may be set to 1 (interrupt requested). (Refer to "Interrupts" in Precautions.) If any of the following bits are changed, the interrupt source, the interrupt timing, etc. will be changed also. Therefore, set the IR bit to 0 (interrupt not requested) after those bits are changed.

- Bits SMD2 to SMD0 in the U2MR register, the IICM bit in the U2SMR register,

- the IICM2 bit in the U2SMR2 register, the CKPH bit in the U2SMR3 register

- 2. Set the default value of the SDA2 output when bits SMD2 to SMD0 in the U2MR register are set to 0002 (serial I/O disabled).

- 3. Second data transfer to the U2RB register (at the rising edge of the ninth bit of SCL2)

- 4. First data transfer to the U2RB register (at falling edge of the ninth bit of SCL2)

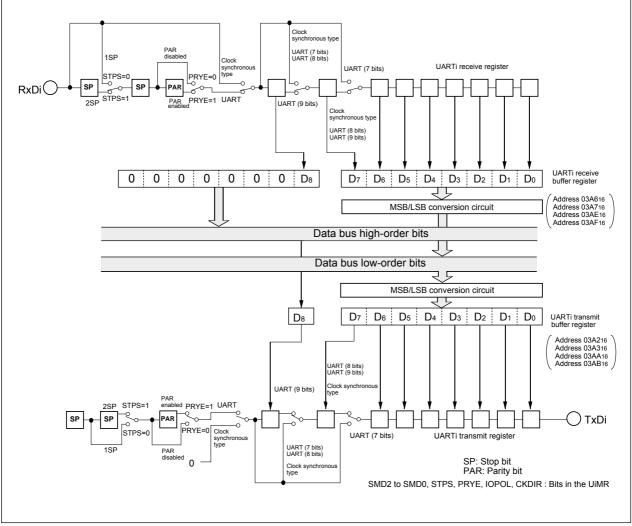

Figure 14.31 Transmit and Receive Timing in SIM Mode

RENESAS

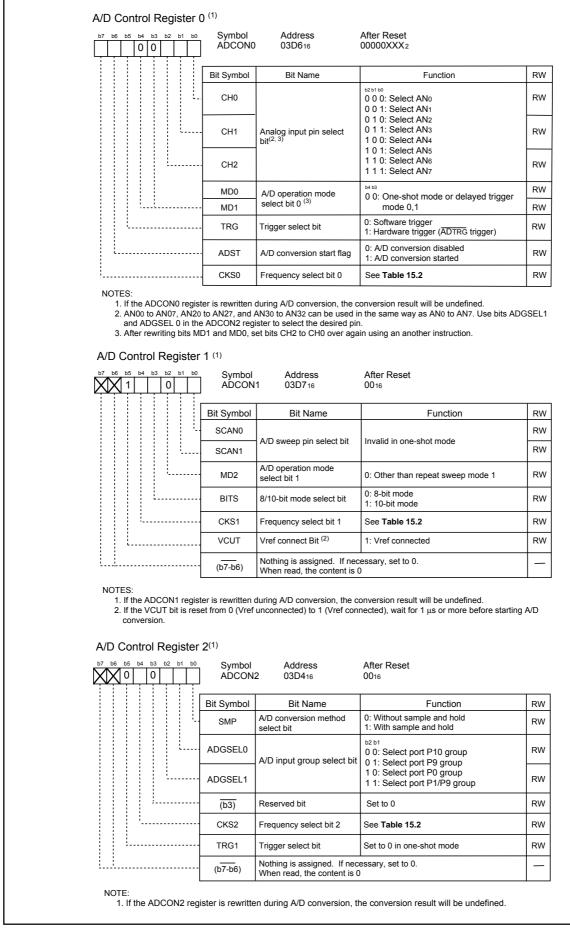

Figure 15.7 ADCON0 to ADCON2 Registers in One-Shot Mode

RENESAS

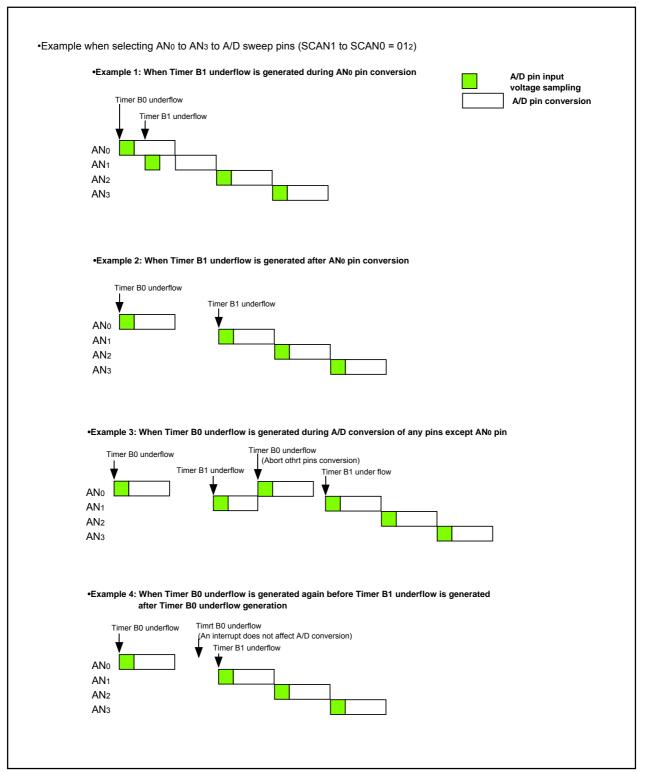

Figure 15.19 Operation Example in Delayed Trigger Mode 0

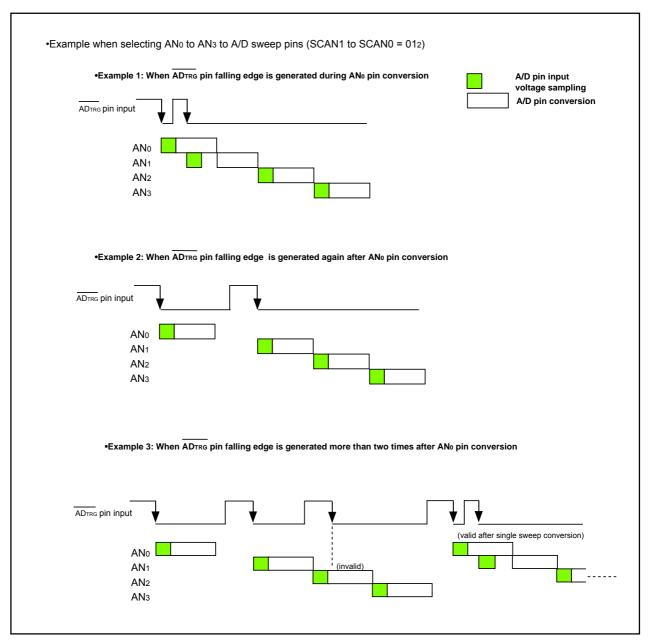

Figure 15.24 Operation Example in Delayed Trigger Mode1

## 21.6 Timer

#### 21.6.1 Timer A

#### 21.6.1.1 Timer A (Timer Mode)

1. The timer remains idle after reset. Set the mode, count source, counter value, etc. using the TAiMR (i = 0 to 4) register and the TAi register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure the TAiMR register is modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. While counting is in progress, the counter value can be read out at any time by reading the TAi register. However, if the TAi register is read at the same time the counter is reloaded, the read value is always FFFF16. If the TAi register is read after setting a value in it, but before the counter starts counting, the read value is the one that has been set in the register.

- 3. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

#### 21.6.1.2 Timer A (Event Counter Mode)

The timer remains idle after reset. Set the mode, count source, counter value, etc. using the TAiMR (i = 0 to 4) register, the TAi register, the UDF register, bits TAZIE, TA0TGL, and TA0TGH in the ONSF register and the TRGSR register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure bits TAZIE, TA0TGL, and TA0TGH in the TAiMR register, the UDF register, the ONSF register, and the TRGSR register are modified while the TAiS bit remains 0 (count stops) regardless whether after reset or not.

- 2. While counting is in progress, the counter value can be read out at any time by reading the TAi register. However, if the TAi register is read at the same time the counter is reloaded, the read value is always FFFF16 when the timer counter underflows and 000016 when the timer counter overflows. If the TAi register is read after setting a value in it, but before the counter starts counting, the read value is the one that has been set in the register.

- 3. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

- 8. If the CPU reads the ADi register (i = 0 to 7) at the same time the conversion result is stored in the ADi register after completion of A/D conversion, an incorrect value may be stored in the ADi register. This problem occurs when a divide-by-n clock derived from the main clock or a subclock is selected for CPU clock.

- When operating in one-shot, single-sweep mode, simultaneous sample sweep mode, delayed trigger mode 0 or delayed trigger mode 1:

Check to see that A/D conversion is completed before reading the target ADi register. (Check the IR bit in the ADIC register to see if A/D conversion is completed.)

- When operating in repeat mode or repeat sweep mode 0 or 1: Use the main clock for CPU clock directly without dividing it.

- 9. If A/D conversion is forcibly terminated while in progress by setting the ADST bit in the ADCON0 register to 0 (A/D conversion halted), the conversion result of the A/D converter is undefined. The contents of ADi registers irrelevant to A/D conversion may also become undefined. If while A/D conversion is underway the ADST bit is cleared to 0 in a program, ignore the values of all ADi registers.

- 10. When setting the ADST bit in the ADCON register to 0 and terminating forcefully by a program in single sweep conversion mode, A/D delayed trigger mode 0 and A/D delayed trigger mode 1 during A/D converting operation, the A/D interrupt request may be generated. If this causes a problem, set the ADST bit to 0 after an interrupt is disabled.