XFI

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             |                                                                                  |

| Core Size                  | ·                                                                                |

| Speed                      |                                                                                  |

| Connectivity               | ·                                                                                |

| Peripherals                | -                                                                                |

| Number of I/O              |                                                                                  |

| Program Memory Size        |                                                                                  |

| Program Memory Type        |                                                                                  |

| EEPROM Size                |                                                                                  |

| RAM Size                   | ·                                                                                |

| Voltage - Supply (Vcc/Vdd) |                                                                                  |

| Data Converters            | -                                                                                |

| Oscillator Type            | -                                                                                |

| Operating Temperature      | -                                                                                |

| Mounting Type              | -                                                                                |

| Package / Case             | -                                                                                |

| Supplier Device Package    | -                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30281favhp-u3a |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 4.3 SFR Information(3)<sup>(1)</sup>

| ddress           | Register                                                            | Symbol | After Reset       |

|------------------|---------------------------------------------------------------------|--------|-------------------|

|                  |                                                                     |        |                   |

|                  |                                                                     |        |                   |

| 01B016           |                                                                     |        |                   |

| 01B116           |                                                                     |        |                   |

| 01B216<br>01B316 | Elach memory control register 4 (2)                                 | FMR4   | 01000000          |

| 01B316<br>01B416 | Flash memory control register 4 (2)                                 | FIVIR4 | 01000002          |

| 01B516           | Flash memory control register 1 (2)                                 | FMR1   | 000XXX0X2         |

| 01B616           |                                                                     |        |                   |

| 01B716           | Flash memory control register 0 <sup>(2)</sup>                      | FMR0   | 00000012          |

| 01B816<br>01B916 |                                                                     |        |                   |

| 012010           |                                                                     |        |                   |

| <b>:</b>         |                                                                     |        |                   |

|                  |                                                                     |        |                   |

| 021016           | Low-power Consumption Control 0                                     | LPCC0  | X00000012         |

| 021116<br>021216 |                                                                     |        |                   |

| 021216           |                                                                     |        |                   |

| 021416           |                                                                     |        |                   |

| 021516           |                                                                     |        |                   |

| 021616           |                                                                     |        |                   |

| 021716<br>021816 |                                                                     |        |                   |

| 021916           |                                                                     |        |                   |

|                  |                                                                     |        |                   |

| 5                |                                                                     |        |                   |

| 025016           |                                                                     |        |                   |

| 025116           |                                                                     |        |                   |

| 025216<br>025316 |                                                                     |        |                   |

| 025416           |                                                                     |        |                   |

| 025516           |                                                                     |        |                   |

| 025616           |                                                                     |        |                   |

| 025716           |                                                                     |        |                   |

| 025816<br>025916 |                                                                     |        |                   |

| 025516<br>025A16 | Three-phase protect control register                                | TPRC   | 0016              |

| 025B16           |                                                                     |        |                   |

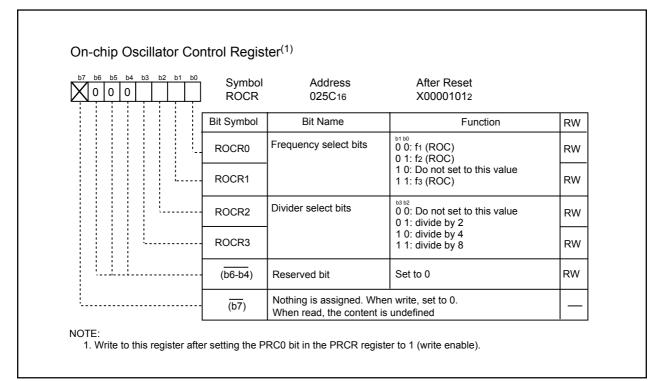

| 025C16           | On-chip oscillator control register                                 | ROCR   | X00001012         |

| 025D16           | Pin assignment control register                                     | PACR   | 0016              |

| 025E16<br>025F16 | Peripheral clock select register<br>Low-power Consumption Control 1 | PCLKR  | 000000112         |

| 02JF 10          |                                                                     | LPCC1  | 0016              |

| ä                |                                                                     |        |                   |

|                  | 2                                                                   |        |                   |

| 02E016           | I <sup>2</sup> C0 data shift register                               | S00    | XX16              |

| 02E116<br>02E216 | I <sup>2</sup> C0 address register                                  | SODO   | 0016              |

| 02E216<br>02E316 | I <sup>2</sup> C0 control register 0                                | S1D0   | 0016              |

| 02E416           | I <sup>2</sup> C0 clock control register                            | S20    | 0016              |

| 02E516           | I <sup>2</sup> C0 start/stop condition control register             | S2D0   | 000110102         |

| 02E616           | I <sup>2</sup> C0 control register 1                                | S3D0   | 001100002         |

| 02E716<br>02E816 | I <sup>2</sup> C0 control register 2                                | S4D0   | 0016<br>0001000X2 |

| 02E816<br>02E916 | I <sup>2</sup> C0 status register                                   | S10    | 0001000X2         |

| 02EA16           |                                                                     |        |                   |

|                  |                                                                     |        |                   |

| ۲<br>۲           |                                                                     |        |                   |

|                  |                                                                     |        |                   |

| 02FE16           |                                                                     |        |                   |

Note 1:The blank spaces are reserved. No access is allowed. Note 2:This register is included in the flash memory version.

X : Undefined

# 5. Reset

Hardware reset 1, software reset, watchdog timer reset, and oscillation stop detection reset are implemented to reset the MCU.

# 5.1 Hardware Reset

# 5.1.1 Hardware Reset 1

Pins, CPU, and SFRs are reset by using the RESET pin. When a low-level ("L") signal is applied to the RESET pin while the supply voltage meets the recommended operating condition, pins, CPU, and SFRs are reset (see **Table 5.1** Pin Status When RESET Pin Level is "L"). The oscillation circuit is also reset and the on-chip oscillator starts oscillating as the CPU clock. CPU and SFRs re reset when the signal applied to the RESET pin changes from "L" to high ("H"). The MCU executes a program beginning with the address indicated by the reset vector. The internal RAM is not reset. When an "L" signal is applied to the RESET pin while writing data to the internal RAM, the content of internal RAM is undefined.

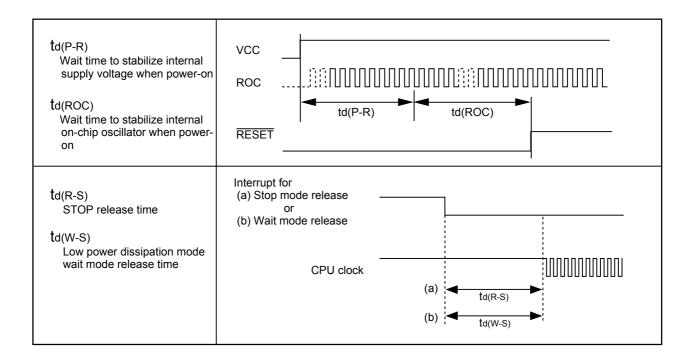

**Figure 5.1** shows an example of the reset circuit. **Figure 5.2** shows a reset sequence. **Table 5.1** shows status of the other pins while the **RESET** pin is held "L". **Figure 5.3** shows CPU register states after reset. Refer to **4. Special Function Register (SFR)** about SFR states after reset.

- 1. Reset on a stable supply voltage

- (1) Apply an "L" signal to the  $\overline{\text{RESET}}$  pin

- (2) Wait *td(ROC)* or more

- (3) Apply an "H" signal to the  $\overline{\text{RESET}}$  pin

2. Power-on reset

- (1) Apply an "L" signal to the  $\overline{\text{RESET}}$  pin

- (2) Increase the supply voltage until it meets the the recommended performance condition

- (3) Wait for *td(P-R)* or more to allow the internal power supply to stabilize

- (4) Wait *td(ROC)* or more

- (5) Apply an "H" signal to the  $\overline{\text{RESET}}$  pin

# 6. Processor Mode

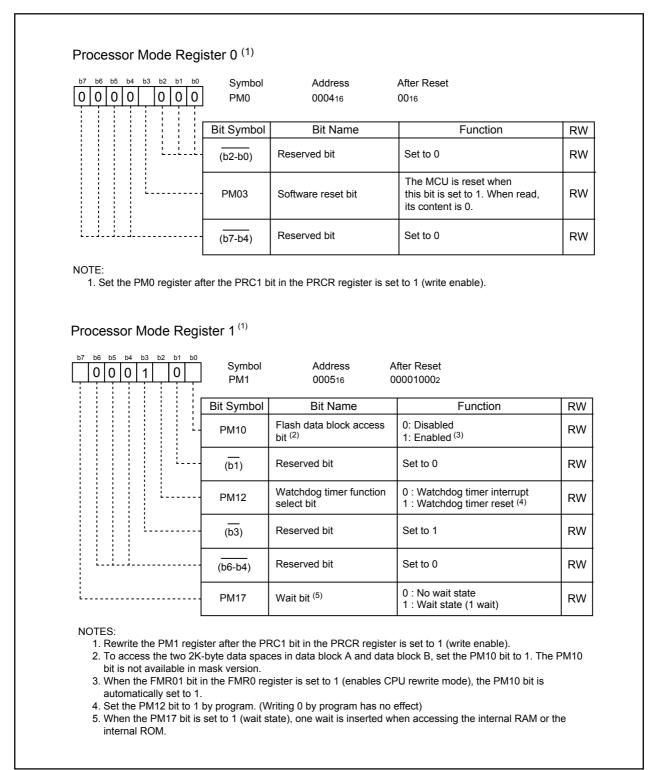

The MCU supports single-chip mode only. **Figures 6.1** and **6.2** show the associated registers.

Figure 6.1 PM0 Register, PM1 Register

Г

| Function     RW       bit     0 : Clock on<br>1 : All clocks off (stop mode)     RW       bit 1     0 : Main clock<br>1 : PLL clock <sup>(5)</sup> RW |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 : All clocks off (stop mode)     RW       bit 1     0 : Main clock<br>1 : PLL clock <sup>(5)</sup> RW                                               |

| 1 : PLL clock <sup>(5)</sup>                                                                                                                          |

|                                                                                                                                                       |

| Set to 0                                                                                                                                              |

| ity 0 : LOW<br>1 : HIGH RW                                                                                                                            |

| 0 0 : No division mode<br>0 1 : Division by 2 mode                                                                                                    |

| 1 0 : Division by 4 mode<br>1 1 : Division by 16 mode                                                                                                 |

|                                                                                                                                                       |

- the CM11 bit to 1 (PLL clock).

When the PM21 bit in the PM2 register is set to 1 (clock modification disable), writing to bits CM10, CM11 has no effect. When the PM22 bit in the PM2 register is set to 1 (watchdog timer count source is on-chip oscillator clock), writing to the CM10 bit has no effect.

- 7. Effective when CM07 bit is 0 and CM21 bit is 0 .

Figure 7.3 CM1 Register

Figure 7.4 ROCR Register

### Table 11.1 DMAC Specifications

| Item                                    |                 | Specification                                                                 |  |  |

|-----------------------------------------|-----------------|-------------------------------------------------------------------------------|--|--|

| No. of channels                         | 6               | 2 (cycle steal method)                                                        |  |  |

|                                         |                 | <ul> <li>From any address in the 1M bytes space to a fixed address</li> </ul> |  |  |

|                                         |                 | <ul> <li>From a fixed address to any address in the 1M bytes space</li> </ul> |  |  |

|                                         |                 | <ul> <li>From a fixed address to a fixed address</li> </ul>                   |  |  |

| Maximum No. of bytes transferred        |                 | 128K bytes (with 16-bit transfers) or 64K bytes (with 8-bit transfers)        |  |  |

| DMA request factors (1, 2)              |                 | Falling edge of INT0 or INT1                                                  |  |  |

|                                         |                 | Both edge of INT0 or INT1                                                     |  |  |

|                                         |                 | Timer A0 to timer A4 interrupt requests                                       |  |  |

|                                         |                 | Timer B0 to timer B2 interrupt requests                                       |  |  |

|                                         |                 | UART0 transfer, UART0 reception interrupt requests                            |  |  |

|                                         |                 | UART1 transfer, UART1 reception interrupt requests                            |  |  |

|                                         |                 | UART2 transfer, UART2 reception interrupt requests                            |  |  |

|                                         |                 | SI/O3, SI/O4 interrupt requests                                               |  |  |

|                                         |                 | A/D conversion interrupt requests                                             |  |  |

|                                         |                 | Timer S(IC/OC) requests                                                       |  |  |

|                                         |                 | Software triggers                                                             |  |  |

| Channel priority                        | ý               | DMA0 > DMA1 (DMA0 takes precedence)                                           |  |  |

| Transfer unit                           |                 | 8 bits or 16 bits                                                             |  |  |

| Transfer addres                         | ss direction    | forward or fixed (The source and destination addresses cannot both be         |  |  |

|                                         |                 | in the forward direction)                                                     |  |  |

| Transfer mode                           | Single transfer | Transfer is completed when the DMAi transfer counter (i = 0,1)                |  |  |

|                                         |                 | underflows after reaching the terminal count                                  |  |  |

|                                         | Repeat transfer | When the DMAi transfer counter underflows, it is reloaded with the value      |  |  |

|                                         |                 | of the DMAi transfer counter reload register and a DMA transfer is con        |  |  |

|                                         |                 | tinued with it                                                                |  |  |

| DMA interrupt request generation timing |                 | When the DMAi transfer counter underflowed                                    |  |  |

| DMA startup                             |                 | Data transfer is initiated each time a DMA request is generated when          |  |  |

| the                                     |                 | DMAE bit in the DMAiCON register = 1 (enabled)                                |  |  |

| DMA shutdown                            | Single transfer | When the DMAE bit is set to 0 (disabled)                                      |  |  |

|                                         |                 | After the DMAi transfer counter underflows                                    |  |  |

|                                         | Repeat transfer | When the DMAE bit is set to 0 (disabled)                                      |  |  |

| Reload timing                           | for forward ad- | When a data transfer is started after setting the DMAE bit to 1 (en           |  |  |

| dress pointer a                         | nd transfer     | abled), the forward address pointer is reloaded with the value of the         |  |  |

| counter                                 |                 | SARi or the DARi pointer whichever is specified to be in the forward          |  |  |

|                                         |                 | direction and the DMAi transfer counter is reloaded with the value of the     |  |  |

|                                         |                 | DMAi transfer counter reload register                                         |  |  |

|                                         |                 | <b>`</b>                                                                      |  |  |

NOTES:

1. DMA transfer is not effective to any interrupt. DMA transfer is affected neither by the I flag nor by the interrupt control register.

- 2. The selectable causes of DMA requests differ with each channel.

- 3. Make sure that no DMAC-related registers (addresses 002016 to 003F16) are accessed by the DMAC.

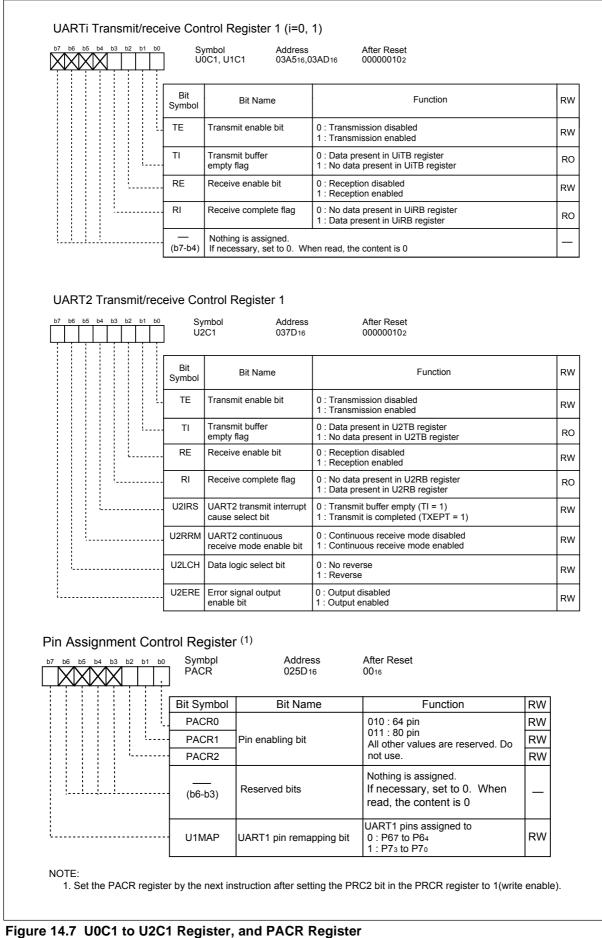

# 14. Serial I/O

Note

The SI/O4 interrupt of peripheral function interrupt is not available in the 64-pin package.

Serial I/O is configured with five channels: UART0 to UART2, SI/O3 and SI/O4.

# 14.1 UARTi (i=0 to 2)

UARTi each have an exclusive timer to generate a transfer clock, so they operate independently of each other.

**Figure 14.1** shows the block diagram of UARTi. **Figures 14.2** and **14.3** shows the block diagram of the UARTi transmit/receive.

UARTi has the following modes:

- Clock synchronous serial I/O mode

- Clock asynchronous serial I/O mode (UART mode).

- Special mode 1 (I<sup>2</sup>C bus mode): UART2

- Special mode 2: UART2

- Special mode 3 (Bus collision detection function, IEBus mode): UART2

- Special mode 4 (SIM mode): UART2

Figures 14.4 to 14.9 show the UARTi-associated registers.

Refer to Tables 14.2, 14.6, 14.11, 14.12, 14.16, 14.17, and 14.19 to set the registers in individual mode.

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                       |                                                                                                                                                | nbol Addres<br>SMR3 037516                                                                                                                                                                                                                                                                                | s After Reset<br>000X0X0X2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                                                                               | Bit<br>Symbol                                                                                                                                  | Bit Name                                                                                                                                                                                                                                                                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R\                                                   |

|                                                                                                                                               |                                                                                                                                                | Nothing is assigned. If ne When read, the content is                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                    |

|                                                                                                                                               |                                                                                                                                                | Clock phase set bit                                                                                                                                                                                                                                                                                       | 0 : Without clock delay<br>1 : With clock delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RV                                                   |

|                                                                                                                                               |                                                                                                                                                | Nothing is assigned. If ne When read, the content is                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                    |

|                                                                                                                                               | NODC                                                                                                                                           | Clock output select bit                                                                                                                                                                                                                                                                                   | 0 : CLK2 is CMOS output<br>1 : CLK2 is N-channel open drain output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                    |

|                                                                                                                                               |                                                                                                                                                | Nothing is assigned. If ne When read, the content is                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                    |

|                                                                                                                                               |                                                                                                                                                | SDA2 digital delay<br>setup bit<br>(1, 2)                                                                                                                                                                                                                                                                 | b7 b6 b5<br>0 0 0 : Without delay<br>0 0 1 : 1 to 2 cycle(s) of U2BRG count source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                    |

|                                                                                                                                               | DL1                                                                                                                                            |                                                                                                                                                                                                                                                                                                           | 0 1 0 : 2 to 3 cycles of U2BRG count source<br>0 1 1 : 3 to 4 cycles of U2BRG count source<br>1 0 0 : 4 to 5 cycles of U2BRG count source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RV                                                   |

|                                                                                                                                               | DL2                                                                                                                                            |                                                                                                                                                                                                                                                                                                           | 1 0 1 : 5 to 6 cycles of U2BRG count source<br>1 1 0 : 6 to 7 cycles of U2BRG count source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                    |

| mode, set these bit<br>2. The amount of dela<br>delay increases by                                                                            | s to 0002 (ne<br>y varies with<br>about 100 ne                                                                                                 | o delay).<br>the load on pins SCL2 ar<br>s.                                                                                                                                                                                                                                                               | 1 1 1 : 7 to 8 cycles of U2BRG count source<br>but by digital means during I <sup>2</sup> C bus mode. In other th<br>d SDA2. Also, when using an external clock, the an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nan I <sup>2</sup> C t                               |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of delation</li> </ol>                                               | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>] Sym                                                                           | o delay).<br>the load on pins SCL2 ar<br>s.<br>er 4                                                                                                                                                                                                                                                       | ut by digital means during I <sup>2</sup> C bus mode. In other th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nan I <sup>2</sup> C I                               |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>Sym<br>U2S                                                                      | o delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416                                                                                                                                                                                                                          | After Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nan I <sup>2</sup> C t                               |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>] Sym<br>U2S<br>Bit<br>Symbol                                                   | b delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name                                                                                                                                                                                                              | After Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nan I <sup>2</sup> C t<br>nount of                   |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>Sym<br>U2S<br>Bit<br>Symbol<br>STAREQ                                           | b delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name<br>Start condition<br>generate bit <sup>(1)</sup>                                                                                                                                                            | After Reset 0016 0 : Clear 1 : Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nan I <sup>2</sup> C t<br>nount of<br>R\             |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>Symbol<br>Bit<br>Symbol<br>STAREQ                                               | b delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name<br>Start condition<br>generate bit <sup>(1)</sup><br>Restart condition<br>generate bit <sup>(1)</sup>                                                                                                        | After Reset<br>0016<br>0 : Clear<br>1 : Start<br>0 : Clear<br>1 : Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nan I <sup>2</sup> C t<br>nount of<br>R\             |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>Symbol<br>STAREQ<br>STAREQ                                                      | bo delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name<br>Start condition<br>generate bit <sup>(1)</sup><br>Restart condition<br>generate bit <sup>(1)</sup><br>Stop condition<br>generate bit <sup>(1)</sup>                                                      | After Reset<br>0016<br>0 : Clear<br>1 : Start<br>0 : Clear<br>1 : Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nan I <sup>2</sup> C t<br>nount of<br>R\<br>R\<br>R\ |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>Sym<br>U2S<br>Bit<br>Symbol<br>STAREQ<br>RSTAREQ<br>STPREQ<br>STSPSEL           | bo delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name<br>Start condition<br>generate bit <sup>(1)</sup><br>Restart condition<br>generate bit <sup>(1)</sup><br>Stop condition<br>generate bit <sup>(1)</sup><br>SCL2,SDA2 output<br>select bit                    | After Reset<br>0016<br>0 : Clear<br>1 : Start<br>0 : Clear<br>1 : Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nan I <sup>2</sup> C t                               |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>Symbol<br>STAREQ<br>STAREQ                                                      | bo delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name<br>Start condition<br>generate bit <sup>(1)</sup><br>Restart condition<br>generate bit <sup>(1)</sup><br>Stop condition<br>generate bit <sup>(1)</sup><br>Stop condition<br>generate bit <sup>(1)</sup>     | After Reset<br>0016<br>0 : Clear<br>1 : Start<br>0 : Clear<br>1 : Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RV                                                   |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>Sym<br>U2S<br>Bit<br>Symbol<br>STAREQ<br>RSTAREQ<br>STPREQ<br>STSPSEL           | bo delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name<br>Start condition<br>generate bit <sup>(1)</sup><br>Restart condition<br>generate bit <sup>(1)</sup><br>Stop condition<br>generate bit <sup>(1)</sup><br>SCL2,SDA2 output<br>select bit                    | After Reset<br>0016<br>Function<br>0 : Clear<br>1 : Start<br>0 : Start and stop conditions not output<br>1 : Start and stop conditions output<br>0 : ACK<br>1 : NACK<br>0 : Serial I/O data output<br>1 : ACK data output                                            | RV                                                   |

| <ol> <li>Bits DL2 to DL0 are<br/>mode, set these bit</li> <li>The amount of dela<br/>delay increases by</li> <li>UART2 Special Mod</li> </ol> | s to 0002 (no<br>y varies with<br>about 100 ns<br>e Registe<br>] Sym<br>U2S<br>Bit<br>Symbol<br>STAREQ<br>RSTAREQ<br>STPREQ<br>STSPSEL<br>ACKD | bo delay).<br>the load on pins SCL2 ar<br>s.<br>er 4<br>bol Address<br>MR4 037416<br>Bit Name<br>Start condition<br>generate bit <sup>(1)</sup><br>Restart condition<br>generate bit <sup>(1)</sup><br>Stop condition<br>generate bit <sup>(1)</sup><br>SCL2,SDA2 output<br>select bit<br>ACK data output | After Reset<br>0016<br>0 : Clear<br>1 : Start<br>0 : Start and stop conditions not output<br>1 : Start and stop conditions output<br>0 : ACK<br>1 : NACK<br>0 : Serial I/O data output | RV                                                   |

Figure 14.9 U2SMR3 and U2SMR4 Registers

### 14.1.1.4 Continuous receive mode

When the UiRRM bit (i=0 to 2) is set to 1 (continuous receive mode), the TI bit in the UiC1 register is set to "0" (data present in the UiTB register) by reading the UiRB register. In this case, i.e., UiRRM bit is set to 1, do not write dummy data to the UiTB register in a program. The U0RRM and U1RRM bits are the bit 2 and bit 3 in the UCON register, respectively, and the U2RRM bit is the bit 5 in the U2C1 register.

### 14.1.1.5 Serial data logic switch function (UART2)

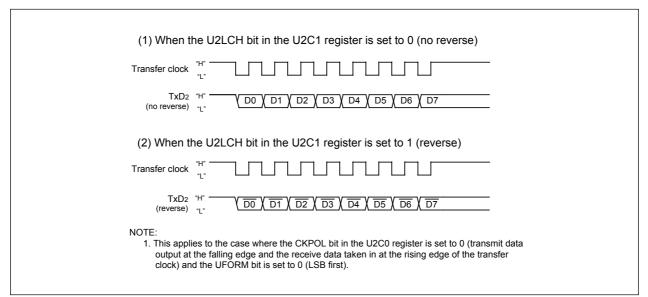

When the U2LCH bit in the U2C1 register is set to 1 (reverse), the data written to the U2TB register has its logic reversed before being transmitted. Similarly, the received data has its logic reversed when read from the U2RB register. **Figure 14.13** shows serial data logic.

Figure 14.13 Serial data logic switch timing

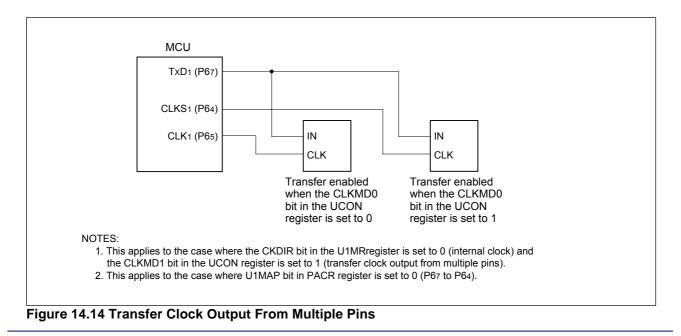

### 14.1.1.6 Transfer clock output from multiple pins function (UART1)

The CLKMD1 to CLKMD0 bits in the UCON register can choose one from two transfer clock output pins. (See **Figure 14.14**) This function is valid when the internal clock is selected for UART1.

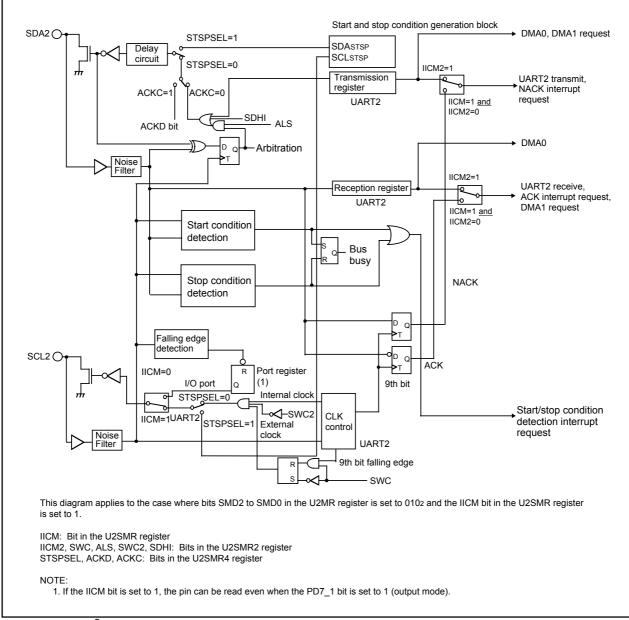

Figure 14.22 I<sup>2</sup>C bus Mode Block Diagram

### 14.1.3.7 ACK and NACK

If the STSPSEL bit in the U2SMR4 register is set to 0 (start and stop conditions not generated) and the ACKC bit in the U2SMR4 register is set to 1 (ACK data output), the value of the ACKD bit in the U2SMR4 register is output from the SDA2 pin.

If the IICM2 bit is set to 0, a NACK interrupt request is generated if the SDA2 pin remains high at the rising edge of the 9th bit of transmit clock pulse. An ACK interrupt request is generated if the SDA2 pin is low at the rising edge of the 9th bit of transmit clock pulse.

If ACK2 is selected for the cause of DMA1 request, a DMA transfer can be activated by detection of an acknowledge.

### 14.1.3.8 Initialization of Transmission/Reception

If a start condition is detected while the STAC bit is set to 1 (UART2 initialization enabled), the serial I/ O operates as described below.

- The transmit shift register is initialized, and the content of the U2TB register is transferred to the transmit shift register. In this way, the serial I/O starts sending data synchronously with the next clock pulse applied. However, the UART2 output value does not change state and remains the same as when a start condition was detected until the first bit in the data is output synchronously with the input clock.

- The receive shift register is initialized, and the serial I/O starts receiving data synchronously with the next clock pulse applied.

- The SWC bit is set to 1 (SCL2 wait output enabled). Consequently, the SCL2 pin is pulled low at the falling edge of the ninth clock pulse.

Note that when UART2 transmission/reception is started using this function, the TI does not change state. Note also that when using this function, the selected transfer clock should be an external clock.

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Symbol<br>ADTRG | Address<br>CON 03D216                                   | After Reset<br>0016                                               |    |

|-------------------------------------------------------|-----------------|---------------------------------------------------------|-------------------------------------------------------------------|----|

|                                                       | Bit Symbol      | Bit Name                                                | Function                                                          | RW |

|                                                       | SSE             | A/D operation mode select bit 2                         | 1: Simultaneous sample sweep mode or<br>delayed trigger mode 0, 1 | RW |

|                                                       | DTE             | A/D operation mode select bit 3                         | 0: Other than delayed trigger mode 0, 1                           | RW |

|                                                       | HPTRG0          | AN0 trigger select bit                                  | See Table 15.9                                                    | RW |

|                                                       | HPTRG1          | AN1 trigger select bit                                  | Set to 0 in simultaneous sample sweep mode                        | RW |

| ·····                                                 | (b7-b4)         | Nothing is assigned. If nec When read, the content is 0 |                                                                   | -  |

Figure 15.18 ADTRGCON Register in Simultaneous Sample Sweep Mode

| TRG | TRG1 | HPTRG0 | TRIGGER                                                     |

|-----|------|--------|-------------------------------------------------------------|

| 0   | -    | -      | Software trigger                                            |

| 1   | -    | 1      | Timer B0 underflow <sup>(1)</sup>                           |

| 1   | 0    | 0      | ADTRG                                                       |

| 1   | 1    | 0      | Timer B2 or Timer B2 interrupt generation frequency setting |

|     |      | 0      | counter underflow <sup>(2)</sup>                            |

### Table 15.9 Trigger Select Bit Setting in Simultaneous Sample Sweep Mode

NOTES:

1. A count can be started for Timer <u>B2. Timer</u> B2 interrupt generation frequency setting counter underflow or the INT5 pin falling edge as count start conditions of Timer B0.

Select Timer B2 or Timer B2 interrupt generation frequency setting counter using the TB2SEL bit in the TB2SC register.

# **16. Multi-master I<sup>2</sup>C bus Interface**

The multi-master I<sup>2</sup>C bus interface is a serial communication circuit based on Philips I<sup>2</sup>C bus data transfer format, equipped with arbitration lost detection and synchronous functions. **Figure 16.1** shows a block diagram of the multi-master I<sup>2</sup>C bus interface and **Table 16.1** lists the multi-master I<sup>2</sup>C bus interface functions.

The multi-master I<sup>2</sup>C bus interface consists of the S0D0 register, the S00 register, the S20 register, the S3D0 register, the S4D0 register, the S10 register, the S2D0 register and other control circuits.

Figures 16.2 to 16.8 show the registers associated with the multi-master  $\mathsf{I}^2\mathsf{C}$  bus.

| Item                | Function                                          |  |  |

|---------------------|---------------------------------------------------|--|--|

| Format              | Based on Philips I <sup>2</sup> C bus standard:   |  |  |

|                     | 7-bit addressing format                           |  |  |

|                     | High-speed clock mode                             |  |  |

|                     | Standard clock mode                               |  |  |

| Communication mode  | Based on Philips I <sup>2</sup> C bus standard:   |  |  |

|                     | Master transmit                                   |  |  |

|                     | Master receive                                    |  |  |

|                     | Slave transmit                                    |  |  |

|                     | Slave receive                                     |  |  |

| SCL clock frequency | 16.1kHz to 400kHz (at VIIC <sup>(1)</sup> = 4MHz) |  |  |

| I/O pin             | Serial data line SDAмм(SDA)                       |  |  |

|                     | Serial clock line SDLMM(SCL)                      |  |  |

Table 16.1 Multi-master I<sup>2</sup>C bus interface functions

NOTE:

1. VIIC=I<sup>2</sup>C system clock

# 16.5 I<sup>2</sup>C0 Status Register (S10 register)

The S10 register monitors the  $l^2C$  bus interface status. When using the S10 register to check the status, use the 6 low-order bits for read only.

# 16.5.1 Bit 0: Last Receive Bit (LRB)

The LRB bit stores the last bit value of received data. It can also be used to confirm whether ACK is received. If the ACK-CLK bit in the S20 register is set to 1 (with ACK clock) and ACK is returned when the ACK clock is generated, the LRB bit is set to 0. If ACK is not returned, the LRB bit is set to 1. When the ACK-CLK bit is set to 0 (no ACK clock), the last bit value of received data is input. When writing data to the S00 register, the LRB bit is set to 0.

# 16.5.2 Bit 1: General Call Detection Flag (ADR0)

When the ALS bit in the S1D0 register is set to 0 (addressing format), this ADR0 flag is set to 1 by receiving the general calls<sup>(1)</sup>, whose address data are all 0, in slave mode.

The ADR0 flag is set to 0 when STOP or START conditions is detected or when the IHR bit in the S1D0 register is set to 1 (reset).

NOTE:

1. General call: A master device transmits the general call address 0016 to all slaves. When the master device transmits the general call, all slave devices receive the controlled data after general call.

# 16.5.3 Bit 2: Slave Address Comparison Flag (AAS)

The AAS flag indicates a comparison result of the slave address data after enabled by setting the ALS bit in the S1D0 register to 0 (addressing format).

The AAS flag is set to 1 when the 7 bits of the address data are matched with the slave address stored into the S0D0 register, or when a general call is received, in slave receive mode. The AAS flag is set to 0 by writing data to the S00 register. When the ES0 bit in the S1D0 register is set to 0 ( $I^2C$  bus interface disabled) or when the IHR bit in the S1D0 register is set to 1 (reset), the AAS flag is also set to 0.

# 16.5.4 Bit 3: Arbitration Lost Detection Flag (AL)<sup>(1)</sup>

In master transmit mode, if an "L" signal is applied to the SDA pin by other than the MCU, the AL flag is set to 1 by determining that the arbitration is los and the TRX bit in the S10 register is set to 0 (receive mode) at the same time. The MST bit in the S10 register is set to 0 (slave mode) after transferring the bytes which lost the arbitration.

The arbitration lost can be detected only in master transmit mode. When writing data to the S00 register, the AL flag is set to 0. When the ES0 bit in the S1D0 register is set to 0 ( $I^2C$  bus interface disabled) or when the IHR bit in the S1D0 register is set to 1 (reset), the AL flag is set to 0.

NOTE:

1. Arbitration lost: communication disabled as a master

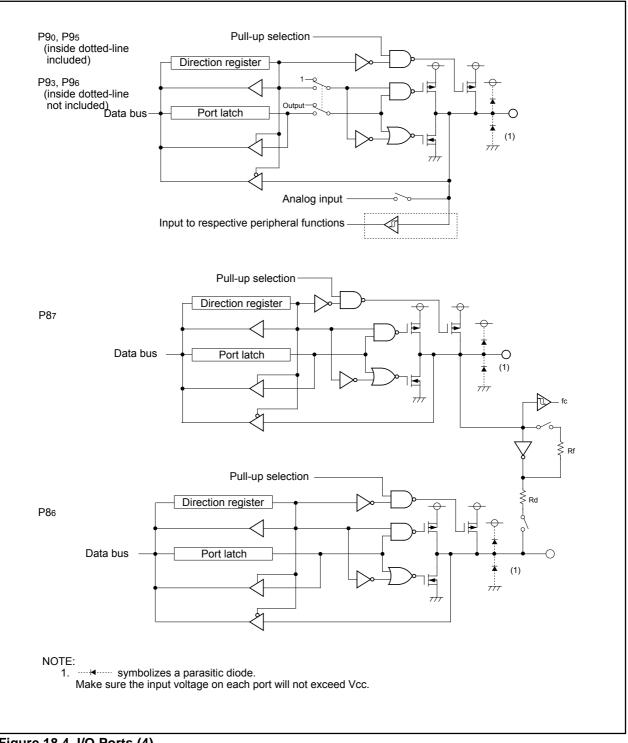

Figure 18.4 I/O Ports (4)

### Table 20.44 Power Supply Circuit Timing Characteristics

| Symbol  | Parameter                                                        | Measurement Condition | Standard |      |      | Unit |

|---------|------------------------------------------------------------------|-----------------------|----------|------|------|------|

|         |                                                                  |                       | Min.     | Тур. | Max. | Onic |

| td(P-R) | Wait Time to Stabilize Internal Supply Voltage when Power-on     |                       |          |      | 2    | ms   |

| td(ROC) | Wait Time to Stabilize Internal On-chip Oscillator when Power-on | V∞=4.2 to 5.5V        |          |      | 40   | μs   |

| td(S-R) | STOP Release Time                                                |                       |          |      | 150  | μs   |

| td(W-S) | Low Power Dissipation Mode Wait Mode Release<br>Time             |                       |          |      | 150  | μs   |

### 21.6.1.3 Timer A (One-shot Timer Mode)

- The timer remains idle after reset. Set the mode, count source, counter value, etc. using the TAiMR

(i = 0 to 4) register, the TAi register, bits TA0TGL and TA0TGH in the ONSF register and the

TRGSR register before setting the TAiS bit in the TABSR register to 1 (count starts).

Always make sure bits TA0TGL and TA0TGH in the TAiMR register, the ONSF register, and the

TRGSR register are modified while the TAiS bit remains 0 (count stops) regardless whether after

reset or not.

- 2. When setting TAiS bit to 0 (count stop), the followings occur:

- A counter stops counting and a content of reload register is reloaded.

- TAiout pin outputs "L".

- After one cycle of the CPU clock, the IR bit in TAiIC register is set to 1 (interrupt request).

- 3. Output in one-shot timer mode synchronizes with a count source internally generated. When the external trigger has been selected, a maximun delay of one cycle of the count source occurs between the trigger input to TAiN pin and output in one-shot timer mode.

- 4. The IR bit is set to 1 when timer operation mode is set with any of the following procedures:

- Select one-shot timer mode after reset.

- Change an operation mode from timer mode to one-shot timer mode.

- Change an operation mode from event counter mode to one-shot timer mode.

To use the timer Ai interrupt (the IR bit), set the IR bit to 0 after the changes listed above have been made.

- 5. When a trigger occurs while the timer is counting, the counter reloads the reload register value, and continues counting after a second trigger is generated and the counter is decremented once. To generate a trigger while counting, space more than one cycle of the timer count source from the first trigger and generate again.

- 6. When selecting the external trigger for the count start conditions in timer A one-shot timer mode, do not generate an external trigger 300ns before the count value of timer A is set to 000016. The one-shot timer may stop counting.

- 7. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the TA10UT, TA20UT and TA40UT pins go to a high-impedance state.

# 21.7.2 Rewrite the ICOCiIC Register

When the interrupt request to the ICOCiIC register is generated during the instruction process, the IR bit may not be set to 1 (interrupt requested) and the interrupt request may not be acknowledged. At that time, when the bit in the G1IR register is held to 1 (interrupt requested), the following IC/OC interrupt request will not be generated. When changing the ICOCiIC register settiing, use the following instruction.

Subject instructions: AND, OR, BCLR, BSET

When initializing Timer S, change the ICOCiIC register setting with the request again after setting the IOCiIC and G1IR registers to 0016.

### 21.7.3 Waveform Generating Function

1. If the BTS bit in the G1BCR1 register is set to 0 (base timer is reset) when the waveform is generating and the base timer is stopped counting, the waveform output pin keeps the same output level. The output level will be changed when the base timer and the G1POj register match the setting value next time after the base timer starts counting again.

2. If the G1POCRj register is set when the waveform is generated, the same setting value of the IVL bit is applied to the waveform generating pin. Do not set the G1POCRj register when the waveform is generating.

3. When the RST1 bit in the G1BCR1 register is set to 1 (the base timer is reset by matching the G1PO0 register), the base timer is reset after two clock cycles of fBT1 when the base timer value matches the G1PO0 register value. A high-level ("H") signal is applied to the OUTC10 pin between the base timer value match to the base timer reset.

# 21.7.4 IC/OC Base Timer Interrupt

If the MCU is operated in the combination selected from Tabl e 1 for use when the RST4 bit in the G1BCR0 register is set to 1 (reset the base timer that matches the G1BTRR register) to reset the base timer, an IC/OC base timer interrupt request is generated twice.

### Table 21.1 Uses of IT Bit in the G1BCR0 Register and G1BTRR Register

| IT Bit in the G1BCR0 Register          | G1BTRR Register                             |  |  |

|----------------------------------------|---------------------------------------------|--|--|

| 0 (bit 15 in the base timer overflows) | 07FFF16 to 0FFFE16                          |  |  |

| 1 (bit 14 in the base timer overflows) | 03FFF16 to 0FFFE16 or<br>0BFFF16 to 0FFFE16 |  |  |

The second IC/OC base timer interrupt request is generated because the base timer overflow request is generated after one fBT1 clock cycle as soon as the base timer is reset.

One of the following conditions must be met in order not to generate the IC/OC base timer interrupt request twice:

- 1) When the RST4 bit is set to 1, set the G1BTRR register with a combination other than what is listed in **Table 21.1**.

- 2) Do not reset the base timer by matching the G1BTRR register. Reset the base timer by matching the G1P00 register. In other words, do not set the RST4 bit to 1 to reset the base timer. Set the RST1 bit in the G1BCR1 register to 1 (reset the base timer that matches the G1P00 register).

# 21.11 Programmable I/O Ports

- 1. If a low-level signal is applied to the  $\overline{SD}$  pin when the IVPCR1 bit in the TB2SC register is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the P72 to P75, P80 and P81 pins go to a high-impedance state.

- 2. The input threshold voltage of pins differs between programmable input/output ports and peripheral functions.

Therefore, if any pin is shared by a programmable input/output port and a peripheral function and the input level at this pin is outside the range of recommended operating conditions VIH and VIL (neither "high" nor "low"), the input level may be determined differently depending on which side—the programmable input/output port or the peripheral function—is currently selected.

- 3.When the SM32 bit in the S3C register is set to 1, the P32 pin goes to high-impedance state. When the SM42 bit in the S4C register is set to 1, the P96 pin goes to high-impedance state.

- 4. When the INV03 bit in the INVC0 register is 1(three-phase motor control timer output enabled), an "L" input on the P85 /NMI/SD pin, has the following effect.

- •When the TB2SC register IVPCR1 bit is set to 1 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin enabled), the U/  $\overline{U}$ / V/  $\overline{V}$ / W/  $\overline{W}$  pins go to a high-impedance state.

- •When the TB2SC register IVPCR1 bit is set to 0 (three-phase output forcible cutoff by input on  $\overline{SD}$  pin disabled), the U/  $\overline{U}$ / V/  $\overline{V}$ / W/  $\overline{W}$  pins go to a normal port.

Therefore, the P85 pin can not be used as programmable I/O port when the INV03 bit is set to 1. When the  $\overline{SD}$  function isn't used, set to 0 (Input) in PD85 and pullup to H in the P85  $\overline{/NMI/SD}$  pin from outside.

# 21.14.9 Interrupts

EW Mode 0

- Any interrupt which has a vector in the variable vector table can be used providing that its vector is transferred into the RAM area.

- The NMI and watchdog timer interrupts can be used because the FMR0 register and FMR1 register are initialized when one of those interrupts occurs. The jump addresses for those interrupt service routines should be set in the fixed vector table.

Because the rewrite operation is halted when a  $\overline{\text{NMI}}$  or watchdog timer interrupt occurs, the rewrite program must be executed again after exiting the interrupt service routine.

• The address match interrupt cannot be used because the flash memory's internal data is referenced. EW Mode 1

- Make sure that any interrupt which has a vector in the variable vector table or address match interrupt will not be accepted during the auto program period or auto erase period with erase-suspend function disabled.

- The NMI interrupt can be used because the FMR0 register and FMR1 register are initialized when this interrupt occurs. The jump address for the interrupt service routine should be set in the fixed vector table.

Because the rewrite operation is halted when a  $\overline{\text{NMI}}$  interrupt occurs, the rewrite program must be executed again after exiting the interrupt service routine.

# 21.14.10 How to Access

To set the FMR01, FMR02, FMR11 or FMR16 bit to 1, set the subject bit to 1 immediately after setting to 0. Do not generate an interrupt or a DMA transfer between the instruction to set the bit to 0 and the instruction to set the bit to 1. Set the bit when the PM24 bit is set to 1 ( $\overline{\text{NMI}}$  funciton) and a high-level ("H") signal is applied to the  $\overline{\text{NMI}}$  pin.

# 21.14.11 Writing in the User ROM Area

EW Mode 0

If the power supply voltage drops while rewriting any block in which the rewrite control program is stored, a problem may occur that the rewrite control program is not correctly rewritten and, consequently, the flash memory becomes unable to be rewritten thereafter. In this case, standard serial I/ O or parallel I/O mode should be used.

EW Mode 1

• Avoid rewriting any block in which the rewrite control program is stored.

# 21.14.12 DMA Transfer

In EW mode 1, make sure that no DMA transfers will occur while the FMR00 bit in the FMR0 register is set to 0(during the auto program or auto erase period).

# 21.14.13 Regarding Programming/Erasure Times and Execution Time

As the number of programming/erasure times increases, so does the execution time for software commands (program command and block erase command).

The software commands are aborted by hardware reset 1,  $\overline{\text{NMI}}$  interrupt, and watchdog timer interrupt. If a software command is aborted by such reset or interrupt, the affected block must be erased before reexecuting the aborted command.