#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | TriCore™                                                                        |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 100MHz                                                                          |

| Connectivity               | CANbus, EBI/EMI, FIFO, I <sup>2</sup> C, IrDA, SPI, UART/USART                  |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 72                                                                              |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 144K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.43V ~ 1.58V                                                                   |

| Data Converters            | -                                                                               |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 208-LBGA                                                                        |

| Supplier Device Package    | P-LBGA-208-2                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-tc1115-l100eb-bb |

|                            |                                                                                 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TC1115

**Advance Information**

# **General Device Information**

# 2 General Device Information

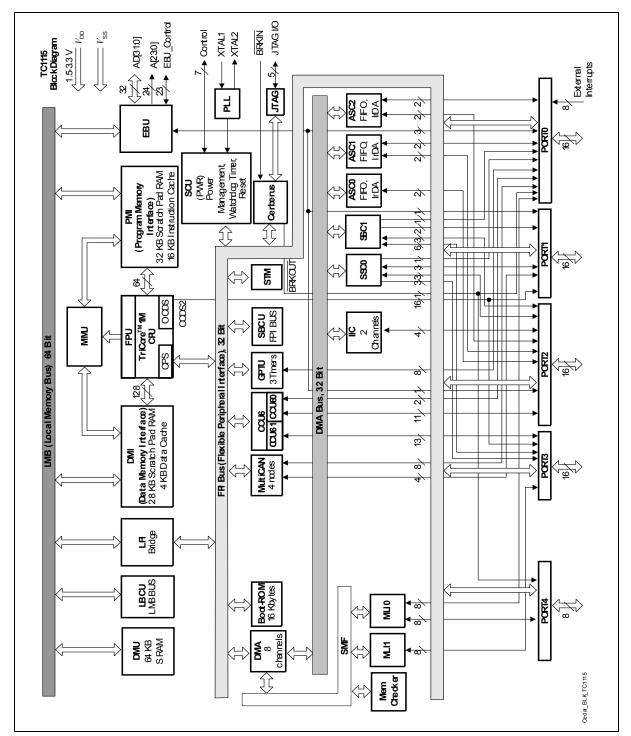

# 2.1 Block Diagram

Figure 2-1 TC1115 Block Diagram

## **General Device Information**

| Table 2-1 | Pin Definitions and Functions | (cont'd) | ) |

|-----------|-------------------------------|----------|---|

|-----------|-------------------------------|----------|---|

| Symbol | Pin | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions |                            |

|--------|-----|-----------|-------------------------|-----------|----------------------------|

| P1.7   | B13 | I         | PUC                     | SWCFG7    | Software configuration 7   |

|        |     | 0         |                         | OCDSA_7   | OCDS L2 Debug Line A7      |

| P1.8   | A13 | I         | PUC                     | SWCFG8    | Software configuration 8   |

|        |     | 0         |                         | OCDSA_8   | OCDS L2 Debug Line A8      |

| P1.9   | A14 | 1         | PUC                     | SWCFG9    | Software configuration 9   |

|        |     | 0         |                         | OCDSA_9   | OCDS L2 Debug Line A9      |

| P1.10  | B14 | 1         | PUC                     | SWCFG10   | Software configuration 10  |

|        |     | 0         |                         | OCDSA 10  | OCDS L2 Debug Line A10     |

| P1.11  | C14 | 1         | PUC                     | SWCFG11   | Software configuration 11  |

|        |     | 0         |                         | OCDSA_11  | OCDS L2 Debug Line A1      |

|        |     | 0         |                         | SLSO0_1   | SSC0 Slave Select output 1 |

| P1.12  | F13 | 1         | PUC                     | SWCFG12   | Software configuration 12  |

|        |     | 0         |                         | OCDSA_12  | OCDS L2 Debug Line A12     |

|        |     | 0         |                         | SLSO1_1   | SSC1 Slave Select output 1 |

| P1.13  | E14 | I         | PUC                     | SWCFG13   | Software configuration 13  |

|        |     | 0         |                         | OCDSA_13  | OCDS L2 Debug Line A13     |

|        |     | 0         |                         | SLSO0_2   | SSC0 Slave Select output 2 |

| P1.14  | D14 | 0         | PUC                     | SLSO1_2   | SSC1 Slave Select output 2 |

|        |     | 1         |                         | SWCFG14   | Software configuration 14  |

|        |     | 0         |                         | OCDSA_14  | OCDS L2 Debug Line A14     |

| P1.15  | F14 | 1         | PUC                     | SLSI0     | SSC0 Slave Select Input    |

|        |     | 0         |                         | RMW       | EBU Read Modify Write      |

|        |     | I         |                         | SWCFG15   | Software configuration 15  |

|        |     | 0         |                         | OCDSA_15  | OCDS L2 Debug Line A15     |

# **General Device Information**

# Table 2-1 Pin Definitions and Functions (cont'd)

| Symbol | Pin  | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions        |                                                                                                         |

|--------|------|-----------|-------------------------|------------------|---------------------------------------------------------------------------------------------------------|

| P2     |      | I/O       |                         | Port 2           |                                                                                                         |

|        |      |           |                         | which can be a   | bit bi-directional general purpose I/O port<br>alternatively used for ASC0/1/2, SSC0/1,<br>EBU and SCU. |

| P2.0   | P12  | I/O<br>O  | PUC                     | RXD0<br>CSEMU    | ASC0 receiver input/output line<br>EBU Chip Select Output for Emulator<br>Region                        |

| P2.1   | P11  | 0         | PUC                     | TXD0<br>TESTMODE | ASC0 transmitter output line<br>Test Mode Select Input                                                  |

| P2.2   | P13  | I/O       | PUC                     | MRST0            | SSC0 master receive/slave transmit input/output                                                         |

| P2.3   | P14  | I/O       | PUC                     | MTSR0            | SSC0 master transmit/slave receive                                                                      |

| P2.4   | N15  | I/O       | PUC                     | SCLK0            | SSC0 clock input/output line                                                                            |

| P2.5   | N14  | 0         | PUC                     | COUT60_3         | CCU60 compare channel 3 output                                                                          |

|        |      | I/O       |                         | MRST1A           | SSC1 master receive/slave transmit                                                                      |

| 50.0   |      |           | 5.1.6                   |                  | input/output A                                                                                          |

| P2.6   | N12  | I/O       | PUC                     | CC60_0           | CCU60 input/output of capture/                                                                          |

|        |      | I/O       |                         | MTSR1A           | compare channel 0<br>SSC1 master transmit/slave receive                                                 |

|        |      | "0        |                         | WITORIA          | input/output A                                                                                          |

| P2.7   | K16  | 0         | PUC                     | COUT60_0         | CCU60 output of capture/compare channel 0                                                               |

|        |      | I/O       |                         | SCLK1A           | SSC1 clock input/output line A                                                                          |

| P2.8   | J16  | I/O       | PUC                     | CC60_1           | CCU60 input/output of capture/<br>compare channel 1                                                     |

|        |      | I/O       |                         | RXD1A            | ASC1 receiver input/output line A                                                                       |

| P2.9   | H16  | 0         | PUC                     | COUT60_1         | CCU60 output of capture/compare channel 1                                                               |

|        |      | 0         |                         | TXD1A            | ASC1 transmitter output line A                                                                          |

| P2.10  | L13  | I/O       | PUC                     | CC60_2           | CCU60 input/output of capture/                                                                          |

|        |      |           |                         |                  | compare channel 2                                                                                       |

|        | 0.10 | 1/0       |                         | RXD2A            | ASC2 receiver input/output line A                                                                       |

| P2.11  | G16  | 0         | PUC                     | COUT60_2         | CCU60 output of capture/compare<br>channel 2                                                            |

|        |      | 0         |                         | TXD2A            | ASC2 transmitter output line A                                                                          |

| P2.12  | K15  | I/O       |                         | SDA0             | IIC Serial Data line 0                                                                                  |

|        |      | 1         |                         | CTRAP0           | CCU60 trap input                                                                                        |

| _      |      | 0         |                         | SLSO0_3          | SSC0 Slave Select output 3                                                                              |

#### **Functional Description**

#### 3.2 Address Map

**Table 3-1** defines the specific segment oriented address blocks of the TC1115 with its address range, size, and PMI/DMI access view. **Table 3-2** shows the block address map of the Segment 15 which includes on-chip peripheral units and ports.

| Seg-<br>ment | Address<br>Range                                   | Size        | Description                                     | DMI<br>Acc. | PMI<br>Acc. |                  |

|--------------|----------------------------------------------------|-------------|-------------------------------------------------|-------------|-------------|------------------|

| 0 – 7        | 0000 0000 <sub>H</sub> –<br>7FFF FFFF <sub>H</sub> | 2 GB        | MMU Space                                       | via FPI     | via<br>FPI  | с<br>а           |

| 8            | 8000 0000 <sub>H</sub> –<br>8FFF FFFF <sub>H</sub> | 256 MB      | External Memory Space<br>mapped from Segment 10 | via<br>LMB  | via<br>LMB  | C<br>h           |

| 9            | 9000 0000 <sub>H</sub> –<br>9FDF FFFF <sub>H</sub> | 256 MB      | Reserved                                        | via FPI     | via<br>FPI  | e<br>d           |

| 10           | A000 0000 <sub>H</sub> –<br>AFBF FFFF <sub>H</sub> | 252 MB      | External Memory Space                           | via<br>LMB  | via<br>LMB  | n<br>o           |

|              | AFC0 0000 <sub>H</sub> –<br>AFC0 FFFF <sub>H</sub> | 64 KB       | DMU Space                                       |             |             | n-<br>C          |

|              | AFC1 0000 <sub>H</sub> –<br>AFFF FFFF <sub>H</sub> | ~4 MB       | Reserved                                        |             |             | a<br>c<br>h      |

| 11           | B000 0000 <sub>H</sub> –<br>BFFF FFFF <sub>H</sub> | 256 MB      | Reserved                                        | via<br>FPI  | via<br>FPI  | e<br>d           |

| 12           | C000 0000 <sub>H</sub> –<br>C000 FFFF <sub>H</sub> | 64 KB       | DMU                                             | via<br>LMB  | via<br>LMB  | c<br>a           |

|              | C001 0000 <sub>H</sub> –<br>CFFF FFFF <sub>H</sub> | ~ 256<br>MB | Reserved                                        |             |             | c<br>h<br>e<br>d |

Table 3-1 TC1115 Block Address Map

#### **Functional Description**

# 3.7 Interrupt System

An interrupt request can be serviced by the CPU, which is called "Service Provider". Interrupt requests are referred to as "Service Requests" in this document.

Each peripheral in the TC1115 can generate service requests. Additionally, the Bus Control Unit, the Debug Unit, the DMA Controller and even the CPU itself can generate service requests to the Service Provider. As shown in **Figure 3-3**, each unit that can generate service requests is connected to one or multiple Service Request Nodes (SRN). Each SRN contains a Service Request Control Register mod\_SRC, where "mod" is the identifier of the unit requesting service. The SRNs are connected to the Interrupt Control Unit (ICU) via the CPU Interrupt Arbitration Bus. The ICU arbitrates service requests for the CPU and administers the Interrupt Arbitration Bus.

Units that can generate service requests are:

- Asynchronous/Synchronous Serial Interfaces (ASC0, ASC1 and ASC2) with 4 SRNs each

- High-Speed Synchronous Serial Interfaces (SSC0 and SSC1) with 3 SRNs each

- Inter IC Interface (IIC) with 3 SRNs

- Micro Link Interface MLI0 with 4 SRNs and MLI1 with 2 SRNs

- · General Purpose Timer Unit (GPTU) with 8 SRNs

- Capture/Compare Unit (CCU60 and CCU61) with 4 SRNs each

- MultiCAN (CAN) with 16 SRNs

- External Interrupts with 4 SRNs

- Direct Memory Access Controller (DMA) with 4 SRNs

- DMA Bus with 1 SRN

- System Timer (STM) with 2 SRNs

- Bus Control Units (SBCU and LBCU) with 1 SRN each

- Central Processing Unit (CPU) with 4 SRNs

- Floating Point Unit (FPU) with 1 SRN

- Debug Unit (OCDS) with 1 SRN

The CPU can make service requests directly to itself (via the ICU). The CPU Service Request Nodes are activated through software.

# **Functional Description**

- · Evaluation of the device address in slave mode

- · Bus access arbitration in multimaster mode

### Features:

- · Extended buffer allows up to 4 send/receive data bytes to be stored

- Selectable baud rate generation

- Support of standard 100 kBaud and extended 400 kBaud data rates

- Operation in 7-bit addressing mode or 10-bit addressing mode

- · Flexible control via interrupt service routines or by polling

- Dynamic access to up to 2 physical IIC buses

### **Functional Description**

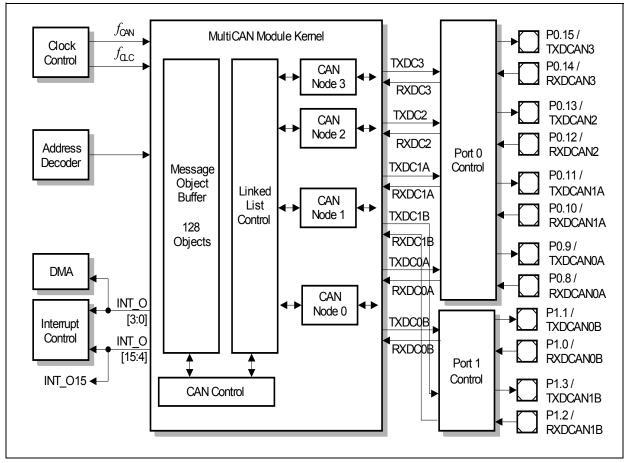

#### 3.12 MultiCAN

Figure 3-8 shows a global view of the functional blocks of the MultiCAN module.

Figure 3-8 General Block Diagram of the MultiCAN Interface

The MultiCAN module contains 4 Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list.

A powerful, command driven list controller performs all list operations.

# **Functional Description**

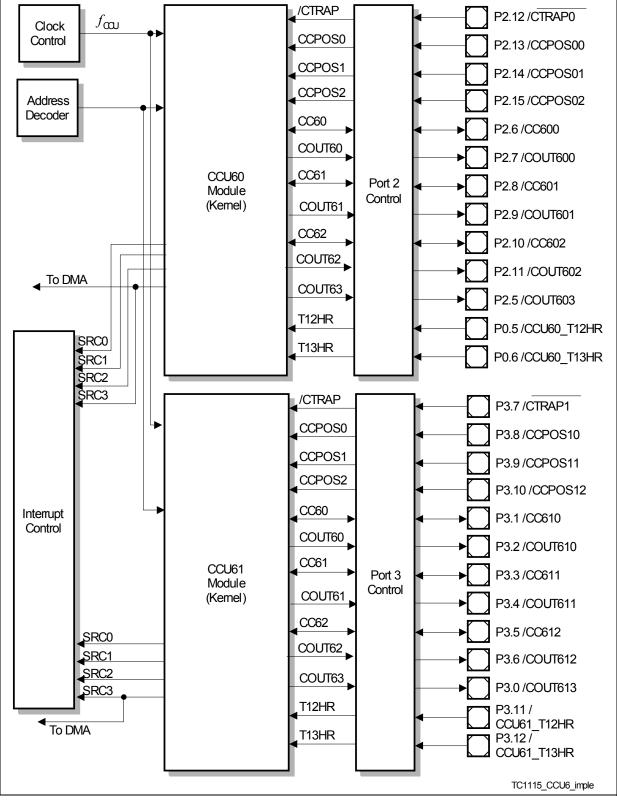

Figure 3-11 General Block Diagram of the CCU6 Interfaces

# TC1115

# Advance Information

# **Functional Description**

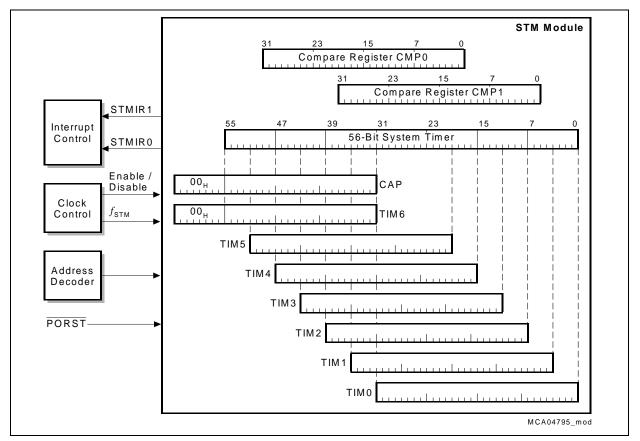

Figure 3-12 Block Diagram of the STM Module

### **Functional Description**

# 3.17 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failure. The WDT helps to abort an accidental malfunction of the TC1115 in a user-specified time period. When enabled, the WDT will cause the TC1115 system to be reset if the WDT is not serviced within a user-programmable time period. The CPU must service the WDT within this time interval to prevent the WDT from causing a TC1115 system reset. Hence, routine service of the WDT confirms that the system is functioning properly.

In addition to this standard "Watchdog" function, the WDT incorporates the ENDINIT feature and monitors its modifications. A system-wide line is connected to the ENDINIT bit implemented in a WDT control register, serving as an additional write-protection for critical registers (besides supervisor mode protection). Registers protected via this line can be modified only when supervisor mode is active and bit ENDINIT = 0.

A further enhancement in the TC1115's Watchdog Timer is its reset prewarning operation. Instead of immediately resetting the device upon detection of an error, the WDT first issues a Non-Maskable Interrupt (NMI) to the CPU before finally resetting the device at a specified time period later. This gives the CPU a chance to save system state to memory for later examination of the cause of the malfunction, thus providing an important aid in debugging.

### Features:

- 16-bit Watchdog counter

- Selectable input frequency:  $f_{SYS}/256 \text{ or } f_{SYS}/16384$

- 16-bit user-definable reload value for normal Watchdog operation, fixed reload value for time-out and prewarning modes

- Incorporation of the ENDINIT bit and monitoring of its modifications

- Sophisticated password access mechanism with fixed and user-definable password fields

- Proper access always requires two write accesses. The time between the two accesses is monitored by the WDT.

- Access Error Detection: Invalid password (during first access) or invalid guard bits (during second access) trigger the Watchdog reset generation.

- Overflow Error Detection: An overflow of the counter triggers the Watchdog reset generation.

- Watchdog function can be disabled; access protection and ENDINIT monitor function remain enabled.

- Double Reset Detection: If a Watchdog induced reset occurs twice without a proper access to its control register in between, a severe system malfunction is assumed and the TC1115 is held in reset until a power-on reset. This prevents the device from being periodically reset if, for instance, connection to the external memory has been lost such that even system initialization could not be performed.

### **Functional Description**

### 3.19 Boot Options

The TC1115 booting schemes provides a number of different boot options for the start of code execution. Table 3-3 shows the boot options available in the TC1115.

#### Table 3-3Boot Selections

| BRKIN <sup>1)</sup> | <b>TM</b> <sup>1)</sup> | HWCFG<br>[2:0] | Type of Boot                                                                              | PC Start Value<br>(User Entry)                                    |

|---------------------|-------------------------|----------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 1                   | 1                       | 000            | <b>Bootstrap Loader</b><br>Serial boot from ASC to PMI scratch<br>pad, run loaded program | DFFF FFFC <sub>H</sub> <sup>2)</sup><br>(D400 0000 <sub>H</sub> ) |

|                     |                         | 001            | <b>Bootstrap Loader</b><br>Serial boot from CAN to PMI scratch<br>pad, run loaded program |                                                                   |

|                     |                         | 010            | <b>Bootstrap Loader</b><br>Serial boot from SSC to PMI scratch<br>pad, run loaded program |                                                                   |

|                     |                         | 011            | External memory, EBU as master                                                            | DFFF FFFC <sub>H</sub> <sup>2)</sup><br>(A000 0000 <sub>H</sub> ) |

|                     |                         | 100            | External memory, EBU as slave                                                             | DFFF FFFC <sub>H</sub> <sup>2)</sup><br>(A000 0000 <sub>H</sub> ) |

|                     |                         | 101            | Reserved (STOP)                                                                           |                                                                   |

|                     |                         | 110            | PMI scratch pad                                                                           | D400 0000 <sub>H</sub>                                            |

|                     |                         | 111            | Reserved (STOP)                                                                           | DFFF FFFC <sub>H</sub> <sup>2)</sup>                              |

| 1                   | 0                       | 000-111        | Reserved (STOP)                                                                           | DFFF FFFC <sub>H</sub> <sup>2)</sup>                              |

| 0                   | 1                       | 000            | Tristate chip                                                                             |                                                                   |

|                     |                         | 001            | Go to external emulator space                                                             | DFFF FFFC <sub>H</sub> <sup>2)</sup><br>(DE00 0000 <sub>H</sub> ) |

|                     |                         | 010            | Reserved (STOP)                                                                           |                                                                   |

|                     |                         | 011            | OSC and PLL Bypass                                                                        |                                                                   |

|                     |                         | 100-111        | Reserved (STOP)                                                                           | DFFFFFFC <sub>H</sub> <sup>2)</sup>                               |

| 0                   | 0                       | 000-111        | Reserved (STOP)                                                                           | DFFFFFFC <sub>H</sub> <sup>2)</sup>                               |

<sup>1)</sup> This input signal is active low.

<sup>2)</sup> This is the BootROM entry address; the start address of user program in parentheses.

# **Functional Description**

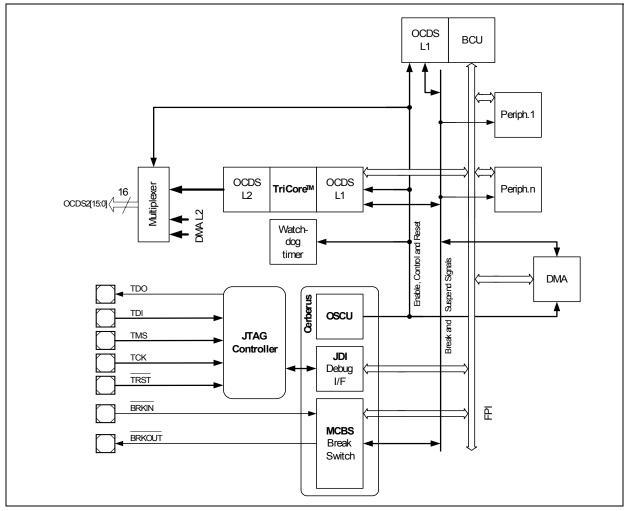

Figure 3-13 OCDS Support Basic Block Diagram

# **Functional Description**

### Table 3-5Load Capacitors Select (cont'd)

| Fundamental Mode Crystal Frequency<br>(approx., MHz) | Load Capacitors<br>C1, C2 (pF) |

|------------------------------------------------------|--------------------------------|

| 20                                                   | 10                             |

| 24                                                   | 10                             |

A block capacitor between  $V_{\rm DDOSC3}$  and  $V_{\rm SSOSC},~V_{\rm DDOSC}$  and  $V_{\rm SSOSC}$  is recommended, too.

#### **Electrical Parameters**

# 4.2.3 IIC Characteristics

Each IIC Pin is an open drain output pin with different characteristics than other pins. The related characteristics are given in the following table.

| Parameter                        | Syml            | bol | Limit Valu          | es                    | Unit | Test                                         |  |

|----------------------------------|-----------------|-----|---------------------|-----------------------|------|----------------------------------------------|--|

|                                  |                 |     | min. max.           |                       |      | Conditions                                   |  |

| Output low voltage               | V <sub>OL</sub> | CC  | _                   | 0.4<br>0.6            | V    | 3 mA sink<br>current<br>6 mA sink<br>current |  |

| Input high voltage <sup>1)</sup> | V <sub>IH</sub> | SR  | 0.7V <sub>DDP</sub> | V <sub>DDP</sub> +0.5 | V    | -                                            |  |

| Input low voltage <sup>1)</sup>  | V <sub>IL</sub> | SR  | -0.5                | 0.3V <sub>DDP</sub>   | V    | -                                            |  |

<sup>1)</sup> Not subject to production test, verified by design/characterization.

Note: No 5 V IIC interface is supported with these pads. Only voltages lower than 3.63 V must be applied to these pads.

Note: IIC pins have no pull-up and pull-down devices.

# TC1115

#### **Advance Information**

#### **Electrical Parameters**

### 4.2.4 Power Supply Current

| Parameter                | Symbol          | Limit V               | alues | Unit | Test Conditions                            |  |

|--------------------------|-----------------|-----------------------|-------|------|--------------------------------------------|--|

|                          |                 | typ. <sup>1)</sup> ma |       |      |                                            |  |

| Active mode supply       | I <sub>DD</sub> | 314                   | 679   | mA   | Sum of $I_{\text{DDS}}^{2)}$               |  |

| current                  |                 | 153                   | 345   | mA   | $I_{\rm DD}$ at $V_{\rm DD}$ <sup>3)</sup> |  |

|                          |                 | 156                   | 322   | mA   | $I_{\rm DD}$ at $V_{\rm DDP}$              |  |

| Idle mode supply current | I <sub>ID</sub> | 74                    | 154   | mA   | Sum of $I_{\text{DDS}}^{2)4)}$             |  |

|                          |                 | 66                    | 130   | mA   | $I_{\rm DD}$ at $V_{\rm DD}^{3)4)}$        |  |

|                          |                 | 6                     | 15    | mA   | $I_{\rm DD}$ at $V_{\rm DDP}^{4)}$         |  |

| Deep sleep mode supply   | I <sub>DS</sub> | 2                     | 19    | mA   | Sum of $I_{\text{DDS}}^{2)5)}$             |  |

| current                  |                 | 2                     | 19    | mA   | $I_{\rm DD}$ at $V_{\rm DD}{}^{3)5)}$      |  |

|                          |                 | 3.6                   | 58    | μA   | $I_{\rm DD}$ at $V_{\rm DDP}^{5)}$         |  |

<sup>1)</sup> Typical values are measured at 25°C, CPU clock at 150 MHz, and nominal supply voltage that is 3.3 V for V<sub>DDP</sub>, V<sub>DDOSC3</sub> and 1.5 V for V<sub>DD</sub>, V<sub>DDOSC</sub>. These currents are measured using a typical application pattern. The power consumption of modules can increase or decrease using other application programs.

<sup>2)</sup> These power supply currents are defined as the sum of all currents at the V<sub>DD</sub> power supply lines:  $V_{DD} + V_{DDP} + V_{DDOSC3} + V_{DDOSC}$

<sup>3)</sup> This measurement includes the TriCore<sup>TM</sup> and Logic power supply lines.

<sup>4)</sup> CPU is in idle state, input clocks to all peripherals are enabled.

<sup>5)</sup> Clock generation is disabled at the source.

# TC1115

# **Advance Information**

# **Electrical Parameters**

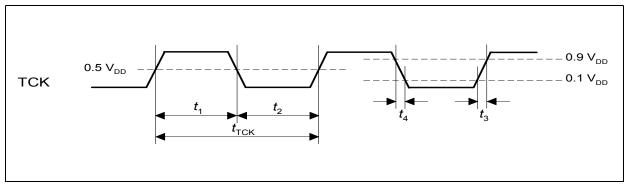

# 4.3.6 Timing for JTAG Signals

(Operating Conditions apply;  $C_{\rm L}$  = 50 pF)

| Parameter           | Symbol              | Limits |     | Unit |

|---------------------|---------------------|--------|-----|------|

|                     |                     | min    | max |      |

| TCK clock period    | t <sub>TCK</sub> SR | 50     | _   | ns   |

| TCK high time       | t <sub>1</sub> SR   | 10     | -   | ns   |

| TCK low time        | t <sub>2</sub> SR   | 29     | _   | ns   |

| TCK clock rise time | t <sub>3</sub> SR   | —      | 0.4 | ns   |

| TCK clock fall time | t <sub>4</sub> SR   | _      | 0.4 | ns   |

Figure 4-6 TCK Clock Timing

#### **Electrical Parameters**

### 4.3.8 EBU Timings

# 4.3.8.1 SDCLKO Output Clock Timing

(Operating Conditions apply; CL = 50 pF)

| Parameter        | Symbol            | Limits <sup>1)</sup> |     | Limits <sup>2)</sup> |     | Unit |  |

|------------------|-------------------|----------------------|-----|----------------------|-----|------|--|

|                  |                   | min                  | max | min                  | max |      |  |

| SDCLKO period    | t <sub>1</sub> CC | 10                   | _   | 8.3                  | -   | ns   |  |

| SDCLKO high time | t <sub>2</sub> CC | 3                    | _   | 2.5                  | _   | ns   |  |

| SDCLKO low time  | t <sub>3</sub> CC | 3                    | _   | 2.5                  | _   | ns   |  |

| SDCLKO rise time | t <sub>4</sub> CC | _                    | 2.5 | _                    | 2.5 | ns   |  |

| SDCLKO fall time | t <sub>5</sub> CC | _                    | 2.5 | _                    | 2.5 | ns   |  |

<sup>1)</sup> The parameters are applicable for PC100 SDRAM access and the maximum SDCLKO is up to 100 MHz.

<sup>2)</sup> The parameters are applicable for PC133 SDRAM access and the maximum SDCLKO is up to 120 MHz.

# 4.3.8.2 BFCLKO Output Clock Timing

(Operating Conditions apply;  $C_{L} = 50 \text{ pF}$ )

| Parameter        | Symbol                |    | Limit <sup>1)</sup> |     | Limit <sup>2)</sup> |     | Unit |  |

|------------------|-----------------------|----|---------------------|-----|---------------------|-----|------|--|

|                  |                       |    | min                 | max | min                 | max |      |  |

| Clock period     | <i>t</i> <sub>1</sub> | CC | 20                  | -   | 16.7                | -   | ns   |  |

| BFCLKO high time | <i>t</i> <sub>2</sub> | CC | 6.6                 | -   | 7.5                 | -   | ns   |  |

| BFCLKO low time  | <i>t</i> <sub>3</sub> | CC | 6.6                 | -   | 7.5                 | -   | ns   |  |

| BFCLKO rise time | <i>t</i> <sub>4</sub> | CC | -                   | 3.5 | -                   | 3.5 | ns   |  |

| BFCLKO fall time | <i>t</i> <sub>5</sub> | CC | -                   | 2.5 | -                   | 2.5 | ns   |  |

<sup>1)</sup> The CPU runs at 150 MHz and the Burst Flash runs at divided by 3 clock.

<sup>2)</sup> The CPU runs at 120 MHz and the Burst Flash runs at divided by 2 clock.

**Electrical Parameters**

# 4.3.9 Peripheral Timings

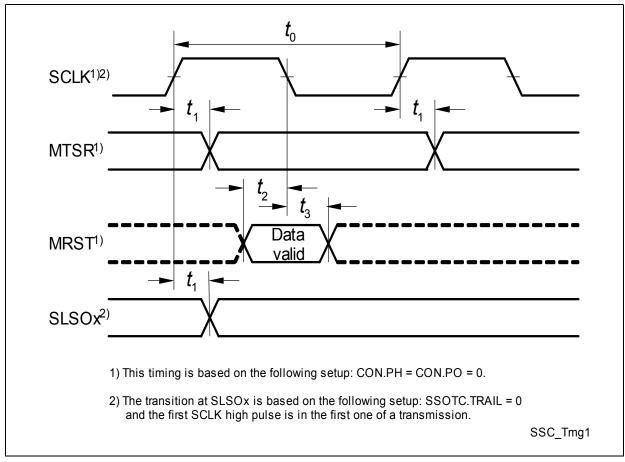

# 4.3.9.1 SSC Master Mode Timing

(Operating Conditions apply;  $C_{L}$  = 50 pF)

| Parameter                    |                       | Symbol | Limit Values          |      | Unit |

|------------------------------|-----------------------|--------|-----------------------|------|------|

|                              |                       |        | min.                  | max. |      |

| SCLK clock period            | <i>t</i> <sub>0</sub> | CC     | 2*T <sub>SSC</sub> 1) | _    | ns   |

| MTSR/SLSOx delay from SCLK 🖌 | <i>t</i> <sub>1</sub> | CC     | 0                     | 8    | ns   |

| MRST setup to SCLK -         | <i>t</i> <sub>2</sub> | SR     | 10                    | -    | ns   |

| MRST hold from SCLK -        | <i>t</i> <sub>3</sub> | SR     | 5                     | -    | ns   |

<sup>1)</sup>  $T_{SSCmin} = T_{SYS} = 1/f_{SYS}$ . When  $f_{SYS} = 120MHz$ ,  $t_0 = 16.7ns$

Figure 4-14 SSC Master Mode Timing

#### **Electrical Parameters**

TC1115

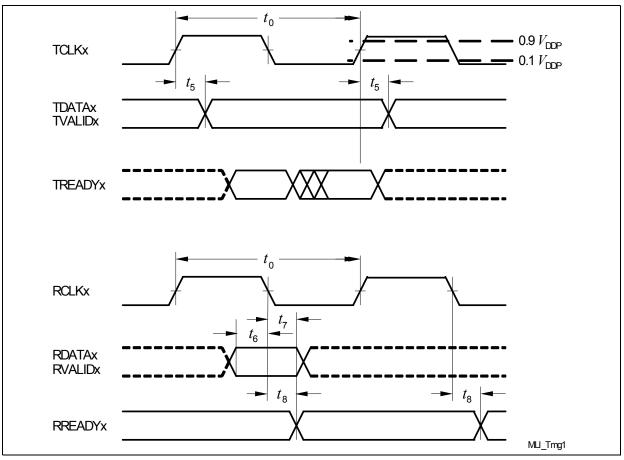

# 4.3.9.2 MLI Interface Timing

(Operating Conditions apply;  $C_{L} = 50 \text{ pF}$ )

| Parameter                       | Symbol                  | Limit Values                     |      | Unit |

|---------------------------------|-------------------------|----------------------------------|------|------|

|                                 |                         | min.                             | max. |      |

| TCLK/RCLK clock period          | t <sub>0</sub><br>CC/SR | 2*T <sub>MLI</sub> <sup>1)</sup> | -    | ns   |

| MLI outputs delay from TCLK 🦨   | t <sub>5</sub> CC       | 0                                | 8    | ns   |

| MLI inputs setup to RCLK 飞      | t <sub>6</sub> SR       | 4                                | -    | ns   |

| MLI inputs hold to RCLK -       | t <sub>7</sub> SR       | 4                                | -    | ns   |

| RREADY output delay from TCLK ٦ | t <sub>8</sub> CC       | 0                                | 8    | ns   |

<sup>1)</sup>  $T_{MLImin} = T_{SYS} = 1/f_{SYS}$ . When  $f_{SYS} = 120MHz$ ,  $t_0 = 16.7ns$

Figure 4-15 MLI Interface Timing

Note: The generation of RREADYx is in the input clock domain of the receiver. The reception of TREADYx is asynchronous to TCLKx.

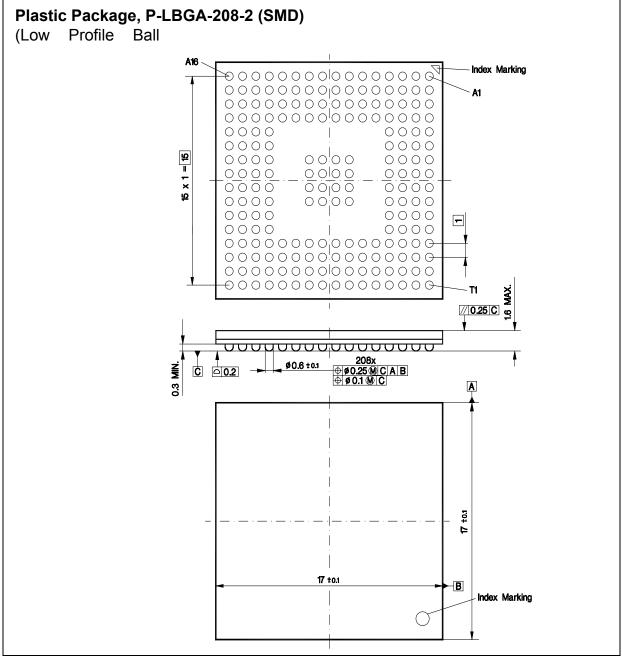

# Package Outline

TC1115

# 5 Package Outline

Figure 5-1 P-LBGA-208-2 Package

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

SMD = Surface Mounted Device

Dimensions in mm