#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

\* Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | TriCore™                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 100MHz                                                                            |

| Connectivity               | CANbus, EBIÆMI, FIFO, I²C, IrDA, SPI, UART/USART                                  |

| Peripherals                | DMA, POR, PWM, WDT                                                                |

| Number of I/O              | 72                                                                                |

| Program Memory Size        | -                                                                                 |

| Program Memory Type        | ROMIess                                                                           |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 144K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.43V ~ 1.58V                                                                     |

| Data Converters            | -                                                                                 |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package /Case              | 208-LBGA                                                                          |

| Supplier Device Package    | P-LBGA-208-2                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-tc1115-l100eb-g-bb |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Adibn          |                   |                 |                         |                                     | Gedelen                                                                                                 |

|----------------|-------------------|-----------------|-------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------|

| T <b>b</b> 2-1 | PiD <b>ieFi</b> o |                 |                         |                                     | (cont'd)                                                                                                |

| Sbyn Ph        | In                | Otu             | PU/<br>PD <sup>1)</sup> |                                     |                                                                                                         |

| P1.7           | B13               | l<br>O          | PUC                     | SWCFG7<br>OCDSA_7                   | Software configuration 7<br>OCDS L2 Debug Line A7                                                       |

| P1.8           | A13               | l<br>O          | PUC                     | SWCFG8<br>OCDSA_8                   | Software configuration 8<br>OCDS L2 Debug Line A8                                                       |

| P1.9           | A14               | l<br>O          | PUC                     | SWCFG9<br>OCDSA_9                   | Software configuration 9<br>OCDS L2 Debug Line A9                                                       |

| P1.10          | B14               | l<br>O          | PUC                     | SWCFG10<br>OCDSA_10                 | Software configuration 10<br>OCDS L2 Debug Line A10                                                     |

| P1.11          | C14               | <br>0<br>0      | PUC                     | SWCFG11<br>OCDSA_11<br>SLSO0 1      | Software configuration 11<br>OCDS L2 Debug Line A1<br>SSC0 Slave Select output 1                        |

| P1.12          | F13               | <br>0<br>0      | PUC                     | SWCFG12<br>OCDSA_12<br>SLSO1_1      | Software configuration 12<br>OCDS L2 Debug Line A12<br>SSC1 Slave Select output 1                       |

| P1.13          | E14               | <br>0<br>0      | PUC                     | SWCFG13<br>OCDSA_13<br>SLSO0_2      | Software configuration 13<br>OCDS L2 Debug Line A13<br>SSC0 Slave Select output 2                       |

| P1.14          | D14               | 0<br>I<br>0     | PUC                     | SLSO1_2<br>SWCFG14<br>OCDSA_14      | SSC1 Slave Select output 2<br>Software configuration 14<br>OCDS L2 Debug Line A14                       |

| P1.15          | F14               | <br>0<br> <br>0 | PUC                     | SLSI0<br>RMW<br>SWCFG15<br>OCDSA_15 | SSC0 Slave Select Input<br>EBU Read Modify Write<br>Software configuration 15<br>OCDS L2 Debug Line A15 |

## Adibn

G**bDidið**n

| T <b>b</b> 2-1 | PiD <b>ieFi</b> o |                  |                         |                                 | (cont'd)                                                                                                                |

|----------------|-------------------|------------------|-------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Sbyn Ph        | In                | Otu              | PU/<br>PD <sup>1)</sup> | Fib                             |                                                                                                                         |

| P3             |                   | I/O              |                         | Ptß                             |                                                                                                                         |

|                |                   |                  |                         | port which car                  | -bit bi-directional general purpose I/O<br>n be alternatively used for MLI1, CCU61,<br>DCDS Level 2 debug lines.        |

| P3.0           | A15               | 0                | PUC                     | OCDSB_0<br>COUT61_3             | OCDS L2 Debug Line B0                                                                                                   |

| P3.1           | B15               | 0<br>0<br>I/0    | PUC                     | OCDSB_1<br>CC61_0               | CCU61 compare channel 3 output<br>OCDS L2 Debug Line B1<br>CCU61 input/output of capture/                               |

| P3.2           | D15               | 0                | PUC                     | OCDSB_2<br>COUT61_0             | compare channel 0<br>OCDS L2 Debug Line B2<br>CCU61 output of capture/compare                                           |

| P3.3           | E15               | 0                | PUC                     | OCDSB_3                         | channel 0<br>OCDS L2 Debug Line B3                                                                                      |

|                |                   | I/O              |                         | CC61_1                          | CCU61 input/output of capture/<br>compare channel 1                                                                     |

| P3.4           | G14               | 0<br>0           | PUC                     | OCDSB_4<br>COUT61_1             | OCDS L2 Debug Line B4<br>CCU61 output of capture/compare                                                                |

| P3.5           | G15               | 0<br>I/O         | PUC                     | OCDSB_5<br>CC61_2               | channel 1<br>OCDS L2 Debug Line B5<br>CCU61 input/output of capture/                                                    |

| P3.6           | F15               | 0<br>0           | PUC                     | OCDSB_6<br>COUT61_2             | compare channel 2<br>OCDS L2 Debug Line B6<br>CCU61 output of capture/compare                                           |

| P3.7           | H14               | 0                | PUC                     | OCDSB_7<br>CTRAP1               | channel 2<br>OCDS L2 Debug Line B7<br>CCU61 trap input                                                                  |

| P3.8           | C15               | 0<br>0<br>1      | PUC                     | SLSO0_5<br>OCDSB_8<br>CCPOS1_0  | SSC0 Slave Select output 5<br>OCDS L2 Debug Line B8<br>CCU61 Hall input signal 0                                        |

| P3.9           | H15               | 0<br>0<br>0      | PUC                     | TCLK1<br>SLSO1_5<br>OCDSB_9     | MLI1 transmit channel clock output<br>SSC1 Slave Select output 5<br>OCDS L2 Debug Line B9                               |

|                |                   | <br> <br>        |                         | CCPOS1_1<br>TREADY1<br>SLSO0_6  | CCU61 Hall input signal 1<br>MLI1 transmit channel ready input                                                          |

| P3.10          | B16               | 0<br>0<br>1<br>0 | PUC                     | OCDSB_10<br>CCPOS1_2<br>TVALID1 | SSC0 Slave Select output 6<br>OCDS L2 Debug Line B10<br>CCU61 Hall input signal 2<br>MLI1 transmit channel valid output |

|                |                   | 0                |                         | SLSO1_6                         | SSC1 Slave Select output 6                                                                                              |

## Adibn

G**bDidið**n

| T <b>b</b> 2-1     | PiD <b>ie</b> Fie                                                                        |     |                         | (cont'd)                                   |

|--------------------|------------------------------------------------------------------------------------------|-----|-------------------------|--------------------------------------------|

| Sbyn Ph            | In                                                                                       | Otu | PU/<br>PD <sup>1)</sup> | Fib                                        |

| V <sub>SSOSC</sub> | L15                                                                                      |     |                         | MacOlaGd                                   |

| V <sub>DD</sub>    | G7<br>G8<br>G9<br>G10<br>G13<br>K7,K8<br>K9<br>K10                                       |     |                         | CeeLġPeSg(1.5V)                            |

| $V_{DDP}$          | D4<br>D13<br>H4<br>J13<br>M4<br>N13                                                      |     |                         | ₽ <b>₩₽₩₩</b> (3.3 V)                      |

| V <sub>SS</sub>    | E4<br>E13<br>H7<br>H8<br>H9<br>H10<br>H13<br>J4,J7<br>J8,J9<br>J10<br>M13<br>N4<br>R2,T2 |     |                         | Gd                                         |

| N.C.               | A1<br>A16<br>T1,R1<br>T14<br>T15<br>T16                                                  |     |                         | NtCtd<br>These pins must not be connected. |

1) Refers to internal pull-up or pull-down device connected and corresponding type. The notation '—' indicates that the internal pull-up or pull-down device is not enabled.

Note: P2.12 to P2.15 are always configured as open drain.

FildDip

## 3.2 A**s**Mp

TbB-1 defines the specific segment oriented address blocks of the TC1115 with its address range, size, and PMI/DMI access view. TbB-2 shows the block address map of the Segment 15 which includes on-chip peripheral units and ports.

Tb3-1 TC1115 BI bAd6Mp

| Sg<br>na | Ad<br>Da                                                 | Sie Di      | DMI                                             | Ac         | PMI<br>Ac  |                  |

|----------|----------------------------------------------------------|-------------|-------------------------------------------------|------------|------------|------------------|

|          | Rg<br>0000 0000 <sub>H</sub> –<br>7FFF FFFF <sub>H</sub> | 2 GB        | MMU Space                                       | via FPI    | via<br>FPI | c<br>a           |

| 8        | 8000 0000 <sub>H</sub> –<br>8FFF FFFF <sub>H</sub>       | 256 MB      | External Memory Space<br>mapped from Segment 10 | via<br>LMB | via<br>LMB | с<br>h           |

| 9        | 9000 0000 <sub>H</sub> –<br>9FDF FFFF <sub>H</sub>       | 256 MB      | Reserved                                        | via FPI    | via<br>FPI | e<br>d           |

| 10       | A000 0000 <sub>H</sub> –<br>AFBF FFFF <sub>H</sub>       | 252 MB      | External Memory Space                           | via<br>LMB | via<br>LMB | n<br>o           |

|          | AFC0 0000 <sub>H</sub> –<br>AFC0 FFFF <sub>H</sub>       | 64 KB       | DMU Space                                       |            |            | n-<br>c          |

|          | AFC1 0000 <sub>H</sub> –<br>AFFF FFFF <sub>H</sub>       | ~4 MB       | Reserved                                        |            |            | a<br>c<br>b      |

| 11       | B000 0000 <sub>H</sub> –<br>BFFF FFFF <sub>H</sub>       | 256 MB      | Reserved                                        | via<br>FPI | via<br>FPI | h<br>e<br>d      |

| 12       | C000 0000 <sub>H</sub> –<br>C000 FFFF <sub>H</sub>       | 64 KB       | DMU                                             | via<br>LMB | via<br>LMB | с<br>а           |

|          | C001 0000 <sub>H</sub> –<br>CFFF FFFF <sub>H</sub>       | ~ 256<br>MB | Reserved                                        |            |            | c<br>h<br>e<br>d |

Fildip

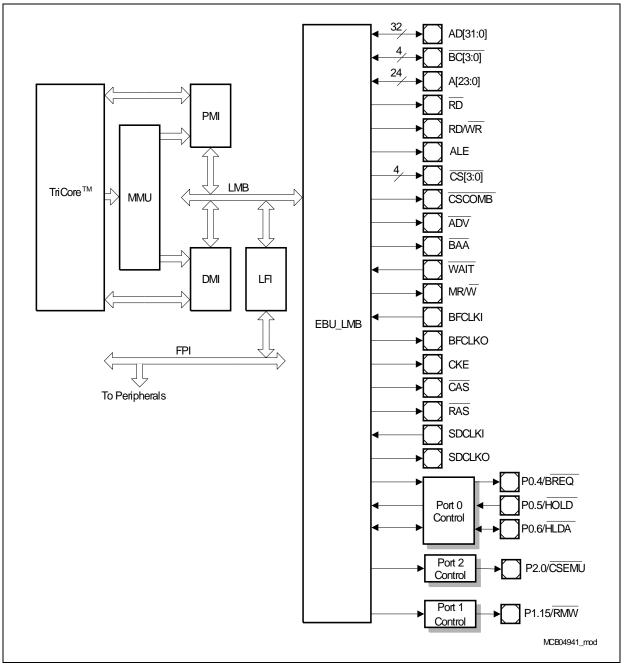

#### 3.5 LMB E kaBsUin

The LMB External Bus Control Unit (EBU) of the TC1115 is the interface between external resources, like memories and peripheral units, and the internal resources connected to on-chip buses if enabled. The basic structure and external interconnections of the EBU are shown in Figs-1

Figs-1 EBU Stelfe

FibDip

## 3.9 Abj6bj

## SHE(ASC)

Fig-5 shows a global view of the functional blocks of three Asynchronous/ Synchronous Serial interfaces (ASC0, ASC1 and ASC2).

Each ASC module (ASC0/ASC1/ASC2) communicates with the external world via one pair of I/O lines. The RXD line is the receive data input signal (in synchronous mode also output). TXD is the transmit output signal. Clock control, address decoding, and interrupt service request control are managed outside the ASC module kernel.

The Asynchronous/Synchronous Serial interfaces provide serial communication between the TC1115 and other microcontrollers, microprocessors or external peripherals.

Each ASC supports full-duplex asynchronous communication and half-duplex synchronous communication. In synchronous mode, data is transmitted or received synchronous to a shift clock which is generated by the ASC internally. In asynchronous mode, 8-bit or 9-bit data transfer, parity generation, and the number of stop bits can be selected. Parity, framing, and overrun error detection are provided to increase the reliability of data transfers. Transmission and reception of data is double-buffered. For multiprocessor communication, a mechanism is included to distinguish address bytes from data bytes. Testing is supported by a loop-back option. A 13-bit baud-rate generator provides the ASC with a separate serial clock signal that can be accurately adjusted by a prescaler implemented as a fractional divider.

FildDip

## 3.10 Htsp5p5bbf(SSC)

Fig-6 shows a global view of the functional blocks of two High-Speed Synchronous Serial interfaces (SSC0 and SSC1).

Each SSC supports full-duplex and half-duplex serial synchronous communication up to 37.5 MBaud (@ 75 MHz module clock) with receive and transmit FIFO support. The serial clock signal can be generated by the SSC itself (master mode) or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices. Transmission and reception of data is double-buffered. A shift clock generator provides the SSC with a separate serial clock signal. Eight slave select inputs are available for slave mode operation. Eight programmable slave select outputs (chip selects) are supported in master mode.

## Fe

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Automatic pad control possible

- Flexible data format

- Programmable number of data bits: 2 to 16 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Baud rate generation minimum at 572.2 Baud (@ 75 MHz module clock)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

- Four-pin interface

- Flexible SSC pin configuration

- Up to eight slave select inputs in slave mode

- · Up to eight programmable slave select outputs SLSO in master mode

- Automatic SLSO generation with programmable timing

- Programmable active level and enable control

- 4-stage receive FIFO (RXFIFO) and 4-stage transmit FIFO (TXFIFO)

- Independent control of RXFIFO and TXFIFO

- 2- to 16-bit FIFO data width

- Programmable receive/transmit interrupt trigger level

- Receive and transmit FIFO filling level indication

- Overrun error generation

- Underflow error generation

FildDip

- Evaluation of the device address in slave mode

- Bus access arbitration in multimaster mode

#### Fe

- Extended buffer allows up to 4 send/receive data bytes to be stored

- Selectable baud rate generation

- Support of standard 100 kBaud and extended 400 kBaud data rates

- Operation in 7-bit addressing mode or 10-bit addressing mode

- · Flexible control via interrupt service routines or by polling

- Dynamic access to up to 2 physical IIC buses

#### FibDip

The Micro Link Serial Bus Interface is dedicated to the serial communication between the other Infineon 32-bit controllers with MLI. The communication is intended to be fast due to an address translation system, and it is not necessary to have any special program in the second controller.

#### FØ

- Serial communication from the MLI transmitter to MLI receiver of another controller

- Module supports connection of each MLI with up to four MLI from other controllers

- Fully transparent read/write access supported (= remote programming)

- Complete address range of target controller available

- Special protocol to transfer data, address offset, or address offset and data

- Error control using a parity bit

- 32-bit, 16-bit, and 8-bit data transfers

- Address offset width: from 1- to 16-bit

- Baud rate:  $f_{\rm MLI}$  / 2 (symmetric shift clock approach), baud rate definition by the corresponding fractional divider

Fildip

#### Adib

Fibbib

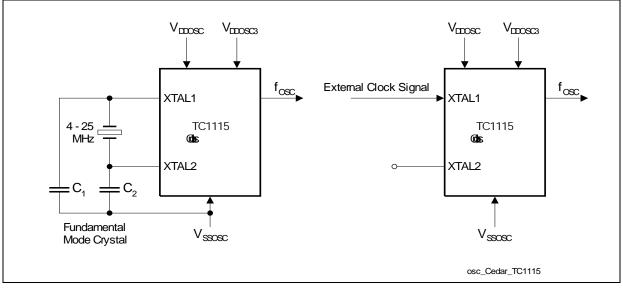

The oscillator circuit, which is designed to work with an external crystal oscillator or an external stable clock source, consists of an inverting amplifier with XTAL1 as input and XTAL2 as output.

Fig8-15 shows the recommended external oscillator circuitries for both operating modes, i.e. external crystal mode and external input clock mode.

#### Fig8-15 OLCE

When using an external clock signal, it must be connected to XTAL1 and XTAL2 is left open (unconnected). When supplying the clock signal directly, not using a crystal and the oscillator, the input frequency can be in the range of 0 - 40 MHz if the PLL is not used, 4 - 40 MHz in case the PLL is used.

When using a crystal, its frequency can be within the range of 4 MHz to 25 MHz. An external oscillator load circuitry must be used, connected to both pins, XTAL1 and XTAL2. It consists normally of the two load capacitances, C1 and C2. For some crystals, a series damp resistor may be necessary. The exact values and related operating range are dependant on the crystal and have to be determined and optimized together with the crystal vendor using the negative resistance method. As starting point for the evaluation and for non-productive systems, the following load capacitor values might be used.

| 168-2 L60-140       | e      |                            |

|---------------------|--------|----------------------------|

| F#bx1eJ<br>(p) MH)≿ | CNJF99 | L <b>dCþ</b><br>C1, C2 (þ) |

| 4                   |        | 33                         |

| 8                   |        | 18                         |

| 12                  |        | 12                         |

| 16                  |        | 10                         |

| Cipise |

|--------|

|        |

TC1115

E**lePe**n

## 4.1.2 AbMaRig

| Pan Sayn L                                                        | ith∕ba Uit              | n Nes  |     |     |            |

|-------------------------------------------------------------------|-------------------------|--------|-----|-----|------------|

|                                                                   |                         | in nan |     |     |            |

| Ambient temperature                                               | T <sub>A</sub>          | -40    | 85  | °C  | under bias |

| Storage temperature                                               | T <sub>ST</sub>         | -65    | 150 | °C  | _          |

| Junction temperature                                              | TJ                      | -40    | 125 | °C  | under bias |

| Voltage at 1.5 V power supply pins with respect to $V_{SS}^{(1)}$ | V <sub>DD</sub>         | -0.5   | 1.7 | V   | -          |

| Voltage at 3.3 V power supply pins with respect to $V_{SS}^{(2)}$ | V <sub>DDP</sub>        | -0.5   | 4.0 | V   | -          |

| Voltage on any pin with respect to $V_{\rm SS}{}^{2)}$            | V <sub>IN</sub>         | -0.5   | 4.0 | V   | -          |

| Input current on any pin during overload condition                | I <sub>IN</sub>         | -10    | 10  | mA  | -          |

| Absolute sum of all input currents during overload condition      | $\Sigma I_{\rm IN}$     | -      | 100 | mA  | _          |

| CPU & LMB Bus Frequency                                           | fsys                    | _      | 150 | MHz | -          |

| FPI Bus Frequency                                                 | <i>f</i> <sub>FPI</sub> | _      | 100 | MHz | -          |

<sup>1)</sup> Applicable for  $V_{\text{DD}}$  and  $V_{\text{DDOSC}}$ .

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

<sup>&</sup>lt;sup>2)</sup> Applicable for  $V_{\text{DDP}}$  and  $V_{\text{DDOSC3}}$ . The maximum voltage difference must not exceed 4.0 V in any case (i.e. Supply Voltage = 4.0 V and Input Voltage = -0.5 V is not allowed).

#### Adibn

E**l₽₽**

4.2 DC P**b**n

4.2.1 Inton C b

## $V_{SS} = 0 V; T_A = -40^{\circ}C \text{ to } +125^{\circ}C$

| P <b>e</b> n | Skyn | Lita/bi |    | 6   | Uin Te£Cit |  |

|--------------|------|---------|----|-----|------------|--|

|              |      |         | 'n | BAN |            |  |

## GPIO pi Dip EBU pi

| Input low voltage               | V <sub>IL</sub> SR   | -0.3 | 0.8                       | V  | LvTTL                                |

|---------------------------------|----------------------|------|---------------------------|----|--------------------------------------|

| Input high voltage              | V <sub>IH</sub> SR   | 2.0  | V <sub>DDP</sub> +<br>0.3 | V  | LvTTL                                |

| Output low voltage              | V <sub>OL</sub> CC   | -    | 0.4                       | V  | $I_{OL} = 2mA$                       |

| Output high voltage             | V <sub>OH</sub> CC   | 2.4  | -                         | V  | I <sub>OH</sub> = -2mA               |

| Pull-up current <sup>1)</sup>   | I <sub>PUA</sub>  CC | -    | 149                       | μA | $V_{IN} = 0V$                        |

|                                 | I <sub>PUC</sub>  CC | _    | 7.2                       | μA | $V_{IN} = 0V$                        |

| Pull-down current <sup>2)</sup> | I <sub>PDA</sub>  CC | _    | 156                       | μA | $V_{IN} = V_{DDP}$                   |

|                                 | I <sub>PDC</sub>  CC | -    | 15.7                      | μA | $V_{IN} = V_{DDP}$                   |

| Input leakage current 3)        | I <sub>OZ1</sub> CC  | -    | ±350                      | nA | $0 < V_{IN} < V_{DDP}$               |

| Pin Capacitance <sup>4)</sup>   | C <sub>IO</sub> CC   | _    | 10                        | pF | f = 1  MHz<br>T <sub>A</sub> = 25 °C |

<sup>1)</sup> The current is applicable to the pins, for which a pull-up has been specified. Refer to Tb2-1 .  $I_{PUx}$  refers to the pull-up current for type *x* in absolute values.

<sup>2)</sup> The current is applicable to the pins, for which a pull-down has been specified. Refer to T $\pounds$ 2-1 .  $I_{PDx}$  refers to the pull-down current for type *x* in absolute values.

<sup>3)</sup> Excluded following pins: NMI, TRST, TCK, TDI, TMS, ALE, P2.1, HWCFG0, HWCFG1, HWCFG2, BRKIN, PORST, HDRST.

<sup>4)</sup> Not subject to production test, verified by design/characterization

## Adibn

E**l₽e**n

4.3 AC Pin

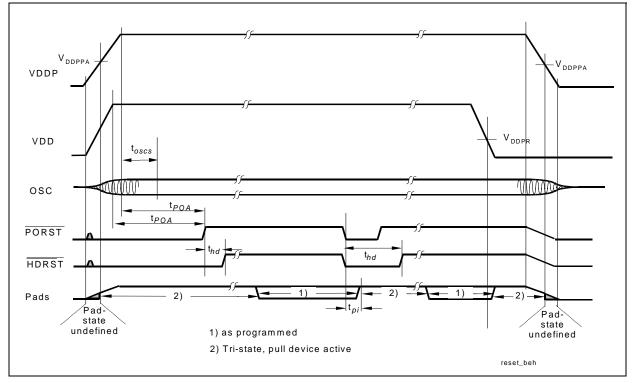

## 4.3.1 PpePetReTign

| Pan Sayn                                                                      | Litt/a                   | Uin                          |   |    |      |

|-------------------------------------------------------------------------------|--------------------------|------------------------------|---|----|------|

|                                                                               |                          | 'n                           | B |    |      |

| Min. $V_{\text{DDP}}$ voltage to ensure defined pad states <sup>1)</sup>      | V <sub>DDPPA</sub><br>CC | 0.6                          |   | -  | V    |

| Oscillator start-up time <sup>2)</sup>                                        | t <sub>OSCS</sub> CC     | -                            |   | 30 | ms   |

| Minimum PORST active time after power supplies are stable at operating levels | t <sub>POA</sub> CC      | 50                           |   | -  | ms   |

| HDRST pulse width                                                             | t <sub>HD</sub> CC       | 1024<br>cycles <sup>3)</sup> |   |    | fsys |

| Ports inactive after any reset active <sup>2)</sup>                           | t <sub>PI</sub> CC       | -                            |   | 30 | ns   |

<sup>1)</sup> This parameter is valid under assumption that PORST signal is constantly at low level during the power-up/ power-down of the  $V_{\text{DDP}}$ .

<sup>2)</sup> Not subject to production test, verified by design/characterization.

<sup>3)</sup> Any HDRST activation is internally prolonged to 1024 FPI bus clock cycles.

## Adibn

E**lePe**n

Fig4-1 PoorRoETign

E**l₽**en

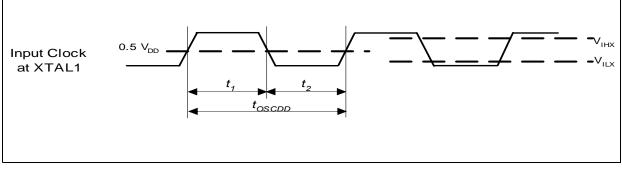

# 4.3.4 IptCkoTign

(Operating Conditions apply)

| Pan                                    | Skyn     | Lian Uin         |        |    |     |

|----------------------------------------|----------|------------------|--------|----|-----|

|                                        |          |                  | in par | )  |     |

| Oscillator clock frequency             | with PLL | $f_{\rm OSC}$ SR | 4      | 25 | MHz |

| Input clock frequency driving at XTAL1 | with PLL | foscdd<br>SR     | -      | 40 | MHz |

| Input Clock Duty Cycle $(t_1 / t_2)$   | ·        | SR               | 45     | 55 | %   |

## Fig4-4 lptCkoTign

TC1115

E**l₽₽**€n

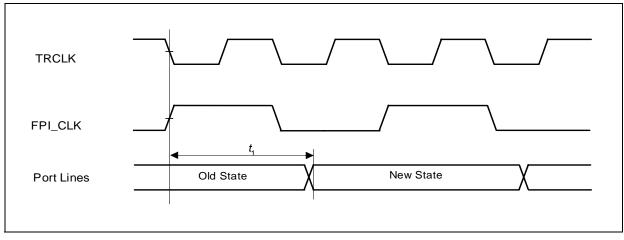

# 4.3.5 Polīgn

(Operating Conditions apply;  $C_{L} = 50 \text{ pF}$ )

| Pan Sayn                                                             | Lin                   | Uin |    |     |    |    |

|----------------------------------------------------------------------|-----------------------|-----|----|-----|----|----|

|                                                                      |                       |     | 'n | BAN |    |    |

| Port data valid from TRCLK <sup>1)</sup> up to 120 MHz <sup>2)</sup> | <i>t</i> <sub>1</sub> | CC  | _  |     | 13 | ns |

<sup>1)</sup> Port data is output with respect to the FPI clock. The TRCLK is used as a reference here since the FPI clock is not available as an external pin and TRCLK is same frequency as CPU clock. Port lines maintain their states for at least 2 CPU clocks.

<sup>2)</sup> 120 MHz is verified by design/characterization.

Fig4-5 PoTign

#### Adibn

E**lePe**n

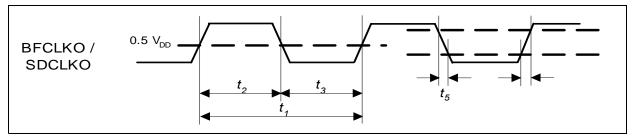

## Fig4-9 EBU CkOpTign

## 4.3.8.3 TigoSDRAM AsSig

(Operating Conditions apply;  $C_{L} = 50 \text{ pF}^{1}$ )

| Patan Sbyn Libn                                               |                        |    |         | 2)   | Lian | 3)  | Uint |

|---------------------------------------------------------------|------------------------|----|---------|------|------|-----|------|

|                                                               |                        |    | impenin | nzan |      |     |      |

| SDCLKO period                                                 | <i>t</i> <sub>1</sub>  | CC | 10      | -    | 8.3  | -   | ns   |

| CKE output valid time from SDCLKO 🦨                           | <i>t</i> <sub>1</sub>  | CC | -       | 8.0  | -    | 6.8 | ns   |

| CKE output hold time from SDCLKO _                            | <i>t</i> <sub>2</sub>  | CC | 0       | _    | 0.8  | _   | ns   |

| Address output valid time from SDCLKO 🦨                       | <i>t</i> <sub>3</sub>  | CC | -       | 8.0  | -    | 6.8 | ns   |

| Address output hold time from SDCLKO 🦵                        | <i>t</i> <sub>4</sub>  | CC | 1.0     | -    | 0.8  | -   | ns   |

| CSx, RAS, CAS, RD/WR, BC(3:0) output valid time from SDCLKO _ | t <sub>5</sub>         | CC | _       | 8.0  | -    | 6.8 | ns   |

| CSx, RAS, CAS, RD/WR, BC(3:0) output hold time from SDCLKO _  | <i>t</i> <sub>6</sub>  | CC | 1.0     | _    | 0.8  | _   | ns   |

| AD(31:0) output valid time from SDCLKO 🖌                      | <i>t</i> <sub>7</sub>  | CC | -       | 8.0  | _    | 6.8 | ns   |

| AD(31:0) output hold time from SDCLKO 🖌                       | <i>t</i> <sub>8</sub>  | CC | 1.0     | _    | 0.8  | _   | ns   |

| AD(31:0) input setup time to SDCLKO _                         | t <sub>9</sub>         | SR | 4.0     | -    | 2.9  | -   | ns   |

| AD(31:0) input hold time from SDCLKO _                        | <i>t</i> <sub>10</sub> | SR | 3.0     | _    | 3.0  | _   | ns   |

1) If application conditions other than 50 pf capacitive load are used, then the proper correlation factor should be used for your specific application condition. For design team, the load should be set according to the system requirement.

2) The parameters are applicable for PC100 SDRAM access and the maximum SDCLKO is up to 100 MHz.

3) The parameters are applicable for PC133 SDRAM access and the maximum SDCLKO is up to 120 MHz.

#### Adibn

Pkph

# 5 PgOb

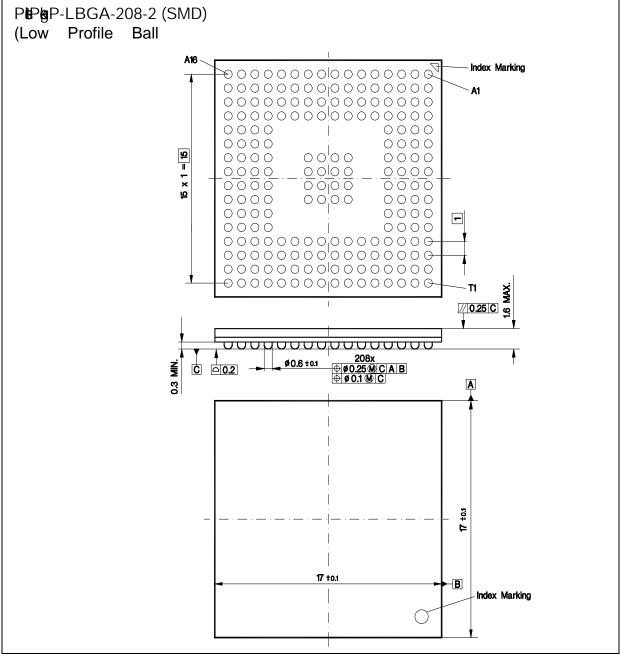

Fig5-1 P-LBGA-208-2 Pig

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

#### SMD = Surface Mounted Device

Dimensions in mm