#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | TriCore™                                                                        |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 150MHz                                                                          |

| Connectivity               | CANbus, EBI/EMI, FIFO, I <sup>2</sup> C, IrDA, SPI, UART/USART                  |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 72                                                                              |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 144K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.43V ~ 1.58V                                                                   |

| Data Converters            | -                                                                               |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 208-LBGA                                                                        |

| Supplier Device Package    | P-LBGA-208-2                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-tc1115-l150eb-bb |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TC1115 32-Bit Single-Chip Microcontroller Advance Information

## Microcontrollers

Never stop thinking.

#### **General Device Information**

#### Table 2-1Pin Definitions and Functions (cont'd)

| Symbol                                        | Pin                  | In<br>Out   | PU/<br>PD <sup>1)</sup>  | Functions                                                                                                                                                                                                             |

|-----------------------------------------------|----------------------|-------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>CS0</u><br><u>CS1</u><br><u>CS2</u><br>CS3 | D9<br>D8<br>C9<br>B8 | 0<br>0<br>0 | PUC<br>PUC<br>PUC<br>PUC | EBU Chip Select Output Line 0<br>EBU Chip Select Output Line 1<br>EBU Chip Select Output Line 2<br>EBU Chip Select Output Line 3<br>Each corresponds to a programmable region. Only<br>one can be active at one time. |

| CSCOMB                                        | N3                   | 0           | PUC                      | EBU Chip Select Output for combination function (Overlay Memory and Global)                                                                                                                                           |

| SDCLKI                                        | J1                   | I           |                          | SDRAM Clock Input (Clock Feedback)                                                                                                                                                                                    |

| SDCLKO                                        | H1                   | 0           |                          | <b>SDRAM Clock Output</b><br>Accesses to SDRAM devices are synchronized to this clock.                                                                                                                                |

| RAS                                           | D6                   | 0           | PUC                      | EBU SDRAM Row Address Strobe Output                                                                                                                                                                                   |

| CAS                                           | D5                   | 0           | PUC                      | EBU SDRAM Column Address Strobe Output                                                                                                                                                                                |

| CKE                                           | L4                   | 0           | PUC                      | EBU SDRAM Clock Enable Output                                                                                                                                                                                         |

| BFCLKI                                        | D1                   | I           |                          | Burst Flash Clock Input (Clock Feedback)                                                                                                                                                                              |

| BFCLKO                                        | E1                   | 0           |                          | <b>Burst Flash Clock Output</b><br>Accesses to Burst Flash devices are synchronized to<br>this clock.                                                                                                                 |

| RD                                            | P2                   | 0           | PUC                      | EBU Read Control Line<br>Output in master mode<br>Input in slave mode                                                                                                                                                 |

| RD/WR                                         | Т3                   | 0           | PUC                      | <b>EBU Write Control Line</b><br>Output in master mode<br>Input in slave mode                                                                                                                                         |

| WAIT                                          | B9                   | Ι           | PUC                      | EBU Wait Control Line                                                                                                                                                                                                 |

| ALE                                           | R3                   | 0           | PDC                      | EBU Address Latch Enable Output                                                                                                                                                                                       |

| MR/W                                          | P3                   | 0           | PUC                      | EBU Motorola-style Read/Write Output                                                                                                                                                                                  |

| BAA                                           | A11                  | 0           | PUC                      | EBU Burst Address Advance Output<br>For advancing address in a Burst Flash access                                                                                                                                     |

| ADV                                           | B11                  | 0           | PUC                      | EBU Burst Flash Address Valid Output                                                                                                                                                                                  |

#### **General Device Information**

| Table 2-1 | Pin Definitions and Functions | (conťd) |

|-----------|-------------------------------|---------|

|-----------|-------------------------------|---------|

| Symbol              | Pin        | In<br>Out | PU/<br>PD <sup>1)</sup> | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|------------|-----------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |            |           |                         | EBU Address Bus Input/Output Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A0                  | K1         | 0         | PUC                     | EBU Address Bus Line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A1                  | L1         | 0         | PUC                     | EBU Address Bus Line 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A2                  | M1         | 0         | PUC                     | EBU Address Bus Line 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A3                  | N1         | 0         | PUC                     | EBU Address Bus Line 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A4                  | P1         | 0         | PUC                     | EBU Address Bus Line 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A5                  | J2         | 0         | PUC                     | EBU Address Bus Line 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A6                  | K2         | 0         | PUC                     | EBU Address Bus Line 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A7                  | L2         | 0         | PUC                     | EBU Address Bus Line 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A8                  | M2         | 0         | PUC                     | EBU Address Bus Line 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A9                  | N2         | 0         | PUC                     | EBU Address Bus Line 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A10                 | J3         | 0         | PUC                     | EBU Address Bus Line 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A11                 | K3         | 0         | PUC                     | EBU Address Bus Line 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A12                 | L3         | 0         | PUC                     | EBU Address Bus Line 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A13                 | M3         | 0         | PUC                     | EBU Address Bus Line 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A14                 | K4         | 0         | PUC                     | EBU Address Bus Line 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A15                 | A8         | 0         | PUC                     | EBU Address Bus Line 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A16                 | A9         | 0         | PUC                     | EBU Address Bus Line 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A17                 | A10        | 0         | PUC                     | EBU Address Bus Line 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A18                 | B10        | 0         | PUC                     | EBU Address Bus Line 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A19                 | C10        | 0         | PUC                     | EBU Address Bus Line 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A20                 | D10        | 0         | PUC                     | EBU Address Bus Line 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A21                 | T4         | 0         | PUC                     | EBU Address Bus Line 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A22                 | R4         | 0         | PUC                     | EBU Address Bus Line 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A23                 | P4         | 0         | PUC                     | EBU Address Bus Line 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL1<br>XTAL2      | M16<br>N16 | I<br>O    |                         | <b>Oscillator/PLL/Clock Generator Input/Output Pins</b><br>XTAL1 is the input to the main oscillator amplifier and<br>input to the internal clock generator. XTAL2 is the<br>output of the main oscillator amplifier circuit. For<br>clocking of the device from an external source, XTAL1<br>is driven with the clock signal while XTAL2 is left<br>unconnected. For crystal oscillator operation, XTAL1<br>and XTAL2 are connected to the crystal with the<br>appropriate recommended oscillator circuitry. |

| V <sub>DDOSC3</sub> | P16        | <u> </u>  | <u> </u>                | Main Oscillator Power Supply (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SSOSC3</sub> | R16        | <u> </u>  |                         | Main Oscillator Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>DDOSC</sub>  | L16        |           |                         | Main Oscillator Power Supply (1.5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### **Functional Description**

#### Table 3-2Block Address Map of Segment 15 (cont'd)

| Symbol       | Description                  | Address Range                                   | Size      |

|--------------|------------------------------|-------------------------------------------------|-----------|

| Зушрог       | •                            | U                                               | Size      |

|              | Reserved                     | F010 0700 <sub>H</sub> - F010 BFFF <sub>H</sub> | -         |

| MLIO         | Micro Link Interface 0       | F010 C000 <sub>H</sub> - F010 C0FF <sub>H</sub> |           |

| MLI1         | Micro Link Interface 1       | F010 C100 <sub>H</sub> - F010 C1FF <sub>H</sub> | 256 Bytes |

| MCHK         | Memory Checker               | F010 C200 <sub>H</sub> - F010 C2FF <sub>H</sub> | 256 Bytes |

| _            | Reserved                     | F010 C300 <sub>H</sub> - F01D FFFF <sub>H</sub> | _         |

| MLI0_<br>SP0 | MLI0 Small Transfer Window 0 | F01E 0000 <sub>H</sub> - F01E 1FFF <sub>H</sub> | 8 Kbytes  |

| MLI0_<br>SP1 | MLI0 Small Transfer Window 1 | F01E 2000 <sub>H</sub> - F01E 3FFF <sub>H</sub> | 8 Kbytes  |

| MLI0_<br>SP2 | MLI0 Small Transfer Window 2 | F01E 4000 <sub>H</sub> - F01E 5FFF <sub>H</sub> | 8 Kbytes  |

| MLI0_<br>SP3 | MLI0 Small Transfer Window 3 | F01E 6000 <sub>H</sub> - F01E 7FF <sub>H</sub>  | 8 Kbytes  |

| MLI1_<br>SP0 | MLI1 Small Transfer Window 0 | F01E 8000 <sub>H</sub> - F01E 9FFF <sub>H</sub> | 8 Kbytes  |

| MLI1_<br>SP1 | MLI1 Small Transfer Window 1 | F01E A000 <sub>H</sub> - F01E BFFF <sub>H</sub> | 8 Kbytes  |

| MLI1_<br>SP2 | MLI1 Small Transfer Window 2 | F01E C000 <sub>H</sub> - F01E DFFF <sub>H</sub> | 8 Kbytes  |

| MLI1_<br>SP3 | MLI1 Small Transfer Window 3 | F01E E000 <sub>H</sub> - F01E FFF <sub>H</sub>  | 8 Kbytes  |

| _            | Reserved                     | F01F 0000 <sub>H</sub> - F01F FFFF <sub>H</sub> | _         |

| MLI0_<br>LP0 | MLI0 Large Transfer Window 0 | F020 0000 <sub>H</sub> - F020 FFFF <sub>H</sub> | 64 Kbytes |

| MLI0_<br>LP1 | MLI0 Large Transfer Window 1 | F021 0000 <sub>H</sub> - F021 FFFF <sub>H</sub> | 64 Kbytes |

| MLI0_<br>LP2 | MLI0 Large Transfer Window 2 | F022 0000 <sub>H</sub> - F022 FFFF <sub>H</sub> | 64 Kbytes |

| MLI0_<br>LP3 | MLI0 Large Transfer Window 3 | F023 0000 <sub>H</sub> - F023 FFFF <sub>H</sub> | 64 Kbytes |

| MLI1_<br>LP0 | MLI1 Large Transfer Window 0 | F024 0000 <sub>H</sub> - F024 FFFF <sub>H</sub> | 64 Kbytes |

| MLI1_<br>LP1 | MLI1 Large Transfer Window 1 | F025 0000 <sub>H</sub> - F025 FFFF <sub>H</sub> | 64 Kbytes |

#### **Functional Description**

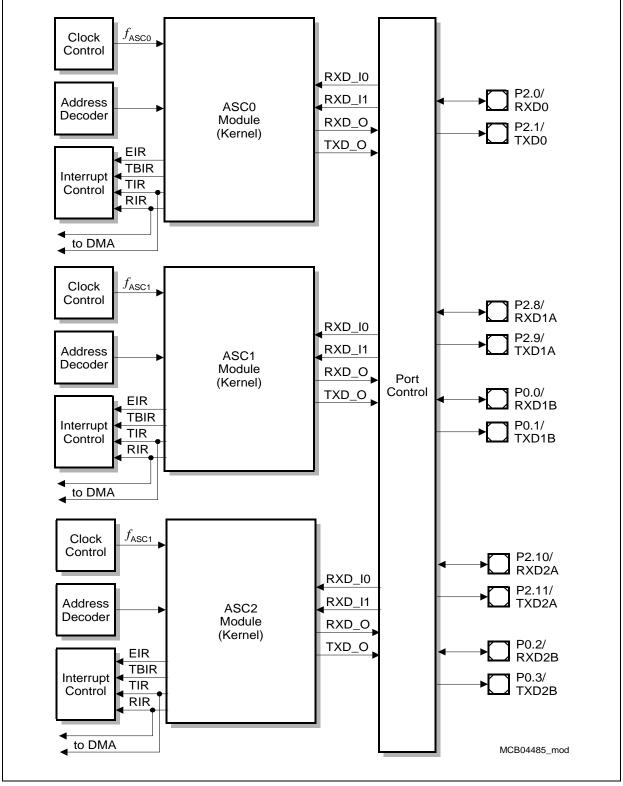

Figure 3-5 General Block Diagram of the ASC Interfaces

#### **Functional Description**

#### Features:

- · Full-duplex asynchronous operating modes

- 8-bit or 9-bit data frames, LSB first

- Parity bit generation/checking

- One or two stop bits

- Baud rate from 4.6875 MBaud to 1.1 Baud (@ 75 MHz clock)

- Multiprocessor mode for automatic address/data byte detection

- · Loop-back capability

- Half-duplex 8-bit synchronous operating mode

Baud rate from 9.375 MBaud to 762.9 Baud (@ 75 MHz clock)

- Support for IrDA data transmission up to 115.2 kBaud maximum

- Double buffered transmitter/receiver

- Interrupt generation

- On a transmitter buffer empty condition

- On a transmit last bit of a frame condition

- On a receiver buffer full condition

- On an error condition (frame, parity, overrun error)

- FIFO

- 8-byte receive FIFO (RXFIFO)

- 8-byte transmit FIFO (TXFIFO)

- Independent control of RXFIFO and TXFIFO

- 9-bit FIFO data width

- Programmable Receive/Transmit Interrupt Trigger Level

- Receive and Transmit FIFO filling level indication

- Overrun error generation

- Underflow error generation

#### **Functional Description**

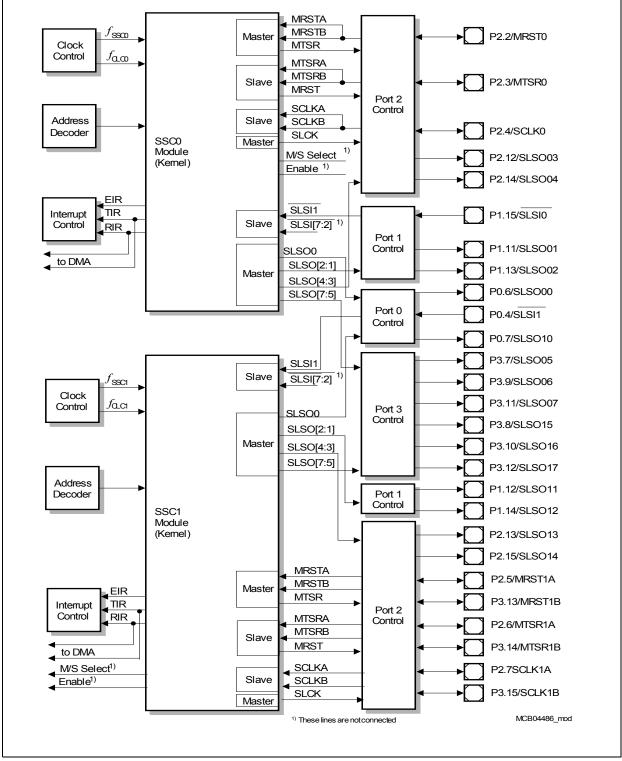

Figure 3-6 General Block Diagram of the SSC Interfaces

#### **Functional Description**

- Static Allocation Commands offer compatibility with TwinCAN applications, which are not list based.

- Advanced Interrupt Handling:

- Up to 16 interrupt output lines are available. Most interrupt requests can be individually routed to one of the 16 interrupt output lines.

- Message postprocessing notifications can be flexibly aggregated into a dedicated register field of 256 notification bits.

#### TC1115

#### **Functional Description**

#### 3.15 Capture/Compare Unit 6 (CCU6)

**Figure 3-11** shows a global view of the functional blocks of two Capture/Compare Units (CCU60 and CCU61).

Both of the CCU6 modules are further supplied by clock control, interrupt control, address decoding, and port control logic. One DMA request can be generated by each CCU6 module.

Each CCU6 provides two independent timers (T12, T13), which can be used for PWM generation, especially for AC-motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

#### Timer 12 Features:

- Three capture/compare channels, each channel can be used either as capture or as compare channel.

- Generation of a three-phase PWM supported (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- · Dead-time control for each channel to avoid short-circuits in the power stage

- · Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- Hysteresis-like control mode

#### Timer 13 Features:

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period-match and compare-match

- Single-shot mode supported

#### Additional Features:

- Block commutation for Brushless DC-drives implemented

- Position detection via Hall-sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC-drives

- · Output levels can be selected and adapted to the power stage

#### Functional Description

#### 3.20 Power Management System

The TC1115 power management system allows software to configure the various processing units to adjust automatically in order to draw the minimum necessary power for the application.

There are four power management modes:

- Run Mode

- Idle Mode

- Sleep Mode

- Deep Sleep Mode

Table 3-4 describes the features of the power management modes.

#### Table 3-4 Power Management Mode Summary

| Mode       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run        | The system is fully operational. All clocks and peripherals are enabled, as determined by software.                                                                                                                                                                                                                                                                                                                                  |

| Idle       | The CPU clock is disabled, waiting for a condition to return it to run mode.<br>Idle mode can be entered by software when the processor has no active<br>tasks to perform. All peripherals remain powered and clocked. Processor<br>memory is accessible to peripherals. A reset, Watchdog Timer event, a<br>falling edge on the NMI pin, or any enabled interrupt event will return the<br>system to run mode.                      |

| Sleep      | The system clock continues to be distributed only to those peripherals programmed to operate in sleep mode. The other peripheral modules will be shut down by the suspend signal. Interrupts from operating peripherals, the Watchdog Timer, a falling edge on the NMI pin, or a reset event will return the system to run mode. Entering this state requires an orderly shut-down controlled by the Power Management State Machine. |

| Deep Sleep | The system clock is shut off; only an external signal will restart the system. Entering this state requires an orderly shut-down controlled by the Power Management State Machine (PMSM).                                                                                                                                                                                                                                            |

Besides these explicit software-controlled power-saving modes, special attention has been paid in the TC1115 to automatic power-saving in operating units that are currently not required or idle. In this case, they are shut off automatically until their operation is required again.

#### TC1115

#### Advance Information

#### **Functional Description**

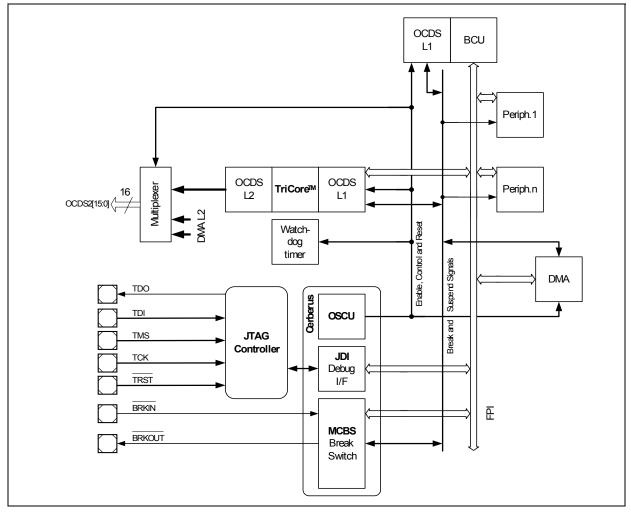

Figure 3-13 OCDS Support Basic Block Diagram

#### **Functional Description**

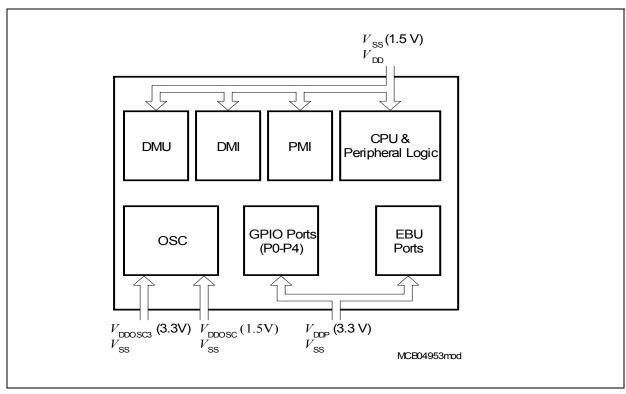

#### 3.23 Power Supply

The TC1115 provides an ingenious power supply concept in order to improve the EMI behavior as well as to minimize the crosstalk within on-chip modules.

**Figure 3-16** shows the TC1115's power supply concept, where certain logic modules are individually supplied with power. This concept improves the EMI behavior by reduction of the noise cross coupling.

Figure 3-16 TC1115 Power Supply Concept

#### **Electrical Parameters**

#### 4 Electrical Parameters

#### 4.1 General Parameters

#### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the TC1115 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for design purposes, they are indicated by the abbreviations in the "Symbol" column:

• cc

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the TC1115 and must be considered for system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the TC1115 is included.

#### **Electrical Parameters**

#### 4.3.2 PLL Parameters

When PLL operation is configured (*PLL\_CLC.LOCK* = 1), the on-chip phase locked loop is enabled and provides the master clock. The PLL multiplies the input frequency by the factor  $\mathbf{F}$  ( $f_{MC} = f_{OSC} \times \mathbf{F}$ ) which results from the input divider, the multiplication factor (N Factor), and the output divider ( $\mathbf{F} = NDIV+1 / (PDIV+1 \times KDIV+1)$ ). The PLL circuit synchronizes the master clock to the input clock. This synchronization is done smoothly, i.e. the master clock frequency does not change abruptly.

Due to this adaptation to the input clock, the frequency of  $f_{\rm MC}$  is constantly adjusted so it is locked to  $f_{\rm OSC}$ . The slight variation causes a jitter of  $f_{\rm MC}$  which also affects the duration of individual TCMs.

The timing listed in the AC Characteristics refers to TCPs. Because  $f_{CPU}$  is derived from  $f_{MC}$ , the timing must be calculated using the minimum TCP possible under the respective circumstances.

The actual minimum value for TCP depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency in order to correspond to the applied input frequency (crystal or oscillator), the relative deviation for periods of more than one TCP is lower than for one single TCP (see formula and Figure 4-2).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baud rates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler (K = KDIV+1) to generate the master clock signal  $f_{MC}$ . Therefore, the number of VCO cycles can be represented as K × N, where N is the number of consecutive  $f_{MC}$  cycles (TCM).

For a period of  $N \times TCM$ , the accumulated PLL jitter is defined by the corresponding deviation  $D_N$ :

$D_N$  [ns] = ±(1.5 + 6.32 ×  $N / f_{MC}$ );  $f_{MC}$  in [MHz], N = number of consecutive TCMs.

So, for a period of 3 TCMs @ 20 MHz and K = 12:  $D_3 = \pm(1.5 + 6.32 \times 3 / 20) = 2.448$  ns.

This formula is applicable for K × N < 95. For longer periods, the K×N=95 value can be used. This steady value can be approximated by: D<sub>Nmax</sub> [ns] = ±(1.5 + 600 / (K ×  $f_{MC})$ ).

#### **Electrical Parameters**

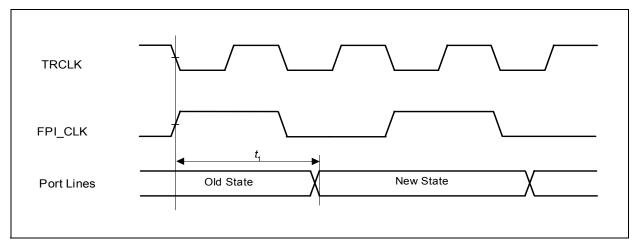

#### 4.3.5 Port Timing

(Operating Conditions apply;  $C_{L}$  = 50 pF)

| Parameter                                                            |                       | nbol | Limits |     | Unit |

|----------------------------------------------------------------------|-----------------------|------|--------|-----|------|

|                                                                      |                       |      | min    | max |      |

| Port data valid from TRCLK <sup>1)</sup> up to 120 MHz <sup>2)</sup> | <i>t</i> <sub>1</sub> | CC   | _      | 13  | ns   |

<sup>1)</sup> Port data is output with respect to the FPI clock. The TRCLK is used as a reference here since the FPI clock is not available as an external pin and TRCLK is same frequency as CPU clock. Port lines maintain their states for at least 2 CPU clocks.

<sup>2)</sup> 120 MHz is verified by design/characterization.

Figure 4-5 Port Timing

#### TC1115

#### **Advance Information**

#### **Electrical Parameters**

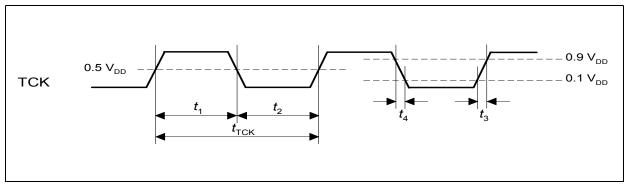

#### 4.3.6 Timing for JTAG Signals

(Operating Conditions apply;  $C_{L}$  = 50 pF)

| Parameter           | Symbol              | Lir | Unit |    |

|---------------------|---------------------|-----|------|----|

|                     |                     | min | max  |    |

| TCK clock period    | t <sub>TCK</sub> SR | 50  | _    | ns |

| TCK high time       | t <sub>1</sub> SR   | 10  | -    | ns |

| TCK low time        | t <sub>2</sub> SR   | 29  | _    | ns |

| TCK clock rise time | t <sub>3</sub> SR   | —   | 0.4  | ns |

| TCK clock fall time | t <sub>4</sub> SR   | _   | 0.4  | ns |

Figure 4-6 TCK Clock Timing

#### **Electrical Parameters**

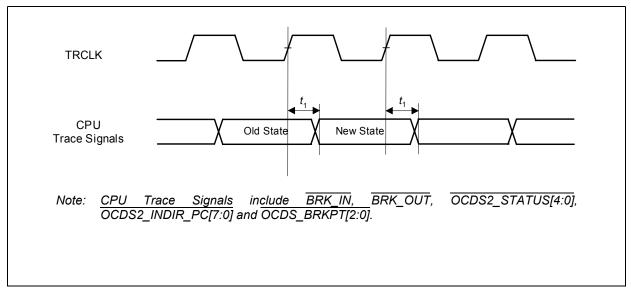

#### 4.3.7 Timing for OCDS Trace and Breakpoint Signals

(Operating Conditions apply;  $C_{L}$ (TRCLK) = 25 pF,  $C_{L}$  = 50 pF)

| Parameter                              |                       | nbol | Lin | Unit |    |

|----------------------------------------|-----------------------|------|-----|------|----|

|                                        |                       |      | min | max  |    |

| BRK_OUT valid from TRCLK 🦨             | <i>t</i> <sub>1</sub> | CC   | _   | 5.2  | ns |

| OCDS2_STATUS[4:0] valid from TRCLK _   | <i>t</i> <sub>1</sub> | CC   | 0   | 5    | ns |

| OCDS2_INDIR_PC[7:0] valid from TRCLK _ | <i>t</i> <sub>1</sub> | CC   | 0   | 5    | ns |

| OCDS2_BRKPT[2:0] valid from TRCLK _    | <i>t</i> <sub>1</sub> | CC   | 0   | 5    | ns |

Figure 4-8 OCDS Trace Signals Timing

#### **Electrical Parameters**

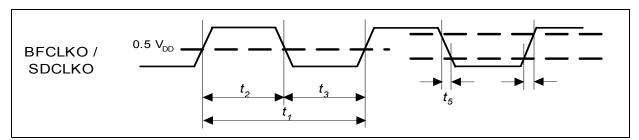

#### Figure 4-9 EBU Clock Output Timing

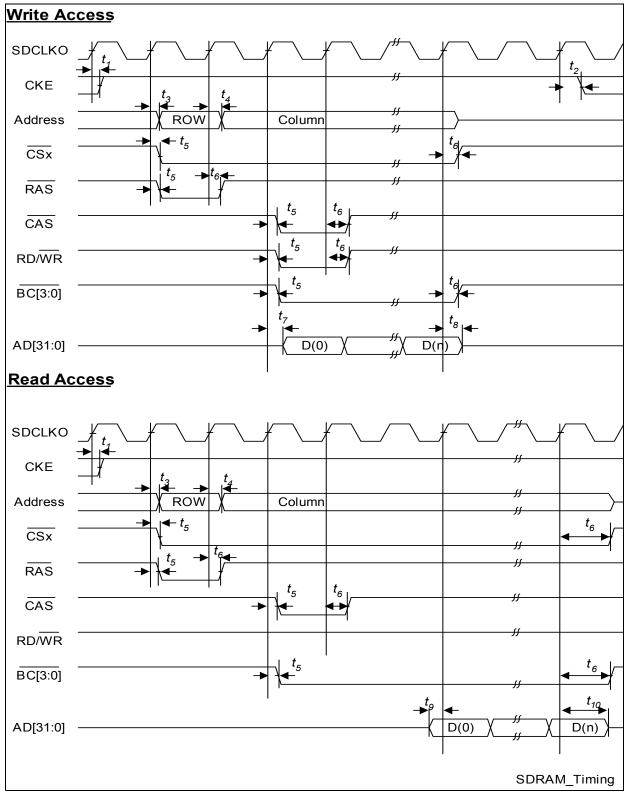

#### 4.3.8.3 Timing for SDRAM Access Signals

(Operating Conditions apply;  $C_{\rm L} = 50 \text{ pF}^{1}$ )

| Parameter                                                     |                        | mbol | Limits <sup>2)</sup> |     | Limits <sup>3)</sup> |     | Unit |

|---------------------------------------------------------------|------------------------|------|----------------------|-----|----------------------|-----|------|

|                                                               |                        |      | min                  | max | min                  | max |      |

| SDCLKO period                                                 | <i>t</i> <sub>1</sub>  | CC   | 10                   | -   | 8.3                  | -   | ns   |

| CKE output valid time from SDCLKO 🦨                           | <i>t</i> <sub>1</sub>  | CC   | -                    | 8.0 | -                    | 6.8 | ns   |

| CKE output hold time from SDCLKO 🦨                            | <i>t</i> <sub>2</sub>  | CC   | 0                    | _   | 0.8                  | -   | ns   |

| Address output valid time from SDCLKO 🖌                       | t <sub>3</sub>         | CC   | _                    | 8.0 | _                    | 6.8 | ns   |

| Address output hold time from SDCLKO 🦵                        | <i>t</i> <sub>4</sub>  | CC   | 1.0                  | -   | 0.8                  | _   | ns   |

| CSx, RAS, CAS, RD/WR, BC(3:0) output valid time from SDCLKO _ | <i>t</i> <sub>5</sub>  | CC   | _                    | 8.0 | -                    | 6.8 | ns   |

| CSx, RAS, CAS, RD/WR, BC(3:0) output hold time from SDCLKO _  | t <sub>6</sub>         | CC   | 1.0                  | _   | 0.8                  | _   | ns   |

| AD(31:0) output valid time from SDCLKO _                      | <i>t</i> <sub>7</sub>  | CC   | _                    | 8.0 | _                    | 6.8 | ns   |

| AD(31:0) output hold time from SDCLKO _                       | <i>t</i> 8             | CC   | 1.0                  | _   | 0.8                  | _   | ns   |

| AD(31:0) input setup time to SDCLKO _                         | t <sub>9</sub>         | SR   | 4.0                  | _   | 2.9                  | _   | ns   |

| AD(31:0) input hold time from SDCLKO _                        | <i>t</i> <sub>10</sub> | SR   | 3.0                  | -   | 3.0                  | -   | ns   |

1) If application conditions other than 50 pf capacitive load are used, then the proper correlation factor should be used for your specific application condition. For design team, the load should be set according to the system requirement.

2) The parameters are applicable for PC100 SDRAM access and the maximum SDCLKO is up to 100 MHz.

3) The parameters are applicable for PC133 SDRAM access and the maximum SDCLKO is up to 120 MHz.

#### **Electrical Parameters**

Figure 4-10 SDRAM Access Timing

#### Package Outline

TC1115

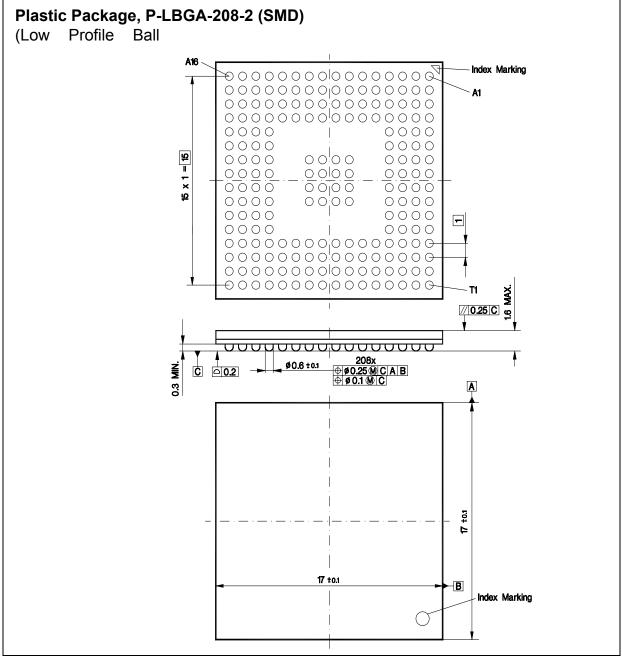

### 5 Package Outline

Figure 5-1 P-LBGA-208-2 Package

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

SMD = Surface Mounted Device

Dimensions in mm