Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm306-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.6 CPU Control Registers

## REGISTER 3-1: SR: CPU STATUS REGISTER

| REGISTE            | R 3-1: SR: C                                            | PU STATUS                            | REGISTER          |                        |                   |                   |                |

|--------------------|---------------------------------------------------------|--------------------------------------|-------------------|------------------------|-------------------|-------------------|----------------|

| R/W-0              | ) R/W-0                                                 | R/W-0                                | R/W-0             | R/C-0                  | R/C-0             | R-0               | R/W-0          |

| OA                 | OB                                                      | SA <sup>(3)</sup>                    | SB <sup>(3)</sup> | OAB                    | SAB               | DA                | DC             |

| bit 15             |                                                         |                                      |                   |                        |                   |                   | bit 8          |

| R/W-0              | <sup>2)</sup> R/W-0 <sup>(2)</sup>                      | R/W-0 <sup>(2)</sup>                 | R-0               | R/W-0                  | R/W-0             | R/W-0             | R/W-0          |

| IPL2 <sup>(1</sup> | ) IPL1 <sup>(1)</sup>                                   | IPL0 <sup>(1)</sup>                  | RA                | N                      | OV                | Z                 | С              |

| bit 7              |                                                         |                                      |                   |                        |                   |                   | bit 0          |

| Legend:            |                                                         | C = Clearable                        | e bit             |                        |                   |                   |                |

| R = Read           | able bit                                                | W = Writable                         | bit               | U = Unimple            | mented bit, read  | 1 as '0'          |                |

| -n = Value         | at POR                                                  | '1' = Bit is set                     |                   | '0' = Bit is cle       | eared             | x = Bit is unkr   | nown           |

|                    |                                                         |                                      |                   |                        |                   |                   |                |

| bit 15             | OA: Accumu                                              | lator A Overflov                     | v Status bit      |                        |                   |                   |                |

|                    | 1 = Accumula                                            | ator A has over                      | flowed            |                        |                   |                   |                |

|                    | 0 = Accumula                                            | ator A has not o                     | overflowed        |                        |                   |                   |                |

| bit 14             | OB: Accumu                                              | lator B Overflov                     | v Status bit      |                        |                   |                   |                |

|                    |                                                         | ator B has over                      |                   |                        |                   |                   |                |

|                    |                                                         | ator B has not o                     |                   | (2)                    |                   |                   |                |

| bit 13             |                                                         | lator A Saturati                     | -                 |                        |                   |                   |                |

|                    |                                                         | ator A is satura<br>ator A is not sa |                   | en saturated at        | some time         |                   |                |

| bit 12             | SB: Accumul                                             | lator B Saturati                     | on 'Sticky' Sta   | tus bit <sup>(3)</sup> |                   |                   |                |

|                    |                                                         | ator B is satura<br>ator B is not sa |                   | en saturated at        | some time         |                   |                |

| bit 11             | OAB: OA II O                                            | OB Combined A                        | ccumulator O      | verflow Status         | bit               |                   |                |

|                    | 1 = Accumula                                            | ator A or B has                      | overflowed        |                        |                   |                   |                |

| hit 10             |                                                         |                                      |                   |                        |                   |                   |                |

| bit 10             |                                                         | B Combined A                         |                   | •                      | ed at some time   | <b>`</b>          |                |

|                    | - ////                                                  | A OF B IS SA                         |                   |                        |                   | 5                 |                |

| bit 9              | DA: DO Loop                                             | Active bit                           |                   |                        |                   |                   |                |

|                    | 1 = DO <b>loop i</b>                                    | n progress<br>not in progress        |                   |                        |                   |                   |                |

| bit 8              | •                                                       | U Half Carry/B                       | orrow hit         |                        |                   |                   |                |

| bit o              |                                                         | -                                    |                   | for byte-sized         | data) or 8th low- | order bit (for wo | ord-sized data |

|                    | •                                                       | sult occurred                        |                   |                        | ,                 |                   |                |

|                    |                                                         | -out from the 4<br>the result occur  |                   | oit (for byte-siz      | ed data) or 8th   | low-order bit (1  | for word-sized |

| Note 1:            | The IPL<2:0> bits<br>Level. The value in<br>IPL<3> = 1. |                                      |                   |                        |                   |                   |                |

| 2:                 | The IPL<2:0> Stat                                       | tus bits are read                    | d-only when th    | ne NSTDIS bit          | (INTCON1<15>      | •) = 1.           |                |

| 3.                 | A data write to the                                     |                                      | -                 |                        | -                 |                   | nd SB or by    |

**3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

### TABLE 4-45: DMA CONTROLLER REGISTER MAP

| IADLE 4- | 4J.   |        |        |             |        |        |            | -     |              |                                                                 |         |         |         | -       |         | -       |         |               |

|----------|-------|--------|--------|-------------|--------|--------|------------|-------|--------------|-----------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------------|

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13      | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8        | Bit 7                                                           | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| DMA0CON  | 0B00  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | —          | _     | —            | —                                                               | _       | AMODE1  | AMODE0  | —       | —       | MODE1   | MODE0   | 0000          |

| DMA0REQ  | 0B02  | FORCE  | _      | _           | _      | _      | _          | _     | _            | IRQSEL7                                                         | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA0STAL | 0B04  |        |        |             |        |        |            |       | STA<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA0STAH | 0B06  |        | _      | _           | _      | _      | STA<23:16> |       |              |                                                                 |         |         |         | 0000    |         |         |         |               |

| DMA0STBL | 0B08  |        |        |             |        |        |            |       | STB<1        | STB<15:0>                                                       |         |         |         |         |         |         | 0000    |               |

| DMA0STBH | 0B0A  | —      | —      | _           | _      | —      | —          | —     | — STB<23:16> |                                                                 |         |         |         |         |         | 0000    |         |               |

| DMA0PAD  | 0B0C  |        |        |             |        |        |            |       | PAD<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA0CNT  | 0B0E  |        | _      |             |        |        |            |       |              | CNT<1                                                           | 3:0>    |         |         |         |         |         |         | 0000          |

| DMA1CON  | 0B10  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | _          | _     | _            | AMODE1 AMODE0 - MODE1 MOI                                       |         |         |         |         |         | MODE0   | 0000    |               |

| DMA1REQ  | 0B12  | FORCE  | _      | _           |        | _      | _          | _     | _            | IRQSEL7                                                         | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 00FF          |

| DMA1STAL | 0B14  |        |        |             |        |        |            |       | STA<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA1STAH | 0B16  | Ι      | _      | _           | _      | —      | —          | —     | _            |                                                                 |         |         | STA<2   | 3:16>   |         |         |         | 0000          |

| DMA1STBL | 0B18  |        |        |             |        |        |            |       | STB<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA1STBH | 0B1A  |        | _      | _           | _      | _      | _          | _     | _            |                                                                 |         |         | STB<2   | 3:16>   |         |         |         | 0000          |

| DMA1PAD  | 0B1C  |        |        |             |        |        |            |       | PAD<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA1CNT  | 0B1E  | _      | _      |             |        |        |            |       |              | CNT<1                                                           | 3:0>    |         |         |         |         |         |         | 0000          |

| DMA2CON  | 0B20  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | _          | _     | _            | AMODE1 AMODE0 - MODE1 MODE                                      |         |         |         |         | MODE0   | 0000    |         |               |

| DMA2REQ  | 0B22  | FORCE  | _      | _           | _      | _      | _          | —     | _            | - IRQSEL7 IRQSEL6 IRQSEL5 IRQSEL4 IRQSEL3 IRQSEL2 IRQSEL1 IRQSE |         |         |         |         | IRQSEL0 | 00FF    |         |               |

| DMA2STAL | 0B24  |        |        |             |        |        |            |       | STA<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA2STAH | 0B26  |        | _      | _           | _      | _      | _          | _     | _            |                                                                 |         |         | STA<2   | 3:16>   |         |         |         | 0000          |

| DMA2STBL | 0B28  |        |        |             |        |        |            |       | STB<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA2STBH | 0B2A  | _      | _      | _           | _      | _      | _          | _     | _            |                                                                 |         |         | STB<2   | 3:16>   |         |         |         | 0000          |

| DMA2PAD  | 0B2C  |        |        |             |        |        |            |       | PAD<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA2CNT  | 0B2E  | —      | —      |             |        |        |            |       |              | CNT<1                                                           | 3:0>    |         |         |         |         |         |         | 0000          |

| DMA3CON  | 0B30  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | _          | _     | _            | _                                                               | _       | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA3REQ  | 0B32  | FORCE  | _      | -           | _      | -      | _          | -     | _            | IRQSEL7                                                         | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA3STAL | 0B34  |        |        |             |        |        |            |       | STA<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA3STAH | 0B36  |        | _      | _           | _      | _      | _          | _     | _            |                                                                 |         |         | STA<2   | 3:16>   |         |         |         | 0000          |

| DMA3STBL | 0B38  |        |        |             |        |        |            |       | STB<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA3STBH | 0B3A  | _      | _      | _           |        | _      | _          | _     | _            |                                                                 |         |         | STB<2   | 3:16>   |         |         |         | 0000          |

| DMA3PAD  | 0B3C  |        |        |             |        |        |            |       | PAD<1        | 5:0>                                                            |         |         |         |         |         |         |         | 0000          |

| DMA3CNT  | 0B3E  | _      | _      |             |        |        |            |       |              | CNT<1                                                           | 3:0>    |         |         |         |         |         |         | 0000          |

| DMAPWC   | 0BF0  | _      | _      | —           | —      | _      | —          | —     | —            | —                                                               | —       | —       | —       | PWCOL3  | PWCOL2  | PWCOL1  | PWCOL0  | 0000          |

| DMARQC   | 0BF2  | _      | _      | _           |        | _      | —          | _     | _            | —                                                               |         | _       | _       | RQCOL3  | RQCOL2  | RQCOL1  | RQCOL0  | 0000          |

| DMAPPS   | 0BF4  | _      | _      | _           | _      | _      | —          | _     | —            | —                                                               | _       | —       | _       | PPST3   | PPST2   | PPST1   | PPST0   | 0000          |

| DMALCA   | 0BF6  | _      | _      | —           | _      | _      | -          | _     | —            | —                                                               | —       | —       | _       |         | LSTCH   | 1<3:0>  |         | 000F          |

| DSADRL   | 0BF8  |        |        |             |        |        |            |       | DSADR<15:0>  |                                                                 |         |         |         | 0000    |         |         |         |               |

| DSADRH   | 0BFA  | _      | _      | —           |        | —      | —          | _     |              |                                                                 |         |         |         | 0000    |         |         |         |               |

| Logond   |       |        |        | Posot valuo |        |        |            |       |              |                                                                 |         |         |         |         |         |         |         | <u>.</u>      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-55: PORTD REGISTER MAP FOR dsPIC33EPXXXGM310/710 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|--------|-------|--------|-------|------------|-------|-------|--------|-------|-------|-------|---------------|

| TRISD       | 0E30  |        | TRISD< | <15:12> |        | _      |        |       | TRISD8 |       | TRISD<6:1> |       |       |        |       | —     | 0160  |               |

| PORTD       | 0E32  |        | RD<1   | 5:12>   |        |        | _      | —     | RD8    | —     | RD<6:1>    |       |       |        |       | _     | xxxx  |               |

| LATD        | 0E34  |        | LATD<  | 15:12>  |        | _      | _      | _     | LATD8  | _     | LATD<6:1>  |       |       |        | _     | xxxx  |       |               |

| ODCD        | 0E36  |        | ODCD<  | <15:12> |        | _      | _      | _     | ODCD8  | _     |            |       | ODCE  | )<6:1> |       |       | _     | 0000          |

| CNEND       | 0E38  |        | CNIED. | <15:12> |        |        | _      | —     | CNIED8 | —     |            |       | CNIE  | 0<6:1> |       |       |       | 0000          |

| CNPUD       | 0E3A  |        | CNPUD  | <15:12> |        |        | _      | —     | CNPUD8 | —     |            |       | CNPU  | D<6:1> |       |       |       | 0000          |

| CNPDD       | 0E3C  |        | CNPDD  | <15:12> |        |        | _      | —     | CNPDD8 | —     | CNPDD<6:1> |       |       |        |       | 0000  |       |               |

| ANSELD      | 0E3E  | ANSD<  | 15:14> | -       | _      |        | _      | _     | _      | —     | _          | _     | —     | —      | _     |       | —     | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-56: PORTD REGISTER MAP FOR dsPIC33EPXXXGM306/706DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD       | 0E30  | _      | _      | _      |        | —      |        |       | TRISD8 | _     | TRISD | <6:5>  | —     | _     | _     | _     |       | 0160          |

| PORTD       | 0E32  |        | _      | _      | _      | _      | _      | _     | RD8    | Ι     | RD<   | 6:5>   | _     | _     | _     | _     | _     | xxxx          |

| LATD        | 0E34  | _      | _      | _      |        | —      |        |       | LATD8  | _     | LATD  | <6:5>  | —     | _     | _     | _     |       | xxxx          |

| ODCD        | 0E36  | _      | _      | -      |        | —      |        |       | ODCD8  | _     | ODCD  | <6:5>  | —     | _     | _     | _     |       | 0000          |

| CNEND       | 0E38  |        | _      | _      | _      | _      | _      | _     | CNIED8 | Ι     | CNIED | )<6:5> | _     | _     | _     | _     | _     | 0000          |

| CNPUD       | 0E3A  | _      | _      | _      |        | —      | _      |       | CNPUD8 | _     | CNPU  | D<6:5> | —     | _     | _     | _     |       | 0000          |

| CNPDD       | 0E3C  | _      | _      | —      | -      | —      | _      | _     | —      | _     | —     | _      | —     | _     | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-57: PORTE REGISTER MAP FOR dsPIC33EPXXXGM310/710 DEVICES

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11         | Bit 10 | Bit 9     | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|----------|-------|--------|--------|------------|--------|----------------|--------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|--------|---------------|

| TRISE    | 0E40  |        | TRISE  | ISE<15:12> |        | — — TRISE<9:8> |        |           |        | _     | TRISE | <1:0> | F303  |       |       |       |        |               |

| PORTE    | 0E42  |        | RE<1   | 5:12>      |        | _              | _      | RE<9:8>   |        |       |       | —     | _     |       | _     | RE<   | 1:0>   | xxxx          |

| LATE     | 0E44  |        | LATE<  | :15:12>    |        | _              | _      | LATE      | <9:8>  |       |       | —     | _     |       | _     | LATE  | <1:0>  | xxxx          |

| ODCE     | 0E46  |        | ODCE.  | <15:12>    |        | _              | _      | ODCE<9:8> |        |       |       | —     | _     |       | _     | ODCE  | <1:0>  | 0000          |

| CNENE    | 0E48  |        | CNIEE  | <15:12>    |        | _              | _      | CNIE      | =<9:8> |       |       | —     | _     |       | _     | CNIE  | <1:0>  | 0000          |

| CNPUE    | 0E4A  |        | CNPUE  | <15:12>    |        | _              | _      | CNPU      | E<9:8> |       |       | —     | _     |       | _     | CNPU  | E<1:0> | 0000          |

| CNPDE    | 0E4C  |        | CNPDE  | <15:12>    |        | _              | _      | CNPD      | E<9:8> |       |       | —     | _     |       | _     | CNPD  | E<1:0> | 0000          |

| ANSELE   | 0E4E  |        | ANSE<  | <15:12>    |        | —              | _      | ANSE      | <9:8>  |       | _     |       |       | _     | _     | ANSE  | <1:0>  | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0           | R/W-0        | R/W-0                               | R/W-0    | R/W-0             | R/W-0                        | R/W-0               | R/W-0        |

|-----------------|--------------|-------------------------------------|----------|-------------------|------------------------------|---------------------|--------------|

| T5MD            | T4MD         | T3MD                                | T2MD     | T1MD              | QEI1MD                       | PWMMD               | DCIMD        |

| bit 15          |              |                                     |          |                   |                              |                     | bit          |

| R/W-0           | R/W-0        |                                     | R/W-0    | R/W-0             |                              | R/W-0               | R/W-0        |

|                 | -            | R/W-0                               | -        | -                 | R/W-0<br>C2MD <sup>(1)</sup> | C1MD <sup>(1)</sup> | -            |

| l2C1MD<br>bit 7 | U2MD         | U1MD                                | SPI2MD   | SPI1MD            | CZIVID                       | CIMDO               | AD1MD<br>bit |

|                 |              |                                     |          |                   |                              |                     |              |

| Legend:         |              |                                     |          |                   |                              |                     |              |

| R = Readabl     | e bit        | W = Writable                        | bit      | U = Unimplen      | nented bit, rea              | d as '0'            |              |

| -n = Value at   | POR          | '1' = Bit is set                    |          | '0' = Bit is clea | ared                         | x = Bit is unkn     | own          |

| bit 15          | TEMD. Timor  | 5 Module Disal                      | alo hit  |                   |                              |                     |              |

| DIC 15          |              | odule is disable                    |          |                   |                              |                     |              |

|                 |              | odule is enable                     |          |                   |                              |                     |              |

| bit 14          | T4MD: Timer  | 4 Module Disal                      | ole bit  |                   |                              |                     |              |

|                 | 1 = Timer4 m | odule is disable                    | ed       |                   |                              |                     |              |

|                 | 0 = Timer4 m | odule is enable                     | ed       |                   |                              |                     |              |

| bit 13          | T3MD: Timer  | 3 Module Disal                      | ole bit  |                   |                              |                     |              |

|                 |              | odule is disabl                     |          |                   |                              |                     |              |

|                 |              | odule is enable                     |          |                   |                              |                     |              |

| bit 12          | -            | 2 Module Disal                      |          |                   |                              |                     |              |

|                 | -            | odule is disable                    |          |                   |                              |                     |              |

| L:1 44          |              | odule is enable                     |          |                   |                              |                     |              |

| bit 11          | -            | 1 Module Disal                      |          |                   |                              |                     |              |

|                 | -            | odule is disable<br>odule is enable |          |                   |                              |                     |              |

| bit 10          |              | 11 Module Disa                      |          |                   |                              |                     |              |

| Sit 10          |              | dule is disabled                    |          |                   |                              |                     |              |

|                 |              | dule is enabled                     |          |                   |                              |                     |              |

| bit 9           | PWMMD: PW    | /M Module Dis                       | able bit |                   |                              |                     |              |

|                 | 1 = PWM mo   | dule is disable                     | t        |                   |                              |                     |              |

|                 | 0 = PWM mo   | dule is enabled                     | l        |                   |                              |                     |              |

| bit 8           | DCIMD: DCI   | Module Disable                      | e bit    |                   |                              |                     |              |

|                 |              | ule is disabled                     |          |                   |                              |                     |              |

| bit 7           |              | 1 Module Disal                      | ale hit  |                   |                              |                     |              |

|                 |              | lule is disabled                    |          |                   |                              |                     |              |

|                 |              | lule is enabled                     |          |                   |                              |                     |              |

| bit 6           | U2MD: UART   | 2 Module Disa                       | ble bit  |                   |                              |                     |              |

|                 |              | nodule is disabl                    |          |                   |                              |                     |              |

|                 | -            | nodule is enable                    |          |                   |                              |                     |              |

| bit 5           | U1MD: UART   | 1 Module Disa                       | ble bit  |                   |                              |                     |              |

|                 | 1 = UART1 m  | nodule is disabl                    | ed       |                   |                              |                     |              |

|                 | 0 = UART1 m  | odule is enabl                      | ed       |                   |                              |                     |              |

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: These bits are available on dsPIC33EPXXXGM6XX/7XX devices only.

## 11.7 Peripheral Pin Select Registers

### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0                                | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |  |

|------------------------------------|-------|--------------|-------|-----------------------------------------|------------------|----------|-------|--|--|

| —                                  |       |              |       | INT1R<6:0>                              |                  |          |       |  |  |

| bit 15                             |       |              |       |                                         |                  |          | bit 8 |  |  |

|                                    |       |              |       |                                         |                  |          |       |  |  |

| U-0                                | U-0   | U-0          | U-0   | U-0                                     | U-0              | U-0      | U-0   |  |  |

| —                                  | —     | —            | _     | —                                       | —                | —        | —     |  |  |

| bit 7                              |       |              |       |                                         |                  |          | bit 0 |  |  |

|                                    |       |              |       |                                         |                  |          |       |  |  |

| Legend:                            |       |              |       |                                         |                  |          |       |  |  |

| R = Readable                       | bit   | W = Writable | bit   | U = Unimpler                            | mented bit, read | d as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |

| bit 15   | Unimplemented: Read as '0'                                                                                                        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111100 = Input tied to RPI124                                                                                                    |

|          | •                                                                                                                                 |

|          | •                                                                                                                                 |

|          | •                                                                                                                                 |

|          | 000001 = Input tied to CMP1                                                                                                       |

|          | 000000 = Input tied to Vss                                                                                                        |

| bit 7-0  | Unimplemented: Read as '0'                                                                                                        |

### REGISTER 16-12: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PDC   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PDC   | x<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **PDCx<15:0>:** PWMx Generator # Duty Cycle Value bits

## REGISTER 16-13: SDCx: PWMx SECONDARY DUTY CYCLE REGISTER<sup>(1)</sup>

| R/W-0 | R/W-0            | R/W-0                             | R/W-0                                                    | R/W-0                                                                                                                                                    | R/W-0                                                                                        | R/W-0                                                                                                      |

|-------|------------------|-----------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|       |                  | SDC                               | x<15:8>                                                  |                                                                                                                                                          |                                                                                              |                                                                                                            |

|       |                  |                                   |                                                          |                                                                                                                                                          |                                                                                              | bit 8                                                                                                      |

|       |                  |                                   |                                                          |                                                                                                                                                          |                                                                                              |                                                                                                            |

| R/W-0 | R/W-0            | R/W-0                             | R/W-0                                                    | R/W-0                                                                                                                                                    | R/W-0                                                                                        | R/W-0                                                                                                      |

|       |                  | SDC                               | x<7:0>                                                   |                                                                                                                                                          |                                                                                              |                                                                                                            |

|       |                  |                                   |                                                          |                                                                                                                                                          |                                                                                              | bit 0                                                                                                      |

|       |                  |                                   |                                                          |                                                                                                                                                          |                                                                                              |                                                                                                            |

|       |                  |                                   |                                                          |                                                                                                                                                          |                                                                                              |                                                                                                            |

| bit   | W = Writable I   | bit                               | U = Unimplen                                             | nented bit, rea                                                                                                                                          | d as '0'                                                                                     |                                                                                                            |

| OR    | '1' = Bit is set |                                   | '0' = Bit is cle                                         | ared                                                                                                                                                     | x = Bit is unkr                                                                              | nown                                                                                                       |

|       | R/W-0            | R/W-0 R/W-0<br>bit W = Writable I | SDC:<br>R/W-0 R/W-0 R/W-0<br>SDC<br>bit W = Writable bit | SDCx<15:8>           R/W-0         R/W-0         R/W-0           SDCx<7:0>         SDCx<7:0>           bit         W = Writable bit         U = Unimpler | SDCx<15:8>           R/W-0         R/W-0         R/W-0           SDCx<7:0>         SDCx<7:0> | SDCx<15:8>           R/W-0         R/W-0         R/W-0         R/W-0           SDCx<7:0>         SDCx<7:0> |

bit 15-0 SDCx<15:0>: Secondary Duty Cycle bits for PWMxL Output Pin bits

**Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle.

NOTES:

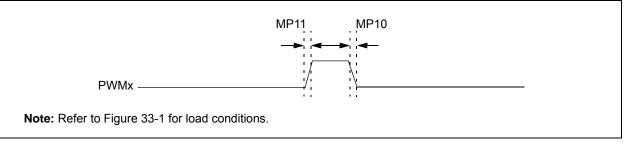

### 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

**Note:** This insures that the first frame transmission after initialization is not shifted or corrupted.

- 2. In Non-Framed 3-Wire mode (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on  $\overline{SSx}$ .

- **Note:** This will insure that during power-up and initialization, the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors, for both transmit and receive, appearing as corrupted data.

- 3. FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPIx specifications in Section 33.0 "Electrical Characteristics" for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                              |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                       |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                      |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                  |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>                                                   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                 |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                   |

|       | 0 = Framing error has not been detected                                                                                                                                                                                    |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets<br/>the receive buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                 |

|       | <ul><li>1 = Receive buffer has data, at least one more character can be read</li><li>0 = Receive buffer is empty</li></ul>                                                                                                 |

|       |                                                                                                                                                                                                                            |

Note 1: Refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) for information on enabling the UART module for transmit operation.

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                          | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0    |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|-------------------|------------------|-----------------|----------|--|--|--|--|

| EDG1MOD       | EDG1POL                                                                                                                                  | EDG1SEL3                       | EDG1SEL2       | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                                                                                                                          |                                |                |                   | •                |                 | bit 8    |  |  |  |  |

|               |                                                                                                                                          |                                |                |                   |                  |                 |          |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                          | R/W-0          | R/W-0             | R/W-0            | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                                                  | EDG2SEL3                       | EDG2SEL2       | EDG2SEL1          | EDG2SEL0         | —               | —        |  |  |  |  |

| bit 7         |                                                                                                                                          |                                |                |                   |                  | •               | bit 0    |  |  |  |  |

|               |                                                                                                                                          |                                |                |                   |                  |                 |          |  |  |  |  |

| Legend:       |                                                                                                                                          |                                |                |                   |                  |                 |          |  |  |  |  |

| R = Readable  | e bit                                                                                                                                    | W = Writable                   | bit            | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is set               |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |  |

|               |                                                                                                                                          |                                |                |                   |                  |                 |          |  |  |  |  |

| bit 15        | EDG1MOD: E                                                                                                                               | Edge 1 Edge Sa                 | ampling Mode   | Selection bit     |                  |                 |          |  |  |  |  |

|               | 0                                                                                                                                        | edge-sensitive                 |                |                   |                  |                 |          |  |  |  |  |

|               | 0 = Edge 1 is level-sensitive                                                                                                            |                                |                |                   |                  |                 |          |  |  |  |  |

| bit 14        | <b>EDG1POL:</b> Edge 1 Polarity Select bit<br>1 = Edge 1 is programmed for a positive edge response                                      |                                |                |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                                                          |                                |                |                   |                  |                 |          |  |  |  |  |

| bit 13-10     | <ul> <li>0 = Edge 1 is programmed for a negative edge response</li> <li>13-10 EDG1SEL&lt;3:0&gt;: Edge 1 Source Select bits</li> </ul>   |                                |                |                   |                  |                 |          |  |  |  |  |

|               | 1111 = Fosc                                                                                                                              |                                |                |                   |                  |                 |          |  |  |  |  |

|               | 1111 = POSC<br>1110 = OSCI pin                                                                                                           |                                |                |                   |                  |                 |          |  |  |  |  |

|               | 1101 <b>= FRC</b> o                                                                                                                      |                                |                |                   |                  |                 |          |  |  |  |  |

|               | 1100 = Reser                                                                                                                             | rved<br>al LPRC oscilla        | tor            |                   |                  |                 |          |  |  |  |  |

|               | 1011 = Intern<br>1010 = Reser                                                                                                            |                                |                |                   |                  |                 |          |  |  |  |  |

|               | 100x = Reser                                                                                                                             | rved                           |                |                   |                  |                 |          |  |  |  |  |

|               | 01xx = Reser                                                                                                                             |                                |                |                   |                  |                 |          |  |  |  |  |

|               | 0011 = CTED<br>0010 = CTED                                                                                                               |                                |                |                   |                  |                 |          |  |  |  |  |

|               | 0001 = OC1 r                                                                                                                             | •                              |                |                   |                  |                 |          |  |  |  |  |

|               | 0000 <b>= Time</b> r                                                                                                                     | 1 module                       |                |                   |                  |                 |          |  |  |  |  |

| bit 9         | EDG2STAT: E                                                                                                                              | Edge 2 Status b                | bit            |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                                                          |                                | 2 and can be v | vritten to contro | ol the edge sou  | rce.            |          |  |  |  |  |

|               | 1 = Edge 2 has<br>0 = Edge 2 has                                                                                                         | as occurred<br>as not occurred | 4              |                   |                  |                 |          |  |  |  |  |

| bit 8         | -                                                                                                                                        | Edge 1 Status b                |                |                   |                  |                 |          |  |  |  |  |

| bit 0         |                                                                                                                                          | -                              |                | vritten to contro | ol the edge sou  | rce             |          |  |  |  |  |

|               | 1 = Edge 1 ha                                                                                                                            |                                |                |                   | i lie euge eeu   |                 |          |  |  |  |  |

|               | 0 = Edge 1 h                                                                                                                             | as not occurred                | t              |                   |                  |                 |          |  |  |  |  |

| bit 7         | EDG2MOD: E                                                                                                                               | Edge 2 Edge Sa                 | ampling Mode   | Selection bit     |                  |                 |          |  |  |  |  |

|               | -                                                                                                                                        | edge-sensitive                 |                |                   |                  |                 |          |  |  |  |  |

| h:+ C         | •                                                                                                                                        | level-sensitive                |                |                   |                  |                 |          |  |  |  |  |

| bit 6         |                                                                                                                                          | dge 2 Polarity                 |                | dao roonana       |                  |                 |          |  |  |  |  |

|               | <ul> <li>1 = Edge 2 is programmed for a positive edge response</li> <li>0 = Edge 2 is programmed for a negative edge response</li> </ul> |                                |                |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                                                          |                                |                |                   |                  |                 |          |  |  |  |  |

|               | he TGEN bit is                                                                                                                           |                                |                |                   | selected as the  | e Edge 2 sourc  | e in the |  |  |  |  |

| EL            | G2SELx bits fi                                                                                                                           | eiu, otnerwise,                | the module WI  | i not function.   |                  |                 |          |  |  |  |  |

### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

| R/W-0                 | R/W-0                                                       | R/W-0                                                                   | U-0                 | U-0              | U-0             | R/W-0               | R/W-0               |

|-----------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|------------------|-----------------|---------------------|---------------------|

| CON                   | COE                                                         | CPOL                                                                    |                     |                  |                 | CEVT <sup>(2)</sup> | COUT                |

| bit 15                |                                                             |                                                                         |                     |                  |                 |                     | bit                 |

|                       |                                                             |                                                                         |                     |                  |                 |                     |                     |

| R/W-0                 | R/W-0                                                       | U-0                                                                     | R/W-0               | U-0              | U-0             | R/W-0               | R/W-0               |

| EVPOL1 <sup>(2)</sup> | EVPOL0 <sup>(2)</sup>                                       | —                                                                       | CREF <sup>(1)</sup> | —                | —               | CCH1 <sup>(1)</sup> | ССН0 <sup>(1)</sup> |

| bit 7                 |                                                             |                                                                         |                     |                  |                 |                     | bit                 |

| Legend:               |                                                             |                                                                         |                     |                  |                 |                     |                     |

| R = Readable          | bit                                                         | W = Writable                                                            | bit                 | U = Unimpler     | nented bit, rea | ıd as '0'           |                     |

| -n = Value at F       | POR                                                         | '1' = Bit is set                                                        | t                   | '0' = Bit is cle | ared            | x = Bit is unkn     | iown                |

| bit 14<br>bit 13      | 0 = Comparat                                                | or is disabled<br>rator Output E<br>or output is pr<br>or output is int | esent on the C      | ·                |                 |                     |                     |

| DIL 13                | 1 = Comparat<br>0 = Comparat                                | or output is in                                                         | verted              | Dit              |                 |                     |                     |

| bit 12-10             | Unimplement                                                 | ted: Read as '                                                          | 0'                  |                  |                 |                     |                     |

| bit 9                 | CEVT: Compa                                                 | arator Event bi                                                         | t <sup>(2)</sup>    |                  |                 |                     |                     |

|                       |                                                             | until the bit is                                                        | cleared             | VPOL<1:0> se     | ttings, occurre | ed; disables futur  | e triggers an       |

| bit 8                 | COUT: Compa                                                 | arator Output                                                           | bit                 |                  |                 |                     |                     |

|                       | When CPOL           1 = VIN+ > VIN           0 = VIN+ < VIN | 1-                                                                      | ed polarity):       |                  |                 |                     |                     |

|                       | When CPOL =                                                 | = 1 (inverted p                                                         | olarity):           |                  |                 |                     |                     |

2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), **must be cleared** before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

## dsPIC33EPXXXGM3XX/6XX/7XX

| U-0          | U-0                                                                      | U-0              | U-0           | U-0              | R/W-x            | R/W-x              | R/W-x  |  |  |  |

|--------------|--------------------------------------------------------------------------|------------------|---------------|------------------|------------------|--------------------|--------|--|--|--|

| —            | —                                                                        | —                | —             | —                | WDAY2            | WDAY1              | WDAY0  |  |  |  |

| bit 15       |                                                                          |                  |               |                  |                  |                    | bit 8  |  |  |  |

|              |                                                                          |                  |               |                  |                  |                    |        |  |  |  |

| U-0          | U-0                                                                      | R/W-x            | R/W-x         | R/W-x            | R/W-x            | R/W-x              | R/W-x  |  |  |  |

| —            |                                                                          | HRTEN1           | HRTEN0        | HRONE3           | HRONE2           | HRONE1             | HRONE0 |  |  |  |

| bit 7        |                                                                          |                  |               |                  |                  |                    | bit 0  |  |  |  |

|              |                                                                          |                  |               |                  |                  |                    |        |  |  |  |

| Legend:      |                                                                          |                  |               |                  |                  |                    |        |  |  |  |

| R = Readab   | le bit                                                                   | W = Writable     | bit           | U = Unimpler     | mented bit, read | l as '0'           |        |  |  |  |

| -n = Value a | t POR                                                                    | '1' = Bit is set |               | '0' = Bit is cle | ared             | x = Bit is unknown |        |  |  |  |

|              |                                                                          |                  |               |                  |                  |                    |        |  |  |  |

| bit 15-11    | Unimplemen                                                               | ted: Read as '   | 0'            |                  |                  |                    |        |  |  |  |

| bit 10-8     | WDAY<2:0>:                                                               | Binary Coded     | Decimal Value | e of Weekday I   | Digit bits       |                    |        |  |  |  |

|              | Contains a value from 0 to 6.                                            |                  |               |                  |                  |                    |        |  |  |  |

| bit 7-6      | bit 7-6 Unimplemented: Read as '0'                                       |                  |               |                  |                  |                    |        |  |  |  |

| bit 5-4      | bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |                  |               |                  |                  |                    |        |  |  |  |

|              | Contains a value from 0 to 2.                                            |                  |               |                  |                  |                    |        |  |  |  |

### REGISTER 27-6: RTCVAL (WHEN RTCPTR<1:0> = 01): WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### **REGISTER 27-7:** RTCVAL (WHEN RTCPTR<1:0> = 00): MINUTES AND SECONDS VALUE REGISTER

HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits

| U-0     | R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| —       | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| U-0     | R/W-x   |

| —       | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend. |         |         |         |         |         |         |         |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

bit 3-0

# REGISTER 28-3: PMADDR: PARALLEL MASTER PORT ADDRESS REGISTER (MASTER MODES ONLY)<sup>(1,2)</sup>

| R/W-0            | R/W-0                                                                                                                                                                      | R/W-0         | R/W-0       | R/W-0        | R/W-0            | R/W-0           | R/W-0 |