Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

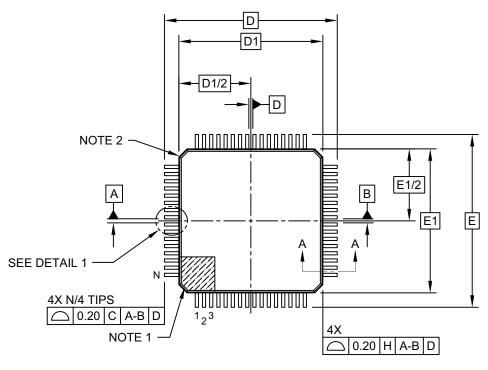

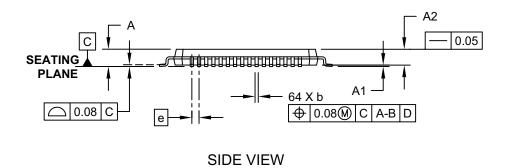

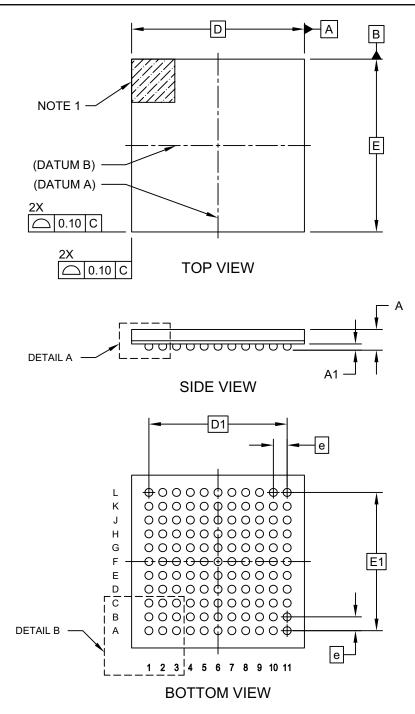

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm310-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADLL       | ABLE 4-3. INTERROFT CONTROLLER REGISTER MAP FOR USFIC33EFAAAGMISAA DEVICES (CONTINUED) |        |         |         |         |        |            |            |            |         |                       |                       |                       |         |         |         |         |               |

|-------------|----------------------------------------------------------------------------------------|--------|---------|---------|---------|--------|------------|------------|------------|---------|-----------------------|-----------------------|-----------------------|---------|---------|---------|---------|---------------|

| SFR<br>Name | Addr.                                                                                  | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10     | Bit 9      | Bit 8      | Bit 7   | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| IPC11       | 0856                                                                                   | _      | T6IP2   | T6IP1   | T6IP0   | —      | —          | _          | —          | _       | PMPIP2 <sup>(1)</sup> | PMPIP1 <sup>(1)</sup> | PMPIP0 <sup>(1)</sup> | —       | OC8IP2  | OC8IP1  | OC8IP0  | 4444          |

| IPC12       | 0858                                                                                   | _      | T8IP2   | T8IP1   | T8IP0   | _      | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | _       | SI2C2IP2              | SI2C2IP1              | SI2C2IP0              | _       | T7IP2   | T7IP1   | T7IP0   | 4444          |

| IPC13       | 085A                                                                                   | _      | _       | _       | _       | -      | INT4IP2    | INT4IP1    | INT4IP0    | -       | INT3IP2               | INT3IP1               | INT3IP0               | _       | T9IP2   | T9IP1   | T9IP0   | 4444          |

| IPC14       | 085C                                                                                   | _      | DCIEIP2 | DCIEIP1 | DCIEIP0 | _      | QEI1IP2    | QEI1IP2    | QEI1IP0    | _       | PCEPIP2               | PCEPIP1               | PCEPIP0               | _       | _       | _       | _       | 4444          |

| IPC15       | 085E                                                                                   | _      | FLT1IP2 | FLT1IP1 | FLT1IP0 |        | RTCCIP2(2) | RTCCIP1(2) | RTCCIP0(2) |         |                       | _                     | _                     | _       | DCIIP2  | DCIIP1  | DCIIP0  | 0404          |

| IPC16       | 0860                                                                                   | _      | CRCIP2  | CRCIP1  | CRCIP0  |        | U2EIP2     | U2EIP1     | U2EIP0     |         | U1EIP2                | U1EIP1                | U1EIP0                | _       | FLT2IP2 | FLT2IP1 | FLT2IP0 | 4440          |

| IPC18       | 0864                                                                                   | _      | C2TXIP2 | C2TXIP1 | C2TXIP0 |        | FLT3IP2    | FLT3IP1    | FLT3IP0    |         | PCESIP2               | PCESIP1               | PCESIP0               | _       | _       |         | _       | 4040          |

| IPC19       | 0866                                                                                   | _      | _       |         | _       |        | _          | -          | _          |         | CTMUIP2               | CTMUIP1               | CTMUIP0               | _       | FLT4IP2 | FLT4IP1 | FLT4IP0 | 0004          |

| IPC20       | 0868                                                                                   | _      | U3TXIP2 | U3TXIP1 | U3TXIP0 | _      | U3RXIP2    | U3RXIP1    | U3RXIP0    | _       | U3EIP2                | U3EIP1                | U3EIP0                | _       | _       | _       | _       | 0000          |

| IPC21       | 086A                                                                                   | _      | U4EIP2  | U4EIP1  | U4EIP0  |        | _          | -          | _          |         |                       | _                     | _                     | _       | _       |         | _       | 0000          |

| IPC22       | 086C                                                                                   | _      | SPI3IP2 | SPI3IP1 | SPI3IP0 |        | SPI3EIP2   | SPI3EIP1   | SPI3EIP0   |         | U4TXIP2               | U4TXIP1               | U4TXIP0               | _       | U4RXIP2 | U4RXIP1 | U4RXIP0 | 0000          |

| IPC23       | 086E                                                                                   | _      | PGC2IP2 | PGC2IP1 | PGC2IP0 |        | PWM1IP2    | PWM1IP1    | PWM1IP0    |         |                       | _                     | _                     | _       | _       |         | _       | 4400          |

| IPC24       | 0870                                                                                   | _      | PWM6IP2 | PWM6IP1 | PWM6IP0 |        | PWM5IP2    | PWM5IP1    | PWM5IP0    |         | PWM4IP2               | PWM4IP1               | PWM4IP0               | _       | PWM3IP2 | PWM3IP1 | PWM3IP0 | 4444          |

| IPC35       | 0886                                                                                   | _      | JTAGIP2 | JTAGIP1 | JTAGIP0 |        | ICDIP2     | ICDIP1     | ICDIP0     |         |                       | _                     | _                     | _       | _       |         | _       | 4400          |

| IPC36       | 0888                                                                                   | _      | PTG0IP2 | PTG0IP1 | PTG0IP0 | -      | PTGWDTIP2  | PTGWDTIP1  | PTGWDTIP0  |         | PTGSTEPIP2            | PTGSTEPIP1            | PTGSTEPIP0            | —       | _       |         | _       | 4440          |

| IPC37       | 088A                                                                                   | _      | _       | -       | _       | -      | PTG3IP2    | PTG3IP1    | PTG3IP0    |         | PTG2IP2               | PTG2IP1               | PTG2IP0               | _       | PTG1IP2 | PTG1IP1 | PTG1IP0 | 0444          |

| INTTREG     | 08C8                                                                                   | _      | —       |         | _       | ILR3   | ILR2       | ILR1       | ILR0       | VECNUM7 | VECNUM6               | VECNUM5               | VECNUM4               | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 | 0000          |

#### TABLE 4-3: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES (CONTINUED)

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PMPIF/PMPIE/PMPIPx flags are not available on 44-pin devices.

2: The RTCCIF/RTCCIE/RTCCIPx flags are not available on 44-pin devices.

| Name<br>Name<br>NameAddr.Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 20Bit 10Bit 20Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                       |       |       |       |        |            |              |              |            |            |        |        | MAP    | ISTER N | SREG   | TIMER  | 4-4:  | TABLE 4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|-------|-------|-------|--------|------------|--------------|--------------|------------|------------|--------|--------|--------|---------|--------|--------|-------|---------|

| PR1       0102       Period Register 1         TICON       0104       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM2       0106       -       Time?       Period Register       FORATE       TCKPS1       TCKPS1       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM3       0106       -       Time?       Register for 32-bit timer operations only)       -       TTSYNC       TCS       —         TRR3H_D       0106       -       -       Time?       Period Register 3       -       TCS       -       -       -       TGATE       TCKPS0       T32       -       TCS       -       -       -       TGATE       TCKPS0       TSD       -       TCS       -       -       -       TGATE       TCKPS0       TSD       -       TCS       -       -       TTSD       -       TCS       -       -       TGATE       TCKPS0       TSD       -       TCS       -       TTSD       -       TTSD       TCS       -       TTSD       TTSD       TTSD       TTSD       TTSD                                                                                                                                                                                                                                                                                     | All<br>Resets | Bit 0                 | Bit 1 | Bit 2 | Bit 3 | Bit 4  | Bit 5      | Bit 6        | Bit 7        | Bit 8      | Bit 9      | Bit 10 | Bit 11 | Bit 12 | Bit 13  | Bit 14 | Bit 15 | Addr. | -       |

| TICON       014//       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR2       0106       -       Timer2       Register       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR3       0106       -       Timer3       Register       -       TS2-bit filter operations only)       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       TCKPS0       T32       -       TCS       -       -       -       -       TCS       -       -       TCS       -       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       1       1       1                                                                                                                                                                                                                                                                                                                                      | 0000          |                       |       |       |       |        |            | r            | er1 Registe  | Tim        |            |        |        |        |         |        |        | 0100  | TMR1    |

| TMR2       0.106       Timer2 Register         TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       0100       Period Register 2         PR2       0100       Period Register 2         PR3       0110       TON       -       TSIDL       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4HD       0110       TON       -       TSIDL       -       -       -       -       TGCR       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5HD       0116       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5HD                                                                                                                                                                                                                                                                                                                               | FFFF          | Period Register 1     |       |       |       |        |            |              |              |            |            |        | 0102   | PR1    |         |        |        |       |         |

| TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       010A       Timer3 Register         PR2       010C       Period Register 2         PR3       0100       Period Register 2         PR3       0100       Timer3 Register 2         PR3       0100       Timer3 Register 2         PR3       0110       TON -       TISDL -       -       Period Register 1         TMR4       0110       ToN -       Timer3 Register         TMR4       0114       Timer5 Holding Register (For 32-bit timer operations only)         TMR5       OTIR       TIMEr5 Register         TMR5       OTIR       ToKPS1       TCKPS1                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0000          | _                     | TCS   | TSYNC | —     | TCKPS0 | TCKPS1     | TGATE        |              | _          | _          | _      | —      | _      | TSIDL   | _      | TON    | 0104  | T1CON   |

| TMR3       010A       Timer3 Register 7         PR2       010C       Period Register 3         TZCON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0114       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0118       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       <                                                                                                                                                                                                                                                                                                                                                 | 0000          | -                     |       |       |       |        |            | r            | er2 Registe  | Tim        |            |        |        |        |         |        |        | 0106  | TMR2    |

| PR2       010C       Period Register 2         PR3       010E       Period Register 3         T2CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR5HLD       0118       -       -       -       -       -       Period Register 4       Period Register 4         PR5       0110       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       -       TSIDL       -       -       -       -       TGA                                                                                                                                                                                                                                                                                                                                                     | xxxx          |                       |       |       |       |        | ions only) | timer operat | (For 32-bit  | g Register | er3 Holdin | Time   |        |        |         |        |        | 0108  | TMR3HLD |

| PR3         010E         Period Register 3           T2CON         0110         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR5         0116         -         -         Timer5 Holding Register (For 32-bit timer operations only)         -         TCS         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           PR4         0114         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T4CON         0112         TON                                                                                                                                                                                                                                | 0000          | Timer3 Register 000   |       |       |       |        |            |              |              |            |            | 010A   | TMR3   |        |         |        |        |       |         |

| T2CON         0110         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS1         TCKPS0         -         -         TCS         -           TMR4         0114         -         -         -         -         TGS0         -         -         TCS         10116         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -         -         TCS         -         TCS         -         TCS         -         TCS         -         TCS         -         TCS         10112         TCS         TCS         10116         TCS <td>FFFF</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>2</td> <td>od Register</td> <td>Peri</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>010C</td> <td>PR2</td> | FFFF          |                       |       |       |       |        |            | 2            | od Register  | Peri       |            |        |        |        |         |        |        | 010C  | PR2     |

| T3CON     0112     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS0     —     —     —     TCS     —       TMR4     0114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FFFF          |                       |       |       |       |        |            | 3            | od Register  | Peri       |            |        |        |        |         |        |        | 010E  | PR3     |

| TMR4     0114     Immediate     Timer4 Register       TMR4LD     0116     Timer5 Holding Register (For 32-bit timer operations only)       TMR5     0118       PR4     011A       PR5     011C       TMR6     012       TMR6     012       TMR7     012       TMR7     012       PR6     012       TMR7     0126       TMR7     0126       PR7     0128       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR7     0126       PR7     0128       PR7     0124       TMR7     0126       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000          | —                     | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _            | _          |            | —      | —      |        | TSIDL   |        | TON    | 0110  | T2CON   |

| TMRSHLD       0116       TimerS Holding Register (For 32-bit timer operations only)         TMRS       0118       TimerS Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T5CON       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0122       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR7       0126       Timer7 Holding Register (For 32-bit timer operations only)       TImer7 Register       Period Register 6         PR7       012A       TSIDL       -       -       -       -       TGATE       TCKPS0       T32                                                                                                                                                                                                                                                                                                  | 0000          | —                     | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | _            | _          |            | —      | —      |        | TSIDL   |        | TON    | 0112  | T3CON   |

| TMR5       0118       Timer5 Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T4CON       011E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       —       —       —       —       —       —       —       —       TCS       —       —       —       —       —       —       TCS       P       P       P       P       P       P       P       P       P       P <t< td=""><td>0000</td><td></td><td></td><td></td><td></td><td></td><td></td><td>r</td><td>er4 Registe</td><td>Tim</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0114</td><td>TMR4</td></t<>                                                                                                                                         | 0000          |                       |       |       |       |        |            | r            | er4 Registe  | Tim        |            |        |        |        |         |        |        | 0114  | TMR4    |

| PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR7       0126       Timer7 Holding Register (For 32-bit timer operations only)       TImer7 Register       Period Register 6       Period Register       Period Register       Period Register       TCKPS0       T32       —       TCS       —         T6CON       012C       TON       —       TSIDL       —       —                                                                                                                                                                                                                                                                                        | xxxx          |                       |       |       |       |        | ions only) | timer operat | (For 32-bit  | g Register | er5 Holdin | Time   |        |        |         |        |        | 0116  | TMR5HLD |

| PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0000          |                       |       |       |       |        |            | r            | er5 Registe  | Tim        |            |        |        |        |         |        |        | 0118  | TMR5    |

| T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FFFF          | Period Register 4 F   |       |       |       |        |            |              |              |            | 011A       | PR4    |        |        |         |        |        |       |         |

| T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FFFF          | Period Register 5     |       |       |       |        |            |              |              |            | 011C       | PR5    |        |        |         |        |        |       |         |

| TMR6       0122       Timer6 Register         TMR7HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                             | 0000          | —                     | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —            |            |            | —      | —      |        | TSIDL   | -      | TON    | 011E  | T4CON   |

| TMR7 HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       0122       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000          | —                     | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | —            |            |            | —      | —      |        | TSIDL   |        | TON    | 0120  | T5CON   |

| TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>0000</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>r</td> <td>ier6 Registe</td> <td>Tim</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0122</td> <td>TMR6</td>                                                                                                                                   | 0000          |                       |       |       |       |        |            | r            | ier6 Registe | Tim        |            |        |        |        |         |        |        | 0122  | TMR6    |

| PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       —       TSIDL       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR8       0130       —       TSIDL       —       —       —       —       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | xxxx          |                       |       |       |       |        | ions only) | timer operat | For 32-bit   | g Register | er7 Holdin | Time   |        |        |         |        |        | 0124  | TMR7HLD |

| PR7         012A         Period Register 7           T6CON         012C         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR8         0130         -         TSIDL         -         -         -         TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000          |                       |       |       |       |        |            | r            | er7 Registe  | Tim        |            |        |        |        |         |        |        | 0126  | TMR7    |

| T6CON     012C     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FFFF          |                       |       |       |       |        |            | 6            | od Register  | Peri       |            |        |        |        |         |        |        | 0128  | PR6     |

| T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FFFF          |                       |       |       |       |        |            | 7            | od Register  | Peri       |            |        |        |        |         |        |        | 012A  | PR7     |

| TMR8 0130 Timer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000          | —                     | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —            | —          | _          | —      | —      | —      | TSIDL   | _      | TON    | 012C  | T6CON   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0000          | —                     | TCS   | —     | _     | TCKPS0 | TCKPS1     | TGATE        | _            | —          | _          | —      | —      | —      | TSIDL   | _      | TON    | 012E  | T7CON   |

| TMR9HLD 0132 Timer9 Holding Register (For 32-bit timer operations only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0000          |                       |       |       |       |        |            | r            | er8 Registe  | Tim        |            |        |        |        |         |        |        | 0130  | TMR8    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xxxx          |                       |       |       |       |        | ions only) | timer operat | For 32-bit   | g Register | er9 Holdin | Time   |        |        |         |        |        | 0132  | TMR9HLD |

| TMR9     0134     Timer9 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0000          |                       |       |       |       |        |            | r            | er9 Registe  | Tim        |            |        |        |        |         |        |        | 0134  | TMR9    |

| PR8 0136 Period Register 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FFFF          |                       |       |       |       |        |            | 8            | od Register  | Peri       |            |        |        |        |         |        |        | 0136  | PR8     |

| PR9 0138 Period Register 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FFFF          | Period Register 9 FFF |       |       |       |        |            |              |              | 0138       | PR9        |        |        |        |         |        |        |       |         |

| T8CON         013A         TON         —         TSIDL         —         —         —         —         TGATE         TCKPS1         TCKPS0         T32         —         TCS         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0000          | -                     | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _            | _          | _          | _      | —      | _      | TSIDL   | _      | TON    | 013A  | T8CON   |

| T9CON     013C     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0000          | -                     | TCS   | -     | _     | TCKPS0 | TCKPS1     | TGATE        | _            | _          | _          | _      | —      | _      | TSIDL   | _      | TON    | 013C  | T9CON   |

dsPIC33EPXXXGM3XX/6XX/7XX

#### TABLE 4-4: TIMERS REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE       | 4-34: | PERI   | PHERA        | L PIN 5 | ELECI  | INFUI     | REGISI |       | P FUR C | ISPIC33     |             |           | DEVICE | 3          |       |       |       |               |  |      |

|-------------|-------|--------|--------------|---------|--------|-----------|--------|-------|---------|-------------|-------------|-----------|--------|------------|-------|-------|-------|---------------|--|------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8   | Bit 7       | Bit 6       | Bit 5     | Bit 4  | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |  |      |

| RPINR0      | 06A0  | _      |              |         |        | NT1R<6:0  | >      |       |         | _           | —           |           | —      | —          | —     | —     | _     | 0000          |  |      |

| RPINR1      | 06A2  | _      | —            | —       | —      | —         | _      | _     | —       | _           | INT2R<6:0>  |           |        |            |       |       | 0000  |               |  |      |

| RPINR3      | 06A6  | _      | _            | _       | —      | —         | _      | _     | _       | _           | T2CKR<6:0>  |           |        |            |       |       | 0000  |               |  |      |

| RPINR7      | 06AE  | —      |              |         |        | IC2R<6:0> | •      |       |         | _           | IC1R<6:0>   |           |        |            |       |       | 0000  |               |  |      |

| RPINR8      | 06B0  | —      |              |         |        | IC4R<6:0> | •      |       |         | _           |             |           |        | IC3R<6:0>  |       |       |       | 0000          |  |      |

| RPINR9      | 06B2  | —      |              |         |        | IC6R<6:0> | •      |       |         |             |             |           |        | IC5R<6:0>  |       |       |       | 0000          |  |      |

| RPINR10     | 06B4  | —      |              |         |        | IC8R<6:0> | •      |       |         | _           |             |           |        | IC7R<6:0>  |       |       |       | 0000          |  |      |

| RPINR11     | 06B6  | —      | —            | _       |        |           | _      |       |         |             |             |           | (      | OCFAR<6:0  | >     |       |       | 0000          |  |      |

| RPINR12     | 06B8  | _      |              |         | I      | -LT2R<6:0 | >      |       |         | _           | FLT1R<6:0>  |           |        |            |       | 0000  |       |               |  |      |

| RPINR14     | 06BC  | —      |              |         | C      | QEB1R<6:0 | )>     |       |         | _           | QEA1R<6:0>  |           |        |            |       |       |       |               |  | 0000 |

| RPINR15     | 06BE  | _      | HOME1R<6:0>  |         |        |           |        |       | _       | INDX1R<6:0> |             |           |        |            | 0000  |       |       |               |  |      |

| RPINR16     | 06C0  | _      |              |         | C      | QEB2R<6:0 | )>     |       |         | _           | QEA2R<6:0>  |           |        |            |       | 0000  |       |               |  |      |

| RPINR17     | 06C2  | _      |              |         | H      | OME2R<6:  | 0>     |       |         | _           | INDX2R<6:0> |           |        |            |       | 0000  |       |               |  |      |

| RPINR18     | 06C4  | _      | —            | _       |        |           | —      |       |         | _           | U1RXR<6:0>  |           |        |            | 0000  |       |       |               |  |      |

| RPINR19     | 06C6  | —      | —            | —       |        |           | —      |       |         | _           | U2RXR<6:0>  |           |        |            |       | 0000  |       |               |  |      |

| RPINR22     | 06CC  | —      |              |         | 9      | SCK2R<6:0 | )>     |       |         |             | SDI2R<6:0>  |           |        |            | 0000  |       |       |               |  |      |

| RPINR23     | 06CE  | —      | _            | _       |        |           | _      |       |         | _           |             |           |        | SS2R<6:0>  |       |       |       | 0000          |  |      |

| RPINR24     | 06D0  | —      |              |         | C      | SCKR<6:0  | )>     |       |         | _           |             |           |        | CSDIR<6:0> | >     |       |       | 0000          |  |      |

| RPINR25     | 06D2  | —      | _            | _       |        |           | _      |       |         | _           |             |           | (      | COFSR<6:0  | >     |       |       | 0000          |  |      |

| RPINR27     | 06D6  | —      |              |         | U      | 3CTSR<6:  | 0>     |       |         | _           |             |           | ι      | J3RXR<6:0  | >     |       |       | 0000          |  |      |

| RPINR28     | 06D8  | —      |              |         | U      | 4CTSR<6:  | 0>     |       |         | _           |             |           | ι      | J4RXR<6:0  | >     |       |       | 0000          |  |      |

| RPINR29     | 06DA  | —      |              |         | 5      | SCK3R<6:0 | >      |       |         | _           |             |           |        | SDI3R<6:0> | •     |       |       | 0000          |  |      |

| RPINR30     | 06DC  | —      | —            | —       | _      | —         | —      | _     | _       | _           |             |           |        | SS3R<6:0>  |       |       |       | 0000          |  |      |

| RPINR37     | 06EA  | _      |              |         | S      | YNCI1R<6: | 0>     |       |         | —           | —           | _         | —      | —          | _     | —     | —     | 0000          |  |      |

| RPINR38     | 06EC  | _      |              |         | DT     | CMP1R<6   | :0>    |       |         | —           | _           | _         | —      | _          | —     |       | —     | 0000          |  |      |

| RPINR39     | 06EE  | _      |              |         | DT     | CMP3R<6   | :0>    |       |         | —           |             |           | D      | TCMP2R<6:  | 0>    |       |       | 0000          |  |      |

| RPINR40     | 06F0  | _      | DTCMP5R<6:0> |         |        |           |        | _     |         |             | D           | TCMP4R<6: | 0>     |            |       | 0000  |       |               |  |      |

| RPINR41     | 06F2  | —      | —            | —       | _      | —         | —      | _     | —       | —           |             |           | D      | TCMP6R<6:  | 0>    |       |       | 0000          |  |      |

#### TABLE 4-34: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

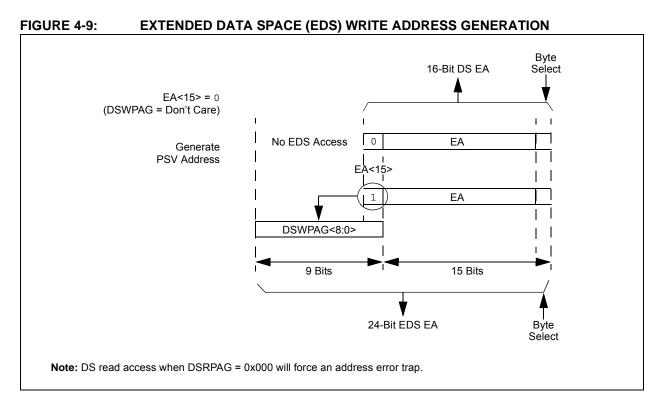

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Figure 4-10.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

## 11.5 High-Voltage Detect

The dsPIC33EPXXXGM3XX/6XX/7XX devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tri-state condition. The device remains in this I/O tristate condition as long as the high-voltage condition is present.

## 11.6 I/O Helpful Tips

- In some cases, certain pins, as defined in Table 33-10 under "Injection Current", have internal protection diodes to VDD and VSs. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 33.0 "Electrical Characteristics"** for additional information.

| R/W-0<br>R/W-0                         | R/W-0<br>R/W-0<br>W = Writable H<br>'1' = Bit is set<br>ted: Read as '0        |                                                                                                                                                                      | R/W-0<br>DTCMP5R<6:(<br>R/W-0<br>DTCMP4R<6:(<br>U = Unimplen<br>'0' = Bit is cle                        | R/W-0<br>)>                                                                                                                                                                                                   | R/W-0<br>R/W-0<br>d as '0'<br>x = Bit is unkr                                                                                                                                                                                                               | R/W-0<br>bit 8<br>R/W-0<br>bit 0                                                                                                                                                                                                                                          |

|----------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | R/W-0<br>DTCMP4R<6:(<br>U = Unimplen                                                                    | R/W-0<br>)>                                                                                                                                                                                                   | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                            | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |