Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, Motor Control PWM, POR, PWM, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm310-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| dsPI( | C33EPXXXGM3XX/6XX/7XX Product Family                                      | 2   |

|-------|---------------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                           |     |

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers     | 21  |

| 3.0   | CPU                                                                       | 27  |

| 4.0   | Memory Organization                                                       | 37  |

| 5.0   | Flash Program Memory                                                      | 103 |

| 6.0   | Resets                                                                    | 111 |

| 7.0   | Interrupt Controller                                                      | 115 |

| 8.0   | Direct Memory Access (DMA)                                                | 129 |

| 9.0   | Oscillator Configuration                                                  | 143 |

| 10.0  | Power-Saving Features                                                     | 153 |

| 11.0  | I/O Ports                                                                 | 163 |

| 12.0  | Timer1                                                                    | 211 |

| 13.0  | Timer2/3, Timer4/5, Timer6/7 and Timer8/9                                 | 213 |

| 14.0  | Input Capture                                                             | 219 |

| 15.0  | Output Compare                                                            | 223 |

| 16.0  | High-Speed PWM Module                                                     | 229 |

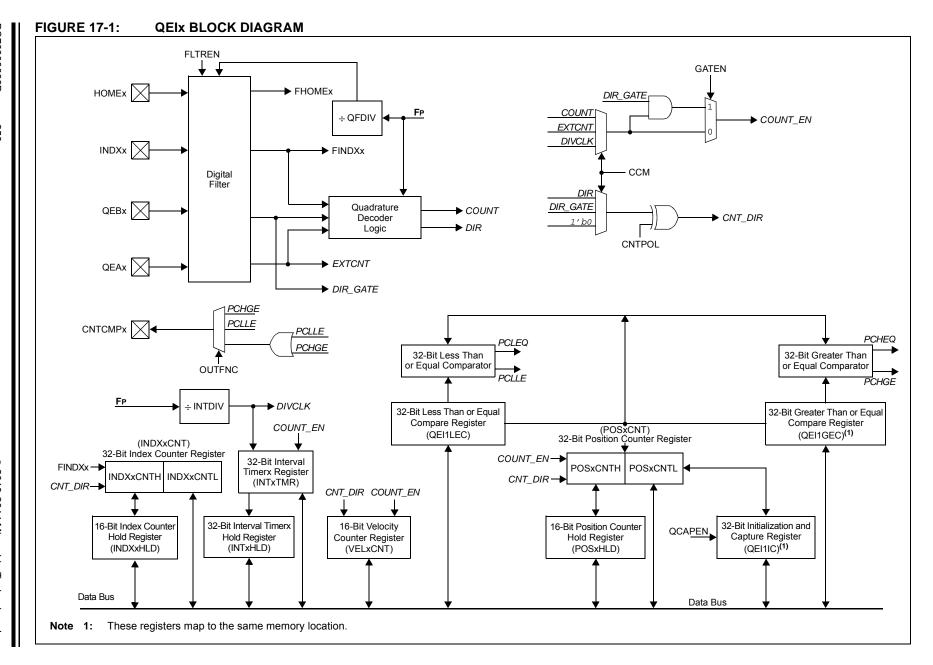

|       | Quadrature Encoder Interface (QEI) Module                                 |     |

| 18.0  | Serial Peripheral Interface (SPI)                                         |     |

| 19.0  |                                                                           |     |

|       | Universal Asynchronous Receiver Transmitter (UART)                        |     |

|       | Controller Area Network (CAN) Module (dsPIC33EPXXXGM6XX/7XX Devices Only) |     |

| 22.0  | Charge Time Measurement Unit (CTMU)                                       | 321 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                           | 327 |

| 24.0  | Data Converter Interface (DCI) Module                                     | 343 |

| 25.0  | Peripheral Trigger Generator (PTG) Module                                 | 349 |

| 26.0  | Op Amp/Comparator Module                                                  | 365 |

| 27.0  | Real-Time Clock and Calendar (RTCC)                                       | 383 |

|       | Parallel Master Port (PMP)                                                |     |

|       | Programmable Cyclic Redundancy Check (CRC) Generator                      |     |

| 30.0  | Special Features                                                          | 411 |

|       | Instruction Set Summary                                                   |     |

|       | Development Support                                                       |     |

| 33.0  | Electrical Characteristics                                                |     |

| 34.0  | High-Temperature Electrical Characteristics                               | 499 |

|       | Packaging Information                                                     |     |

| Appe  | endix A: Revision History                                                 | 527 |

|       | X                                                                         |     |

| The I | Microchip Web Site                                                        | 537 |

|       | omer Change Notification Service                                          |     |

| Custo | omer Support                                                              | 537 |

| Prod  | uct Identification System                                                 | 539 |

#### 1.0 DEVICE OVERVIEW

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGM3XX/6XX/7XX Digital Signal Controller (DSC) devices.

dsPIC33EPXXXGM3XX/6XX/7XX devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

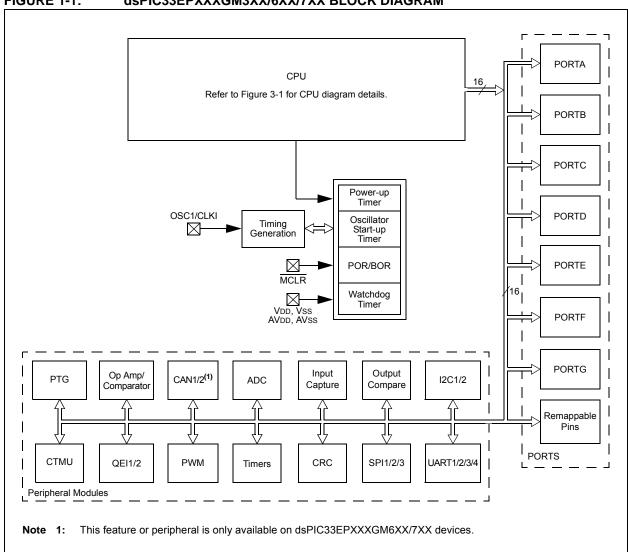

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGM3XX/6XX/7XX BLOCK DIAGRAM

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB® PICkit™ 3, MPLAB ICD 3, or MPLAB REAL ICF™.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB® ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB® REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 9.0** "Oscillator Configuration" for details.

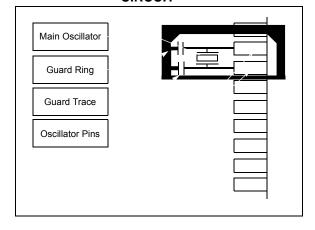

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

FIGURE 2-3: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER<sup>(3)</sup> (CONTINUED)

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

bit 2 SFA: Stack Frame Active Status bit

1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values

0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space

bit 1 RND: Rounding Mode Select bit

1 = Biased (conventional) rounding is enabled

0 = Unbiased (convergent) rounding is enabled

IF: Integer or Fractional Multiplier Mode Select bit

1 = Integer mode is enabled for DSP multiply0 = Fractional mode is enabled for DSP multiply

Note 1: This bit is always read as '0'.

bit 0

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

3: Refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359) for more detailed information.

TABLE 4-3: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES (CONTINUED)

| SFR<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10                 | Bit 9                  | Bit 8                  | Bit 7   | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|---------|---------|---------|--------|------------------------|------------------------|------------------------|---------|-----------------------|-----------------------|-----------------------|---------|---------|---------|---------|---------------|

| IPC11       | 0856  | _      | T6IP2   | T6IP1   | T6IP0   | _      | _                      | _                      | _                      | _       | PMPIP2 <sup>(1)</sup> | PMPIP1 <sup>(1)</sup> | PMPIP0 <sup>(1)</sup> | 1       | OC8IP2  | OC8IP1  | OC8IP0  | 4444          |

| IPC12       | 0858  | _      | T8IP2   | T8IP1   | T8IP0   | _      | MI2C2IP2               | MI2C2IP1               | MI2C2IP0               | _       | SI2C2IP2              | SI2C2IP1              | SI2C2IP0              | -       | T7IP2   | T7IP1   | T7IP0   | 4444          |

| IPC13       | 085A  | _      | -       | -       | _       | _      | INT4IP2                | INT4IP1                | INT4IP0                | 1       | INT3IP2               | INT3IP1               | INT3IP0               | ı       | T9IP2   | T9IP1   | T9IP0   | 4444          |

| IPC14       | 085C  | _      | DCIEIP2 | DCIEIP1 | DCIEIP0 | _      | QEI1IP2                | QEI1IP2                | QEI1IP0                | 1       | PCEPIP2               | PCEPIP1               | PCEPIP0               | ı       | ı       | 1       | _       | 4444          |

| IPC15       | 085E  | _      | FLT1IP2 | FLT1IP1 | FLT1IP0 | _      | RTCCIP2 <sup>(2)</sup> | RTCCIP1 <sup>(2)</sup> | RTCCIP0 <sup>(2)</sup> | 1       | _                     | _                     | 1                     | ı       | DCIIP2  | DCIIP1  | DCIIP0  | 0404          |

| IPC16       | 0860  | _      | CRCIP2  | CRCIP1  | CRCIP0  | _      | U2EIP2                 | U2EIP1                 | U2EIP0                 | 1       | U1EIP2                | U1EIP1                | U1EIP0                | ı       | FLT2IP2 | FLT2IP1 | FLT2IP0 | 4440          |

| IPC18       | 0864  | _      | C2TXIP2 | C2TXIP1 | C2TXIP0 | _      | FLT3IP2                | FLT3IP1                | FLT3IP0                | 1       | PCESIP2               | PCESIP1               | PCESIP0               | ı       | ı       | 1       | _       | 4040          |

| IPC19       | 0866  | _      | -       | ı       | _       | _      | _                      | _                      | _                      | 1       | CTMUIP2               | CTMUIP1               | CTMUIP0               | ı       | FLT4IP2 | FLT4IP1 | FLT4IP0 | 0004          |

| IPC20       | 0868  | _      | U3TXIP2 | U3TXIP1 | U3TXIP0 | _      | U3RXIP2                | U3RXIP1                | U3RXIP0                | 1       | U3EIP2                | U3EIP1                | U3EIP0                | ı       | ı       | 1       | _       | 0000          |

| IPC21       | 086A  | _      | U4EIP2  | U4EIP1  | U4EIP0  | _      | _                      | _                      | _                      | _       | _                     | _                     | 1                     | 1       | _       | _       | _       | 0000          |

| IPC22       | 086C  | _      | SPI3IP2 | SPI3IP1 | SPI3IP0 | _      | SPI3EIP2               | SPI3EIP1               | SPI3EIP0               | _       | U4TXIP2               | U4TXIP1               | U4TXIP0               | -       | U4RXIP2 | U4RXIP1 | U4RXIP0 | 0000          |

| IPC23       | 086E  | _      | PGC2IP2 | PGC2IP1 | PGC2IP0 | _      | PWM1IP2                | PWM1IP1                | PWM1IP0                | _       | _                     | _                     | -                     | -       | _       | _       | _       | 4400          |

| IPC24       | 0870  | _      | PWM6IP2 | PWM6IP1 | PWM6IP0 | _      | PWM5IP2                | PWM5IP1                | PWM5IP0                | _       | PWM4IP2               | PWM4IP1               | PWM4IP0               | -       | PWM3IP2 | PWM3IP1 | PWM3IP0 | 4444          |

| IPC35       | 0886  | _      | JTAGIP2 | JTAGIP1 | JTAGIP0 | _      | ICDIP2                 | ICDIP1                 | ICDIP0                 | _       | _                     | _                     | -                     | -       | _       | _       | _       | 4400          |

| IPC36       | 0888  | _      | PTG0IP2 | PTG0IP1 | PTG0IP0 | _      | PTGWDTIP2              | PTGWDTIP1              | PTGWDTIP0              | 1       | PTGSTEPIP2            | PTGSTEPIP1            | PTGSTEPIP0            | ı       | ı       | ı       | _       | 4440          |

| IPC37       | 088A  | _      | -       | -       | _       | _      | PTG3IP2                | PTG3IP1                | PTG3IP0                | 1       | PTG2IP2               | PTG2IP1               | PTG2IP0               | ı       | PTG1IP2 | PTG1IP1 | PTG1IP0 | 0444          |

| INTTREG     | 08C8  | _      | _       | _       | _       | ILR3   | ILR2                   | ILR1                   | ILR0                   | VECNUM7 | VECNUM6               | VECNUM5               | VECNUM4               | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PMPIF/PMPIE/PMPIPx flags are not available on 44-pin devices.

2: The RTCCIF/RTCCIE/RTCCIPx flags are not available on 44-pin devices.

#### **REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER**

| U-0    | U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |  |  |

|--------|--------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| _      | _            | _   | _   | _   | _   | _   | _   |  |  |  |  |

| bit 15 | bit 15 bit 8 |     |     |     |     |     |     |  |  |  |  |

| U-0   | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3 PPST3: Channel 3 Ping-Pong Mode Status Flag bit

1 = DMA3STB register is selected0 = DMA3STA register is selected

bit 2 PPST2: Channel 2 Ping-Pong Mode Status Flag bit

1 = DMA2STB register is selected0 = DMA2STA register is selected

bit 1 PPST1: Channel 1 Ping-Pong Mode Status Flag bit

1 = DMA1STB register is selected0 = DMA1STA register is selected

bit 0 PPST0: Channel 0 Ping-Pong Mode Status Flag bit

1 = DMA0STB register is selected0 = DMA0STA register is selected

TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

| TABLE 11-2: INP                                  | UI FIN 3         | ELECTION FOR SEL |

|--------------------------------------------------|------------------|------------------|

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment   |

| 010 1001                                         | I/O              | RP41             |

| 010 1010                                         | I/O              | RP42             |

| 010 1011                                         | I/O              | RP43             |

| 101 1000                                         | _                | _                |

| 101 1001                                         | _                | _                |

| 101 1010                                         |                  | _                |

| 101 1011                                         | _                | _                |

| 101 1100                                         | _                | _                |

| 101 1101                                         | _                | _                |

| 101 1110                                         | I                | RPI94            |

| 101 1111                                         | I                | RPI95            |

| 110 0000                                         | I                | RPI96            |

| 110 0001                                         | I/O              | RP97             |

| 110 0010                                         | _                | _                |

| 110 0011                                         | _                | _                |

| 110 0100                                         | _                | _                |

| 110 0101                                         | _                | _                |

| 110 0110                                         | _                | _                |

| 110 0111                                         | _                | _                |

| 110 1000                                         | _                | _                |

| 110 1001                                         | _                | _                |

| 110 1010                                         | _                | _                |

| 110 1011                                         | _                | _                |

|                                                  |                  | <u> </u>       |

|--------------------------------------------------|------------------|----------------|

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

| 101 0101                                         | _                | _              |

| 101 0110                                         | _                | _              |

| 101 0111                                         | _                |                |

| 110 1100                                         | _                |                |

| 110 1101                                         |                  |                |

| 110 1110                                         |                  |                |

| 110 1111                                         | _                |                |

| 111 0000                                         | I                | RPI112         |

| 111 0001                                         | I/O              | RP113          |

| 111 0010                                         | _                |                |

| 111 0011                                         | _                | _              |

| 111 0100                                         | _                | _              |

| 111 0101                                         | _                | _              |

| 111 0110                                         | I/O              | RP118          |

| 111 0111                                         | I                | RPI119         |

| 111 1000                                         | I/O              | RP120          |

| 111 1001                                         | I                | RPI121         |

| 111 1010                                         | _                | _              |

| 111 1011                                         | _                | _              |

| 111 1100                                         | I                | RPI124         |

| 111 1101                                         | I/O              | RP125          |

| 111 1110                                         | I/O              | RP126          |

| 111 1111                                         | I/O              | RP127          |

**Legend:** Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

#### REGISTER 11-21: RPINR27: PERIPHERAL PIN SELECT INPUT REGISTER 27

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | U3CTSR<6:0 | >     |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------|------------|-------|-------|-------|-------|-------|--|--|--|

| _     |       | U3RXR<6:0> |       |       |       |       |       |  |  |  |

| bit 7 |       |            |       |       |       |       | bit 0 |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 **U3CTSR<6:0>:** Assign UART3 Clear-to-Send (U3CTS) to the Corresponding RPn/RPIn Pin bits

(see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP124

•

.

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 U3RXR<6:0>: Assign UART3 Receive (U3RX) to the Corresponding RPn/RPIn Pin bits

(see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP124

•

•

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

#### REGISTER 11-28: RPINR40: PERIPHERAL PIN SELECT INPUT REGISTER 40

| U-0    | R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-------|--------------|-------|-------|-------|-------|-------|--|--|

| _      |       | DTCMP5R<6:0> |       |       |       |       |       |  |  |

| bit 15 |       |              |       |       |       |       | bit 8 |  |  |

| U-0   | R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------|--------------|-------|-------|-------|-------|-------|--|--|--|

| _     |       | DTCMP4R<6:0> |       |       |       |       |       |  |  |  |

| bit 7 |       |              |       |       |       |       | bit 0 |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 **DTCMP5R<6:0>:** Assign PWM Dead-Time Compensation Input 5 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111100 = Input tied to RPI124

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 **DTCMP4R<6:0>:** Assign PWM Dead-Time Compensation Input 4 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111100 = Input tied to RPI124

•

\_

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

#### REGISTER 11-32: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|--|

| _      | _   |       | RP39R<5:0> |       |       |       |       |  |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |  |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP38  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP39R<5:0>: Peripheral Output Function is Assigned to RP39 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-33: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP41R<5:0>: Peripheral Output Function is Assigned to RP41 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP40R<5:0>: Peripheral Output Function is Assigned to RP40 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### **REGISTER 17-3: QEIXSTAT: QEIX STATUS REGISTER**

| U-0    | U-0 | HS, R/C-0 | R/W-0    | HS, R/C-0 | R/W-0    | HS, R/C-0 | R/W-0    |

|--------|-----|-----------|----------|-----------|----------|-----------|----------|

| _      | _   | PCHEQIRQ  | PCHEQIEN | PCLEQIRQ  | PCLEQIEN | POSOVIRQ  | POSOVIEN |

| bit 15 |     |           |          |           |          |           | bit 8    |

| HS, R/C-0             | R/W-0  | HS, R/C-0 | R/W-0    | HS, R/C-0 | R/W-0  | HS, R/C-0 | R/W-0  |

|-----------------------|--------|-----------|----------|-----------|--------|-----------|--------|

| PCIIRQ <sup>(1)</sup> | PCIIEN | VELOVIRQ  | VELOVIEN | HOMIRQ    | HOMIEN | IDXIRQ    | IDXIEN |

| bit 7                 |        |           |          |           |        |           | bit 0  |

| <b>Legend:</b> HS = Hardware Settable bit |                  | C = Clearable bit                  |                    |  |  |

|-------------------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit                          | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                         | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-14 **Unimplemented:** Read as '0'

bit 13 PCHEQIRQ: Position Counter Greater Than or Equal Compare Status bit

1 = POSxCNT ≥ QEIxGEC 0 = POSxCNT < QEIxGEC

bit 12 **PCHEQIEN:** Position Counter Greater Than or Equal Compare Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 11 PCLEQIRQ: Position Counter Less Than or Equal Compare Status bit

1 = POSxCNT ≤ QEIxLEC 0 = POSxCNT > QEIxLEC

bit 10 PCLEQIEN: Position Counter Less Than or Equal Compare Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 9 **POSOVIRQ:** Position Counter Overflow Status bit

1 = Overflow has occurred0 = No overflow has occurred

bit 8 POSOVIEN: Position Counter Overflow Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 7 PCIIRQ: Position Counter (Homing) Initialization Process Complete Status bit<sup>(1)</sup>

1 = POSxCNT was reinitialized 0 = POSxCNT was not reinitialized

bit 6 PCIIEN: Position Counter (Homing) Initialization Process Complete interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 5 **VELOVIRQ:** Velocity Counter Overflow Status bit

1 = Overflow has occurred0 = No overflow has occurred

bit 4 **VELOVIEN:** Velocity Counter Overflow Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 3 **HOMIRQ:** Status Flag for Home Event Status bit

1 = Home event has occurred0 = No home event has occurred

**Note 1:** This status bit is only applicable to PIMOD<2:0> = 011 and 100 modes.

#### REGISTER 17-6: POSxHLD: POSITION COUNTER x HOLD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| POSHLD<15:8> |       |       |       |       |       |       |       |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| POSHLD<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **POSHLD<15:0>:** Holding Register for Reading and Writing POSxCNT bits

#### REGISTER 17-7: VELxCNT: VELOCITY COUNTER x REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| VELCNT<15:8> |       |       |       |       |       |       |       |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| VELCNT<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **VELCNT<15:0>:** Velocity Counter x bits

## 19.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit™ (I²C™)" (DS70000195), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains two Inter-Integrated Circuit ( $I^2C$ ) modules: I2C1 and I2C2.

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- · The SCLx pin is clock.

- · The SDAx pin is data.

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C Interface Supporting both Master and Slave modes of Operation.

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Port Allows Bidirectional Transfers Between Master and Slaves.

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control).

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly.

- Intelligent Platform Management Interface (IPMI) Support

- · System Management Bus (SMBus) Support

#### REGISTER 21-8: CxEC: CANx TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2 | RERRCNT1 | RERRCNT0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **TERRCNT<7:0>:** Transmit Error Count bits bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CxCFG1: CANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-6 **SJW<1:0>:** Synchronization Jump Width bits

11 = Length is 4 x TQ 10 = Length is 3 x TQ

01 = Length is 2 x TQ

$00 = \text{Length is } 1 \times \text{TQ}$

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

11 1111 = TQ = 2 x 64 x 1/FCAN

•

.

00 0010 =  $TQ = 2 \times 3 \times 1/FCAN$

00 0001 = TQ = 2 x 2 x 1/FCAN

00 0000 =  $TQ = 2 \times 1 \times 1/FCAN$

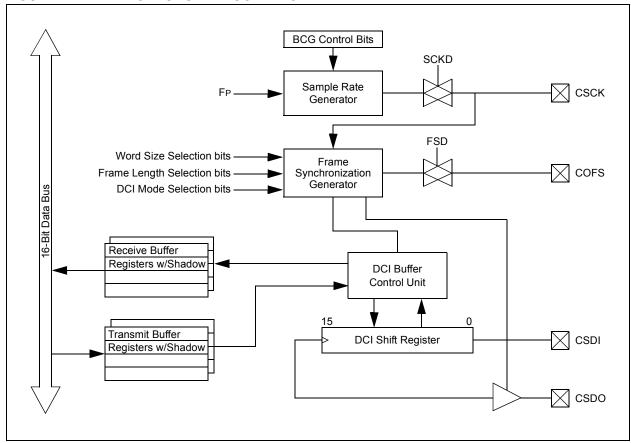

## 24.0 DATA CONVERTER INTERFACE (DCI) MODULE

- Note 1: This data sheet is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Data Converter Interface (DCI) Module" (DS70356), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 24.1 Module Introduction

The Data Converter Interface (DCI) module allows simple interfacing of devices, such as audio coder/decoders (Codecs), ADC and D/A Converters. The following interfaces are supported:

- Framed Synchronous Serial Transfer (Single or Multi-Channel)

- Inter-IC Sound (I<sup>2</sup>S) Interface

- · AC-Link Compliant mode

#### General features include:

- · Programmable word size up to 16 bits

- Supports up to 16 time slots, for a maximum frame size of 256 bits

- Data buffering for up to 4 samples without CPU overhead

#### FIGURE 24-1: DCI MODULE BLOCK DIAGRAM

# REGISTER 27-8: ALRMVAL (WHEN ALRMPTR<1:0> = 10): ALARM MONTH AND DAY VALUE REGISTER $^{(1)}$

| U-0    | U-0 | U-0 | R/W-x R/W-x F |                 | R/W-x R/W-x |         | R/W-x   |

|--------|-----|-----|---------------|-----------------|-------------|---------|---------|

| _      | _   | _   | MTHTEN0       | MTHONE3 MTHONE2 |             | MTHONE1 | MTHONE0 |

| bit 15 |     |     |               |                 |             |         | bit 8   |

| U-0   | U-0 R/W-x R/W-x           |  | R/W-x   | R/W-x R/W-x |         | R/W-x | R/W-x |

|-------|---------------------------|--|---------|-------------|---------|-------|-------|

| _     | - DAYTEN1 DAYTEN0 DAYONE3 |  | DAYONE2 | DAYONE1     | DAYONE0 |       |       |

| bit 7 |                           |  |         |             |         |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit      |

|           | Contains a value of 0 or 1.                                        |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits |

|           | Contains a value from 0 to 9.                                      |

| bit 7-6   | Unimplemented: Read as '0'                                         |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits   |

|           | Contains a value from 0 to 3.                                      |

| bit 3-0   | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits   |

|           | Contains a value from 0 to 9.                                      |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 28-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER<sup>(3)</sup> (CONTINUED)

- **CS1P:** Chip Select 0 Polarity bit<sup>(1)</sup> bit 3

- 1 = Active-high (PMCS1/PMCS)(2)

- 0 = Active-low (PMCS1/PMCS)

- bit 2 BEP: Byte Enable Polarity bit

- 1 = Byte enable is active-high (PMBE)

- 0 = Byte enable is active-low (PMBE)

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):

- 1 = Write strobe is active-high (PMWR)

- 0 = Write strobe is active-low (PMWR)

- For Master Mode 1 (PMMODE<9:8> = 11):

- 1 = Enables strobe active-high (PMENB)

- 0 = Enables strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):

- 1 = Read strobe is active-high (PMRD)

- 0 = Read strobe is active-low (PMRD)

- For Master Mode 1 (PMMODE<9:8> = 11):

- 1 = Enables strobe active-high (PMRD/PMWR)

- 0 = Enables strobe active-low (PMRD/PMWR)

- Note 1: These bits have no effect when their corresponding pins are used as address lines.

- 2: PMCS1 applies to Master mode and PMCS applies to Slave mode.

- 3: This register is not available on 44-pin devices.

#### 30.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGM3XX/6XX/7XX devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- · Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming™ (ICSP™)

- · In-Circuit Emulation

#### 30.1 Configuration Bits

In dsPIC33EPXXXGM3XX/6XX/7XX devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 30-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

**Note:** Configuration data is reloaded on all types of device Resets.

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

Note: Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 30-1.

TABLE 33-9: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTERISTICS                     |    |    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |       |            |      |         |

|----------------------------------------|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|---------|

| Parameter No. Typ. <sup>(2)</sup> Max. |    |    | Doze<br>Ratio                                                                                                                                                                                                                                    | Units | Conditions |      |         |

| Doze Current (IDOZE) <sup>(1)</sup>    |    |    |                                                                                                                                                                                                                                                  |       |            |      |         |

| DC73a                                  | 20 | 53 | 1:2                                                                                                                                                                                                                                              | mA    | -40°C      | 3.3V | 70 MIPS |

| DC73g                                  | 8  | 30 | 1:128                                                                                                                                                                                                                                            | mA    | -40 C      |      |         |

| DC70a                                  | 19 | 53 | 1:2                                                                                                                                                                                                                                              | mA    | +25°C      | 3.3V | 60 MIPS |

| DC70g                                  | 8  | 30 | 1:128                                                                                                                                                                                                                                            | mA    | +25 C      |      |         |

| DC71a                                  | 20 | 53 | 1:2                                                                                                                                                                                                                                              | mA    | +85°C      | 3.3V | 60 MIPS |

| DC71g                                  | 10 | 30 | 1:128                                                                                                                                                                                                                                            | mA    | +65 C      |      |         |

| DC72a                                  | 25 | 42 | 1:2                                                                                                                                                                                                                                              | mA    | 110E°C     | 3.3V | FO MIDS |

| DC72g                                  | 12 | 30 | 1:128                                                                                                                                                                                                                                            | mA    | +125°C     |      | 50 MIPS |

- **Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- CPU executing

while(1)

{

NOP();

}

- JTAG is disabled

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise specified.