Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      |                                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) |                                                                                  |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm310-h-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| IADL        | ABLE 4-2: INTERROPT CONTROLLER REGISTER MAP FOR dSPIC33EPAAAGM6AA/7AA DEVICES (CONTINUED) |        |         |         |         |        |            |            |            |         |                       |                       |                       |         |         |         |         |               |

|-------------|-------------------------------------------------------------------------------------------|--------|---------|---------|---------|--------|------------|------------|------------|---------|-----------------------|-----------------------|-----------------------|---------|---------|---------|---------|---------------|

| SFR<br>Name | Addr.                                                                                     | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10     | Bit 9      | Bit 8      | Bit 7   | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| IPC11       | 0856                                                                                      | —      | T6IP2   | T6IP1   | T6IP0   | —      | —          | —          | —          | _       | PMPIP2 <sup>(1)</sup> | PMPIP1 <sup>(1)</sup> | PMPIP0 <sup>(1)</sup> | _       | OC8IP2  | OC8IP1  | OC8IP0  | 4444          |

| IPC12       | 0858                                                                                      | _      | T8IP2   | T8IP1   | T8IP0   | _      | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | _       | SI2C2IP2              | SI2C2IP1              | SI2C2IP0              | _       | T7IP2   | T7IP1   | T7IP0   | 4444          |

| IPC13       | 085A                                                                                      | _      | C2RXIP2 | C2RXIP1 | C2RXIP0 | -      | INT4IP2    | INT4IP1    | INT4IP0    | _       | INT3IP2               | INT3IP1               | INT3IP0               | _       | T9IP2   | T9IP1   | T9IP0   | 4444          |

| IPC14       | 085C                                                                                      | -      | DCIEIP2 | DCIEIP1 | DCIEIP0 | _      | QEI1IP2    | QEI1IP2    | QEI1IP0    | _       | PCEPIP2               | PCEPIP1               | PCEPIP0               | _       | C2IP2   | C2IP1   | C2IP0   | 4444          |

| IPC15       | 085E                                                                                      | -      | FLT1IP2 | FLT1IP1 | FLT1IP0 | _      | RTCCIP2(2) | RTCCIP1(2) | RTCCIP0(2) | _       | _                     | _                     | _                     | _       | DCIIP2  | DCIIP1  | DCIIP0  | 0404          |

| IPC16       | 0860                                                                                      | -      | CRCIP2  | CRCIP1  | CRCIP0  | _      | U2EIP2     | U2EIP1     | U2EIP0     | _       | U1EIP2                | U1EIP1                | U1EIP0                | _       | FLT2IP2 | FLT2IP1 | FLT2IP0 | 4440          |

| IPC17       | 0862                                                                                      | -      | C2TXIP2 | C2TXIP1 | C2TXIP0 | _      | C1TXIP2    | C1TXIP1    | C1TXIP0    | _       | _                     | _                     | _                     | _       | _       | _       | _       | 4400          |

| IPC18       | 0864                                                                                      | -      | QEI2IP2 | QEI2IP1 | QEI2IP0 | _      | FLT3IP2    | FLT3IP1    | FLT3IP0    | _       | PCESIP2               | PCESIP1               | PCESIP0               | _       | _       | _       | _       | 4040          |

| IPC19       | 0866                                                                                      | -      | _       | _       | _       | _      | _          | _          | _          | _       | CTMUIP2               | CTMUIP1               | CTMUIP0               | _       | FLT4IP2 | FLT4IP1 | FLT4IP0 | 4000          |

| IPC20       | 0868                                                                                      | -      | U3TXIP2 | U3TXIP1 | U3TXIP0 | _      | U3RXIP2    | U3RXIP1    | U3RXIP0    | _       | U3EIP2                | U3EIP1                | U3EIP0                | _       | _       | _       | _       | 0000          |

| IPC21       | 086A                                                                                      | -      | U4EIP2  | U4EIP1  | U4EIP0  | _      | _          | _          | _          | _       | _                     | _                     | _                     | _       | _       | _       | _       | 0000          |

| IPC22       | 086C                                                                                      | -      | SPI3IP2 | SPI3IP1 | SPI3IP0 | _      | SPI3EIP2   | SPI3EIP1   | SPI3EIP0   | _       | U4TXIP2               | U4TXIP1               | U4TXIP0               | _       | U4RXIP2 | U4RXIP1 | U4RXIP0 | 0000          |

| IPC23       | 086E                                                                                      | -      | PGC2IP2 | PGC2IP1 | PGC2IP0 | _      | PWM1IP2    | PWM1IP1    | PWM1IP0    | _       | _                     | _                     | _                     | _       | _       | _       | _       | 4400          |

| IPC24       | 0870                                                                                      | -      | PWM6IP2 | PWM6IP1 | PWM6IP0 | _      | PWM5IP2    | PWM5IP1    | PWM5IP0    | _       | PWM4IP2               | PWM4IP1               | PWM4IP0               | _       | PWM3IP2 | PWM3IP1 | PWM3IP0 | 4444          |

| IPC35       | 0886                                                                                      | -      | JTAGIP2 | JTAGIP1 | JTAGIP0 | _      | ICDIP2     | ICDIP1     | ICDIP0     | _       | _                     | _                     | _                     | _       | _       | _       | _       | 4400          |

| IPC36       | 0888                                                                                      | _      | PTG0IP2 | PTG0IP1 | PTG0IP0 | -      | PTGWDTIP2  | PTGWDTIP1  | PTGWDTIP0  | _       | PTGSTEPIP2            | PTGSTEPIP1            | PTGSTEPIP0            | _       | —       | —       | _       | 4440          |

| IPC37       | 088A                                                                                      | _      | —       | —       | —       | -      | PTG3IP2    | PTG3IP1    | PTG3IP0    | _       | PTG2IP2               | PTG2IP1               | PTG2IP0               | _       | PTG1IP2 | PTG1IP1 | PTG1IP0 | 0445          |

| INTTREG     | 08C8                                                                                      | _      | _       | _       | -       | ILR3   | ILR2       | ILR1       | ILR0       | VECNUM7 | VECNUM6               | VECNUM5               | VECNUM4               | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 | 0000          |

## TABLE 4-2: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGM6XX/7XX DEVICES (CONTINUED)

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** The PMPIF/PMPIE/PMPIPx flags are not available on 44-pin devices.

2: The RTCCIF/RTCCIE/RTCCIPx flags are not available on 44-pin devices.

## dsPIC33EPXXXGM3XX/6XX/7XX

FIGURE 7-1: dsPIC33EPXXXGM3XX/6XX/7XX INTERRUPT VECTOR TABLE

| <b>▲</b>                          | Reset – GOTO Instruction         | 0x000000 |                          |

|-----------------------------------|----------------------------------|----------|--------------------------|

|                                   | Reset – GOTO Address             | 0x000002 |                          |

| £                                 | Oscillator Fail Trap Vector      | 0x000004 |                          |

| rior                              | Address Error Trap Vector        | 0x000006 |                          |

| ር<br>አ                            | Generic Hard Trap Vector         | 0x000008 |                          |

| Orde                              | Stack Error Trap Vector          | 0x00000A |                          |

| ផ្ទ                               | Math Error Trap Vector           | 0x00000C |                          |

| atur                              | DMA Controller Error Trap Vector | 0x00000E |                          |

| ž b                               | Generic Soft Trap Vector         | 0x000010 |                          |

| Decreasing Natural Order Priority | Reserved                         | 0x000012 |                          |

| crea                              | Interrupt Vector 0               | 0x000014 |                          |

| Dec                               | Interrupt Vector 1               | 0x000016 |                          |

|                                   | :                                | :        |                          |

| ,                                 | :                                | :        |                          |

| ĭ                                 | :                                | :        |                          |

| 2                                 | Interrupt Vector 52              | 0x00007C |                          |

|                                   | Interrupt Vector 53              | 0x00007E |                          |

|                                   | Interrupt Vector 54              | 0x000080 | $\backslash$             |

|                                   | :                                | :        | See Table 7-1 for        |

|                                   | :                                | :        | Interrupt Vector Details |

|                                   | :                                | :        |                          |

|                                   | Interrupt Vector 116             | 0x0000FC |                          |

|                                   | Interrupt Vector 117             | 0x0000FE |                          |

|                                   | Interrupt Vector 118             | 0x000100 |                          |

|                                   | Interrupt Vector 119             | 0x000102 |                          |

|                                   | Interrupt Vector 120             | 0x000104 |                          |

|                                   | :                                | :        |                          |

|                                   | :                                | :        |                          |

|                                   | :                                | :        |                          |

| V                                 | Interrupt Vector 244             | 0x0001FC |                          |

|                                   | Interrupt Vector 245             | 0x0001FE | /                        |

|                                   | START OF CODE                    | 0x000200 |                          |

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Secondary (Timer1) Oscillator (SOSC)                       | Secondary         | xx          | 100        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 00          | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

## TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

## 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby mode when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions

- · The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

## REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 3 | <b>U3MD:</b> UART3 Module Disable bit<br>1 = UART3 module is disabled<br>0 = UART3 module is enabled |

|-------|------------------------------------------------------------------------------------------------------|

| bit 2 | I2C3MD: I2C3 Module Disable bit                                                                      |

|       | 1 = I2C3 module is disabled<br>0 = I2C3 module is enabled                                            |

| bit 1 | I2C2MD: I2C2 Module Disable bit                                                                      |

|       | 1 = I2C2 module is disabled<br>0 = I2C2 module is enabled                                            |

| bit 0 | ADC2MD: ADC2 Module Disable bit                                                                      |

|       | 1 = ADC2 module is disabled<br>0 = ADC2 module is enabled                                            |

**Note 1:** The RTCCMD bit is not available on 44-pin devices.

| TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (F | ₹Pn) |

|-----------------------------------------------------|------|

|-----------------------------------------------------|------|

| Function     | RPnR<5:0> | Output Name                                     |

|--------------|-----------|-------------------------------------------------|

| Default Port | 000000    | RPn tied to Default Pin                         |

| U1TX         | 000001    | RPn tied to UART1 Transmit                      |

| U2TX         | 000011    | RPn tied to UART2 Transmit                      |

| SDO2         | 001000    | RPn tied to SPI2 Data Output                    |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output                   |

| SS2          | 001010    | RPn tied to SPI2 Slave Select                   |

| CSDO         | 001011    | RPn tied to DCI Data Output                     |

| CSCK         | 001100    | RPn tied to DCI Clock Output                    |

| COFS         | 001101    | RPn tied to DCI Frame Sync                      |

| C1TX         | 001110    | RPn tied to CAN1 Transmit                       |

| C2TX         | 001111    | RPn tied to CAN2 Transmit                       |

| OC1          | 010000    | RPn tied to Output Compare 1 Output             |

| OC2          | 010001    | RPn tied to Output Compare 2 Output             |

| OC3          | 010010    | RPn tied to Output Compare 3 Output             |

| OC4          | 010011    | RPn tied to Output Compare 4 Output             |

| OC5          | 010100    | RPn tied to Output Compare 5 Output             |

| OC6          | 010101    | RPn tied to Output Compare 6 Output             |

| OC7          | 010110    | RPn tied to Output Compare 7 Output             |

| OC8          | 010111    | RPn tied to Output Compare 8 Output             |

| C1OUT        | 011000    | RPn tied to Comparator Output 1                 |

| C2OUT        | 011001    | RPn tied to Comparator Output 2                 |

| C3OUT        | 011010    | RPn tied to Comparator Output 3                 |

| U3TX         | 011011    | RPn tied to UART3 Transmit                      |

| <b>U3RTS</b> | 011100    | RPn tied to UART3 Ready-to-Send                 |

| U4TX         | 011101    | RPn tied to UART4 Transmit                      |

| U4RTS        | 011110    | RPn tied to UART4 Ready-to-Send                 |

| SDO3         | 011111    | RPn tied to SPI3 Slave Output                   |

| SCK3         | 100000    | RPn tied to SPI3 Clock Output                   |

| SS3          | 100001    | RPn tied to SPI3 Slave Select                   |

| SYNCO1       | 101101    | RPn tied to PWM Primary Time Base Sync Output   |

| SYNCO2       | 101110    | RPn tied to PWM Secondary Time Base Sync Output |

| QEI1CCMP     | 101111    | RPn tied to QEI1 Counter Comparator Output      |

| QEI2CCMP     | 110000    | RPn tied to QEI2 Counter Comparator Output      |

| REFCLKO      | 110001    | RPn tied to Reference Clock Output              |

| C4OUT        | 110010    | RPn tied to Comparator Output 4                 |

| C5OUT        | 110011    | RPn tied to Comparator Output 5                 |

### REGISTER 16-5: STCON: PWMx SECONDARY TIME BASE CONTROL REGISTER

| U-0    | U-0 | U-0 | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|-----|---------|-------|---------------------|------------------------|------------------------|

|        | —   | —   | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |     |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|--|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |  |

| bit 7 bit             |                         |                         |                         |                        |                        |                        |                        |  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit |                    |  |  |

|-------------------|-----------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, rea | ad as '0'          |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                                                                                                          |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | SESTAT: Special Event Interrupt Status bit                                                                                                                                                                          |

|           | <ul><li>1 = Special event interrupt is pending</li><li>0 = Special event interrupt is not pending</li></ul>                                                                                                         |

| bit 11    | SEIEN: Special Event Interrupt Enable bit                                                                                                                                                                           |

|           | <ul><li>1 = Special event interrupt is enabled</li><li>0 = Special event interrupt is disabled</li></ul>                                                                                                            |

| bit 10    | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                                                                            |

|           | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWM cycle boundaries</li> </ul>                                                                     |

| bit 9     | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                                                                                   |

|           | <ul><li>1 = SYNCI2/SYNCO2 polarity is inverted (active-low)</li><li>0 = SYNCI2/SYNCO2 is active-high</li></ul>                                                                                                      |

| bit 8     | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                                                                                           |

|           | <ul><li>1 = SYNCO2 output is enabled</li><li>0 = SYNCO2 output is disabled</li></ul>                                                                                                                                |

| bit 7     | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                                                                                |

|           | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul>                                                             |

| bit 6-4   | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup>                                                                                                                                                      |

|           | 111 = Reserved                                                                                                                                                                                                      |

|           | •                                                                                                                                                                                                                   |

|           | •                                                                                                                                                                                                                   |

|           | 100 = Reserved                                                                                                                                                                                                      |

|           | $011 = PTGO17^{(2)}$                                                                                                                                                                                                |

|           | $010 = PTGO16^{(2)}$ $001 = Reserved$                                                                                                                                                                               |

|           | 000 = SYNCI1                                                                                                                                                                                                        |

| Note 1:   | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of |

- application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

## REGISTER 16-6: STCON2: PWMx SECONDARY MASTER CLOCK DIVIDER SELECT REGISTER 2

| U-0                                                         | U-0 | U-0 | U-0 | U-0              | U-0                         | U-0   | U-0   |  |

|-------------------------------------------------------------|-----|-----|-----|------------------|-----------------------------|-------|-------|--|

| —                                                           | —   | —   | —   | —                | —                           | —     | _     |  |

| bit 15                                                      |     |     |     |                  |                             |       | bit 8 |  |

|                                                             |     |     |     |                  |                             |       |       |  |

| U-0                                                         | U-0 | U-0 | U-0 | U-0              | R/W-0                       | R/W-0 | R/W-0 |  |

| —                                                           | —   | —   | —   | —                | PCLKDIV<2:0> <sup>(1)</sup> |       |       |  |

| bit 7                                                       |     |     |     |                  |                             |       | bit 0 |  |

|                                                             |     |     |     |                  |                             |       |       |  |

| Legend:                                                     |     |     |     |                  |                             |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, re |     |     |     | mented bit, read | as '0'                      |       |       |  |

| R – Reauable bit  |                  | 0 – Unimplemented bit, read |                    |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64

- 101 = Divide-by-32

- 100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0               | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                    | U-0                                                                           | U-0                     | U-0                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------|------------------------|

| TRGDIV3             | TRGDIV2                                                                                                                                                                                                                                                      | TRGDIV1                                                                                                                                                                                                                                                                                                                                                                                                                         | TRGDIV0                                                                                                                                                                                                                                                                                    |                                                                                                                                        | _                                                                             |                         | _                      |

| bit 15              |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                               |                         | bit                    |

| U-0                 | U-0                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                  | R/W-0                                                                         | R/W-0                   | R/W-0                  |

| _                   | _                                                                                                                                                                                                                                                            | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                         | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                    | TRGSTRT5 <sup>(1)</sup>                                                                                                                | TRGSTRT5 <sup>(1)</sup>                                                       | TRGSTRT5 <sup>(1)</sup> | TRGSTRT5 <sup>(1</sup> |

| bit 7               |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                               |                         | bit                    |

| Legend:             |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                               |                         |                        |

| R = Readabl         | e bit                                                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                  | oit                                                                                                                                                                                                                                                                                        | U = Unimplem                                                                                                                           | nented bit, read                                                              | as '0'                  |                        |

| -n = Value at       | POR                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                            | '0' = Bit is clea                                                                                                                      | ared                                                                          | x = Bit is unkno        | own                    |

|                     |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                               |                         |                        |

| bit 15-12           | 1111 = Trigg<br>1110 = Trigg<br>1101 = Trigg<br>1001 = Trigg<br>1010 = Trigg<br>1001 = Trigg<br>1000 = Trigg<br>0111 = Trigg<br>0110 = Trigg<br>0101 = Trigg<br>0101 = Trigg<br>0011 = Trigg<br>0010 = Trigg<br>0001 = Trigg<br>0001 = Trigg<br>0000 = Trigg | >: Trigger # Ou<br>er output for ev<br>er output for ev | ery 16th trigge<br>ery 15th trigge<br>ery 15th trigge<br>ery 13th trigge<br>ery 12th trigge<br>ery 12th trigge<br>ery 10th trigger<br>ery 9th trigger<br>ery 8th trigger<br>ery 6th trigger<br>ery 5th trigger<br>ery 5th trigger<br>ery 3rd trigger<br>ery 2nd trigger<br>ery trigger eve | r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>event<br>event<br>event<br>event<br>event<br>event<br>event<br>event |                                                                               |                         |                        |

| bit 11-6<br>bit 5-0 | TRGSTRT<5<br>111111 = Wa                                                                                                                                                                                                                                     | ait 63 PWM cyc                                                                                                                                                                                                                                                                                                                                                                                                                  | estscaler Start E<br>eles before gen<br>es before gene<br>e before genera                                                                                                                                                                                                                  | rating the first t                                                                                                                     | its <sup>(1)</sup><br>trigger event a<br>rigger event afte<br>gger event afte | er the module is        | s enabled              |

## REGISTER 16-18: TRGCONx: PWMx TRIGGER CONTROL REGISTER

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Serial Peripheral Interface (SPI)" (DS70005185), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. The dsPIC33EPXXXGM3XX/6XX/7XX device family offers three SPI modules on a single device. These modules, which are designated as SPI1, SPI2 and SPI3, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 and SPI3. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1, SPI2 and SPI3 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 and SPI3 modules take advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of these modules, but results in a lower maximum speed. See **Section 33.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

## dsPIC33EPXXXGM3XX/6XX/7XX

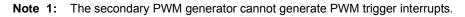

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

## dsPIC33EPXXXGM3XX/6XX/7XX

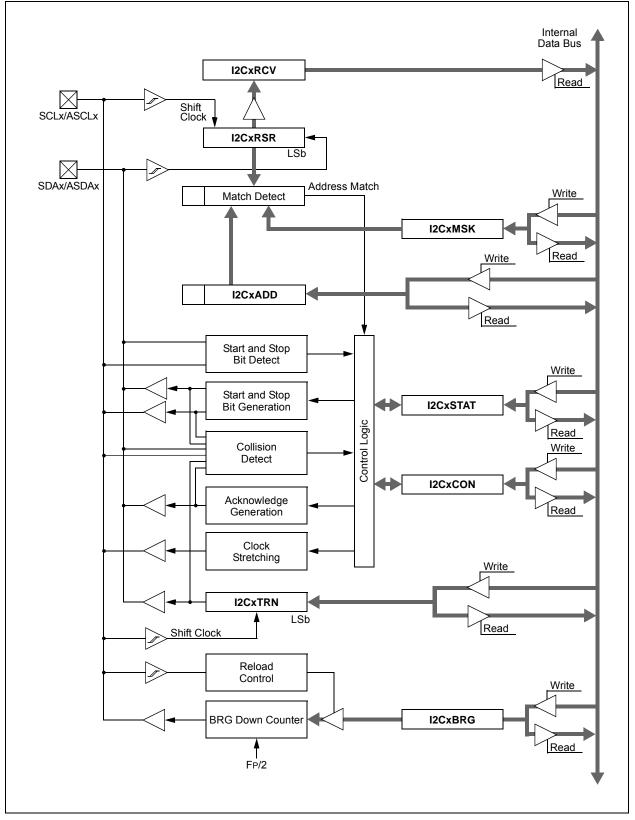

## FIGURE 22-1: CTMU BLOCK DIAGRAM

## 24.2 DCI Control Registers

## REGISTER 24-1: DCICON1: DCI CONTROL REGISTER 1

| 1<br>bit 14 Re<br>bit 13 De<br>1<br>0<br>bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                     | e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                           | e is disabled                                                                                                                     | t              | r-0<br>r<br>U = Unimplem<br>'0' = Bit is clea | r-0<br>r<br>ented bit, read a | CSCKE<br>R/W-0<br>COFSM1<br>as '0'<br>x = Bit is unkno | COFSD<br>bit 8<br>R/W-0<br>COFSM0<br>bit 0 |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------|-------------------------------|--------------------------------------------------------|--------------------------------------------|--|--|--|

| R/W-0         UNFM         bit 7         Legend:         R = Readable         -n = Value at         bit 15       D0         bit 14       Re         bit 13       D0         bit 13       D0         bit 13       D0         bit 13       D0         bit 14       Re         bit 13       D0         bit 14       Re         bit 13       D0         bit 14       D1 | CSDOM<br>e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                  | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>lodule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | R/W-0<br>COFSM0<br>bit (                   |  |  |  |

| UNFM<br>bit 7<br>Legend:<br>R = Readable<br>-n = Value at<br>bit 15 D0<br>1<br>0<br>bit 14 Re<br>bit 13 D0<br>1<br>0<br>bit 12 Re<br>bit 12 Re                                                                                                                                                                                                                      | CSDOM<br>e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                  | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>lodule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | COFSM0<br>bit (                            |  |  |  |

| UNFM<br>bit 7<br>Legend:<br>R = Readable<br>-n = Value at<br>bit 15 D0<br>1<br>0<br>bit 14 Re<br>bit 13 D0<br>1<br>0<br>bit 12 Re<br>bit 12 Re                                                                                                                                                                                                                      | CSDOM<br>e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                  | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>lodule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | COFSM0<br>bit (                            |  |  |  |

| bit 7<br>Legend:<br>R = Readable<br>-n = Value at<br>bit 15 De<br>1<br>0<br>bit 14 Re<br>bit 13 De<br>1<br>0<br>bit 12 Re<br>bit 12 Re                                                                                                                                                                                                                              | e bit<br>POR<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                          | r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0'          | t<br>t         | U = Unimplem                                  | ented bit, read a             | as '0'                                                 | bit (                                      |  |  |  |

| R = Readable<br>-n = Value at<br>bit 15 De<br>bit 14 Re<br>bit 13 De<br>bit 13 De<br>bit 12 Re<br>bit 11 De                                                                                                                                                                                                                                                         | e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                           | W = Writable bi<br>'1' = Bit is set<br>lodule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0'                            | t              | -                                             |                               |                                                        | own                                        |  |  |  |

| R = Readable<br>-n = Value at<br>bit 15 D<br>bit 14 Re<br>bit 13 D<br>bit 13 D<br>bit 12 Re<br>bit 11 D                                                                                                                                                                                                                                                             | POR<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                                   | '1' = Bit is set<br>lodule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0'                                               |                | -                                             |                               |                                                        | own                                        |  |  |  |

| bit 15 D(<br>1<br>0<br>bit 14 R(<br>bit 13 D(<br>1<br>0<br>bit 12 R(<br>bit 11 D)                                                                                                                                                                                                                                                                                   | CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                           | odule Enable bi<br>e is enabled<br>e is disabled<br>ad as '0'                                                                     | t              | -                                             |                               |                                                        | own                                        |  |  |  |

| 1<br>0<br>bit 14<br>8<br>bit 13<br>1<br>0<br>bit 12<br>8<br>bit 12<br>1<br>0<br>bit 12<br>1<br>0                                                                                                                                                                                                                                                                    | = DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                                          | e is enabled<br>e is disabled<br>ad as '0'                                                                                        | t              |                                               |                               |                                                        |                                            |  |  |  |

| 1<br>0<br>bit 14<br>Re<br>bit 13<br>1<br>0<br>bit 12<br>Re<br>bit 11<br>D                                                                                                                                                                                                                                                                                           | = DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                                          | e is enabled<br>e is disabled<br>ad as '0'                                                                                        | t              |                                               |                               |                                                        |                                            |  |  |  |

| 0<br>bit 14 Re<br>bit 13 De<br>1<br>0<br>bit 12 Re<br>bit 11 De                                                                                                                                                                                                                                                                                                     | = DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                                                          | e is disabled<br>ad as '0'                                                                                                        |                |                                               |                               |                                                        |                                            |  |  |  |

| bit 14 Re<br>bit 13 D<br>1<br>0<br>bit 12 Re<br>bit 11 D                                                                                                                                                                                                                                                                                                            | eserved: Rea<br>CISIDL: DCI<br>= Module will                                                                                          | ad as '0'                                                                                                                         |                |                                               |                               |                                                        |                                            |  |  |  |

| bit 13 D(<br>1<br>0<br>bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                                       | <b>CISIDL:</b> DCI<br>= Module will                                                                                                   |                                                                                                                                   |                |                                               |                               |                                                        |                                            |  |  |  |

| 1<br>0<br>bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                                                    | = Module will                                                                                                                         | Stop in Idle Con                                                                                                                  |                |                                               |                               |                                                        |                                            |  |  |  |

| 0<br>bit 12 Re<br>bit 11 Di                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                       | •                                                                                                                                 |                |                                               |                               |                                                        |                                            |  |  |  |

| bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                       | I halt in CPU Idle<br>I continue to ope                                                                                           |                | Idle mode                                     |                               |                                                        |                                            |  |  |  |

| bit 11 DI                                                                                                                                                                                                                                                                                                                                                           | eserved: Rea                                                                                                                          | -                                                                                                                                 |                |                                               |                               |                                                        |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | DLOOP: Digital Loopback Mode Control bit                                                                                              |                                                                                                                                   |                |                                               |                               |                                                        |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | 1 = Digital Loopback mode is enabled; CSDI and CSDO pins are internally connected                                                     |                                                                                                                                   |                |                                               |                               |                                                        |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                       | pback mode is c                                                                                                                   |                |                                               |                               |                                                        |                                            |  |  |  |

| bit 10 C                                                                                                                                                                                                                                                                                                                                                            | CSCKD: Sample Clock Direction Control bit                                                                                             |                                                                                                                                   |                |                                               |                               |                                                        |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                       | is an input when<br>is an output whe                                                                                              |                |                                               |                               |                                                        |                                            |  |  |  |

| bit 9 C                                                                                                                                                                                                                                                                                                                                                             | SCKE: Samp                                                                                                                            | ole Clock Edge (                                                                                                                  | Control bit    |                                               |                               |                                                        |                                            |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                   | = Data chang                                                                                                                          | ges on serial clo                                                                                                                 | ck falling edg | je, sampled on s                              | erial clock rising            | l edge                                                 |                                            |  |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                   | = Data chang                                                                                                                          | ges on serial clo                                                                                                                 | ck rising edg  | e, sampled on se                              | erial clock falling           | l edge                                                 |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                       | e Synchronizatio                                                                                                                  |                |                                               |                               |                                                        |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>1 = COFS pin is an input when DCI module is enabled</li> <li>0 = COFS pin is an output when DCI module is enabled</li> </ul> |                                                                                                                                   |                |                                               |                               |                                                        |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                     | is an output whe<br>low Mode bit                                                                                                  | en DCI modu    | le is enabled                                 |                               |                                                        |                                            |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                   | = Transmits I                                                                                                                         |                                                                                                                                   |                | smit registers on                             | a transmit unde               | rflow                                                  |                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                       | al Data Output M                                                                                                                  |                |                                               |                               |                                                        |                                            |  |  |  |