Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | -                                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | -                                                                                |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

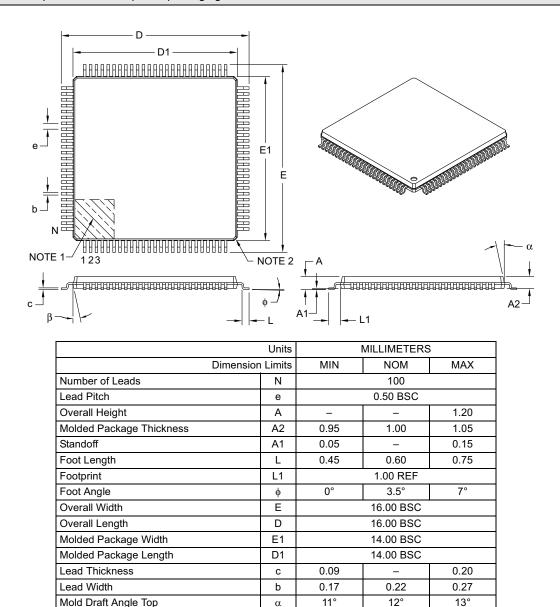

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm310-h-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name<br>Name<br>NameAddr.Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 20Bit 10Bit 20Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                   |       |       |       |        |            |              |             |            |            |        |        | MAP    | ISTER N | SREG   | TIMER  | 4-4:  | TABLE 4 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|-------|-------|-------|--------|------------|--------------|-------------|------------|------------|--------|--------|--------|---------|--------|--------|-------|---------|

| PR1       0102       Period Register 1         TICON       0104       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM2       0106       -       Time?       Period Register       FORATE       TCKPS1       TCKPS1       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM3       0106       -       Time?       Register for 32-bit timer operations only)       -       TTSYNC       TCS       —         TRR3H_D       0106       -       -       Time?       Period Register 3       -       TCS       -       -       -       TGATE       TCKPS0       T32       -       TCS       -       -       -       TGATE       TCKPS0       TSD       -       TCS       -       -       -       TGATE       TCKPS0       TSD       -       TCS       -       -       TTSD       -       TCS       -       -       TGATE       TCKPS0       TSD       -       TCS       -       TTSD       -       TTSD       TCS       -       TTSD       TTSD       TTSD       TTSD       TTSD                                                                                                                                                                                        | All<br>Resets | Bit 0             | Bit 1 | Bit 2 | Bit 3 | Bit 4  | Bit 5      | Bit 6        | Bit 7       | Bit 8      | Bit 9      | Bit 10 | Bit 11 | Bit 12 | Bit 13  | Bit 14 | Bit 15 | Addr. | -       |

| TICON       014//       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR2       0106       -       Timer2       Register       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR3       0106       -       Timer3       Register       -       TS2-bit filter operations only)       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       TCKPS0       T32       -       TCS       -       -       -       -       TCS       -       -       TCS       -       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       10116       1014       1014 </td <td>0000</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>r</td> <td>er1 Registe</td> <td>Tim</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0100</td> <td>TMR1</td> | 0000          |                   |       |       |       |        |            | r            | er1 Registe | Tim        |            |        |        |        |         |        |        | 0100  | TMR1    |

| TMR2       0.106       Timer2 Register         TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       0100       Period Register 2         PR2       0100       Period Register 2         PR3       0110       TON       -       TSIDL       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4HD       0110       TON       -       TSIDL       -       -       -       -       TGCR       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5HD       0116       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5HD                                                                                                                                                                                                                                  | FFFF          | -                 |       |       |       |        |            | 1            | od Register | Peri       |            |        |        |        |         |        |        | 0102  | PR1     |

| TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       010A       Timer3 Register         PR2       010C       Period Register 2         PR3       0100       Period Register 2         PR3       0100       Timer3 Register 2         PR3       0100       Timer3 Register 2         PR3       0110       TON -       TISDL       -       Period Register 1         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       Timer5 Holding Register (For 32-bit timer operations only)         TMR5       0118       Timer5 Holding Register (For 32-bit timer operations only)         TMR5       0116       Timer5 Register 4         PR4       0110       Timer6 Register 4         PR5       011C       Period Register 7         T4CON       0112       Timer7 Holding Register (For 32-bit timer operations only)         TMR6       0122       Timer7 Holding Register (For 32-bit                                                                                                                                                                                                              | 0000          | _                 | TCS   | TSYNC | —     | TCKPS0 | TCKPS1     | TGATE        |             | _          | _          | _      | —      | _      | TSIDL   | _      | TON    | 0104  | T1CON   |

| TMR3       010A       Timer3 Register 7         PR2       010C       Period Register 3         TZCON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0114       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0118       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       <                                                                                                                                                                                                                                                    | 0000          | -                 |       |       |       |        |            | r            | er2 Registe | Tim        |            |        |        |        |         |        |        | 0106  | TMR2    |

| PR2       010C       Period Register 2         PR3       010E       Period Register 3         T2CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR5HLD       0118       -       -       -       -       -       Period Register 4       Period Register 4         PR5       0110       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       -       TSIDL       -       -       -       -       TGA                                                                                                                                                                                                                                                        | xxxx          |                   |       |       |       |        | ions only) | timer operat | (For 32-bit | g Register | er3 Holdin | Time   |        |        |         |        |        | 0108  | TMR3HLD |

| PR3         010E         Period Register 3           T2CON         0110         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR5         0116         -         -         Timer5 Holding Register (For 32-bit timer operations only)         -         TCS         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           PR4         0114         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T4CON         0112         TON                                                                                                                                   | 0000          |                   |       |       |       |        |            | r            | er3 Registe | Tim        |            |        |        |        |         |        |        | 010A  | TMR3    |

| T2CON         0110         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS1         TCKPS0         -         -         TCS         -           TMR4         0114         -         -         -         -         TGS0         -         -         TCS         10116         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -         -         TCS         -                                                                                                                                       | FFFF          |                   |       |       |       |        |            | 2            | od Register | Peri       |            |        |        |        |         |        |        | 010C  | PR2     |

| T3CON     0112     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS0     —     —     —     TCS     —       TMR4     0114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FFFF          |                   |       |       |       |        |            | 3            | od Register | Peri       |            |        |        |        |         |        |        | 010E  | PR3     |

| TMR4     0114     Immediate     Timer4 Register       TMR4LD     0116     Timer5 Holding Register (For 32-bit timer operations only)       TMR5     0118       PR4     011A       PR5     011C       TMR6     012       TMR6     012       TMR7     012       TMR7     012       PR6     012       TMR7     0126       TMR7     0126       PR7     0128       PR7     0120       TON     -       TSIDL     -       -     -       -     Timer6 Register       TMR7     0126       -     -       -     -       -     -       O112     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -       -     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000          | —                 | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | —      | —      |        | TSIDL   |        | TON    | 0110  | T2CON   |

| TMRSHLD       0116       TimerS Holding Register (For 32-bit timer operations only)         TMRS       0118       TimerS Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T5CON       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0122       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR7       0126       Timer7 Holding Register (For 32-bit timer operations only)       TImer7 Register       Period Register 6         PR6       0132       TON       -       TSIDL       -       -       -       TGATE       TCKPS0                                                                                                                                                                                                     | 0000          | —                 | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | —      | —      |        | TSIDL   |        | TON    | 0112  | T3CON   |

| TMR5       0118       Timer5 Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T4CON       011E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       —       —       —       —       —       —       —       —       TCS       —       —       —       —       —       —       TCS       P       P       P       P       P       P       P       P       P       P <t< td=""><td>0000</td><td></td><td></td><td></td><td></td><td></td><td></td><td>r</td><td>er4 Registe</td><td>Tim</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0114</td><td>TMR4</td></t<>                                            | 0000          |                   |       |       |       |        |            | r            | er4 Registe | Tim        |            |        |        |        |         |        |        | 0114  | TMR4    |

| PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR7       0126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xxxx          |                   |       |       |       |        | ions only) | timer operat | (For 32-bit | g Register | er5 Holdin | Time   |        |        |         |        |        | 0116  | TMR5HLD |

| PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000          |                   |       |       |       |        |            | r            | er5 Registe | Tim        |            |        |        |        |         |        |        | 0118  | TMR5    |

| T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFFF          |                   |       |       |       |        |            |              |             |            | 011A       | PR4    |        |        |         |        |        |       |         |

| T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FFFF          | Period Register 5 |       |       |       |        |            |              |             |            | 011C       | PR5    |        |        |         |        |        |       |         |

| TMR6       0122       Timer6 Register         TMR7HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                | 0000          | —                 | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —           |            |            | —      | —      |        | TSIDL   | -      | TON    | 011E  | T4CON   |

| TMR7 HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       0122       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0000          | —                 | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | —           |            |            | —      | —      |        | TSIDL   |        | TON    | 0120  | T5CON   |

| TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>0000</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>r</td> <td>er6 Registe</td> <td>Tim</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0122</td> <td>TMR6</td>                                       | 0000          |                   |       |       |       |        |            | r            | er6 Registe | Tim        |            |        |        |        |         |        |        | 0122  | TMR6    |

| PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       —       TSIDL       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR8       0130       —       TSIDL       —       —       —       —       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xxxx          |                   |       |       |       |        | ions only) | timer operat | For 32-bit  | g Register | er7 Holdin | Time   |        |        |         |        |        | 0124  | TMR7HLD |

| PR7         012A         Period Register 7           T6CON         012C         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR8         0130         -         TSIDL         -         -         -         TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0000          |                   |       |       |       |        |            | r            | er7 Registe | Tim        |            |        |        |        |         |        |        | 0126  | TMR7    |

| T6CON     012C     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FFFF          |                   |       |       |       |        |            | 6            | od Register | Peri       |            |        |        |        |         |        |        | 0128  | PR6     |

| T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFFF          |                   |       |       |       |        |            | 7            | od Register | Peri       |            |        |        |        |         |        |        | 012A  | PR7     |

| TMR8 0130 Timer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0000          | —                 | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —           | —          | _          | —      | —      | —      | TSIDL   | _      | TON    | 012C  | T6CON   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000          | —                 | TCS   | —     | _     | TCKPS0 | TCKPS1     | TGATE        | _           | —          | _          | —      | —      | —      | TSIDL   | _      | TON    | 012E  | T7CON   |

| TMR9HLD 0132 Timer9 Holding Register (For 32-bit timer operations only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0000          |                   |       |       |       |        |            | r            | er8 Registe | Tim        |            |        |        |        |         |        |        | 0130  | TMR8    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xxxx          |                   |       |       |       |        | ions only) | timer operat | For 32-bit  | g Register | er9 Holdin | Time   |        |        |         |        |        | 0132  | TMR9HLD |

| TMR9     0134     Timer9 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000          |                   |       |       |       |        |            | r            | er9 Registe | Tim        |            |        |        |        |         |        |        | 0134  | TMR9    |

| PR8 0136 Period Register 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FFFF          |                   |       |       |       |        |            | 8            | od Register | Peri       |            |        |        |        |         |        |        | 0136  | PR8     |

| PR9 0138 Period Register 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FFFF          |                   |       |       |       |        |            | 9            | od Register | Peri       |            |        |        |        |         |        |        | 0138  | PR9     |

| T8CON         013A         TON         —         TSIDL         —         —         —         —         TGATE         TCKPS1         TCKPS0         T32         —         TCS         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000          | -                 | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | _      | —      | _      | TSIDL   | _      | TON    | 013A  | T8CON   |

| T9CON     013C     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0000          | -                 | TCS   | -     | _     | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | _      | —      | —      | TSIDL   | _      | TON    | 013C  | T9CON   |

dsPIC33EPXXXGM3XX/6XX/7XX

#### TABLE 4-4: TIMERS REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-10: PWM GENERATOR 2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14            | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|-------------------|---------|---------|-----------|-----------|-----------|-----------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2     | 0C40  | FLTSTAT | CLSTAT            | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON2      | 0C42  | PENH    | PENL              | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON2     | 0C44  | IFLTMOD | CLSRC4            | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC2        | 0C46  |         |                   |         |         |           |           |           | PDC2      | <15:0>   |         |          |          |          |          | •        | •        | 0000          |

| PHASE2      | 0C48  |         |                   |         |         |           |           |           | PHASE     | 2<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR2        | 0C4A  | _       | _                 |         |         |           |           |           |           | DTR2     | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR2     | 0C4C  | _       | _                 |         |         |           |           |           |           | ALTDTR   | 2<13:0> |          |          |          |          |          |          | 0000          |

| SDC2        | 0C4E  |         |                   |         |         |           |           |           | SDC2      | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE2     | 0C50  |         |                   |         |         |           |           |           | SPHAS     | =2<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG2       | 0C52  |         |                   |         |         |           |           |           | TRGCM     | IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON2     | 0C54  | TRGDIV3 | TRGDIV2           | TRGDIV1 | TRGDIV0 | _         | _         | _         | _         | _        | _       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP2     | 0C78  |         | PWMCAP2<15:0> 000 |         |         |           |           |           |           |          | 0000    |          |          |          |          |          |          |               |

| LEBCON2     | 0C5A  | PHR     | PHF               | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | —         | —         | —        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2     | 0C5C  | _       | _                 | _       | _       |           | -         |           | •         |          | LEB<1   | 1:0>     | -        |          |          | •        | •        | 0000          |

| AUXCON2     | 0C5E  | _       | _                 | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | —        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-11: PWM GENERATOR 3 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|-----------|-----------|-----------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON3     | 0C60  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     |          | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON3      | 0C62  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON3     | 0C64  | IFLTMOD | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC3        | 0C66  |         |         |         |         |           |           |           | PDC3      | <15:0>   |         |          |          |          |          |          |          | 0000          |

| PHASE3      | 0C68  |         |         |         |         |           |           |           | PHASE     | 3<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR3        | 0C6A  | _       | _       |         |         |           |           |           |           | DTR3     | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR3     | 0C6C  | _       | -       |         |         |           |           |           |           | ALTDTR   | 3<13:0> |          |          |          |          |          |          | 0000          |

| SDC3        | 0C6E  |         |         |         |         |           |           |           | SDC3      | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE3     | 0C70  |         |         |         |         |           |           |           | SPHASE    | E3<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG3       | 0C72  |         |         |         |         |           |           |           | TRGCM     | IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON3     | 0C74  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | _         | _         | _         | _         | _        | _       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP3     | 0C78  |         |         |         |         |           |           |           | PWMCA     | P3<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON3     | 0C7A  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | _         | _         | _        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY3     | 0C7C  | _       | -       | _       | _       |           |           |           |           |          | LEB<    | 11:0>    |          |          |          |          |          | 0000          |

| AUXCON3     | 0C7E  | _       | -       | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | _        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 7.3 Interrupt Control and Status Registers

dsPIC33EPXXXGM3XX/6XX/7XX devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- IFSx

- IECx

- IPCx

- INTTREG

## 7.3.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS) as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap (SGHT) status bit.

#### 7.3.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.3.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.3.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into Vector Number (VECNUM<7:0>) and Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

## 7.3.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"CPU"** (DS70359).

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

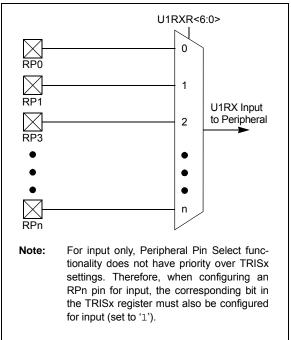

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-29). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

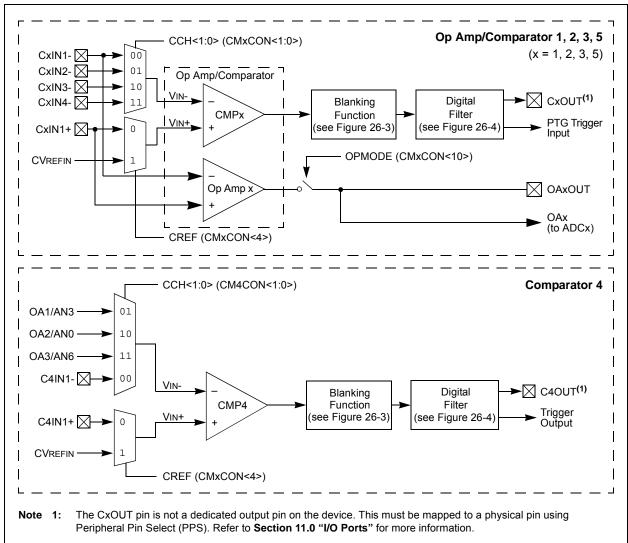

dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 26-1 in Section 26.0 "Op Amp/Comparator Module") and the PTG module (see Section 25.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual connections to the filtered QEIx module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module").

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEIx module allows peripherals to be connected to the QEIx digital filter input. To utilize this filter, the QEIx module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEIx digital filter.

#### EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43

| RPINR15 = 0x2500;<br>RPINR7 = 0x009; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */ /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| QEI1IOC = 0x4000;                    | /* Enable the QEI digital filter */                                                                                       |

| QEI1CON = 0x8000;                    | /* Enable the QEI module */                                                                                               |

| U-0                          | R/W-0                                                                                  | R/W-0                                                                                    | R/W-0                                             | R/W-0                     | R/W-0           | R/W-0                               | R/W-0 |

|------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------|-----------------|-------------------------------------|-------|

| _                            |                                                                                        |                                                                                          |                                                   | QEB2R<6:0>                | •               |                                     |       |

| bit 15                       | ·                                                                                      |                                                                                          |                                                   |                           |                 |                                     | bit 8 |

|                              |                                                                                        |                                                                                          |                                                   |                           |                 |                                     |       |

| U-0                          | R/W-0                                                                                  | R/W-0                                                                                    | R/W-0                                             | R/W-0                     | R/W-0           | R/W-0                               | R/W-0 |

| —                            |                                                                                        |                                                                                          |                                                   | QEA2R<6:0>                | •               |                                     |       |

| bit 7                        |                                                                                        |                                                                                          |                                                   |                           |                 |                                     | bit 0 |

|                              |                                                                                        |                                                                                          |                                                   |                           |                 |                                     |       |

| Legend:                      |                                                                                        |                                                                                          |                                                   |                           |                 |                                     |       |

| R = Readabl                  | le bit                                                                                 | W = Writable                                                                             | bit                                               | U = Unimplen              | nented bit, rea | ad as '0'                           |       |

| -n = Value at                | t POR                                                                                  | '1' = Bit is set                                                                         |                                                   | '0' = Bit is clea         | ared            | x = Bit is unkr                     | nown  |

| bit 14-8<br>bit 7<br>bit 6-0 | (see Table 1<br>1111111 = I<br>0000001 = I<br>0000000 = I<br>Unimplement<br>QEA2R<6:03 |                                                                                          | selection nur<br>127<br>P1<br>0'<br>I2 Phase A (C | nbers)<br>QEA2) to the Co |                 | n/RPIn Pin bits<br>RPn/RPIn Pin bit | s     |

|                              | 1111111 =  <br>•<br>•<br>•<br>•<br>•<br>•                                              | 1-2 for input pin<br>nput tied to RP <sup>-</sup><br>nput tied to CM<br>nput tied to Vss | 127<br>P1                                         | nbers)                    |                 |                                     |       |

#### REGISTER 11-12: RPINR16: PERIPHERAL PIN SELECT INPUT REGISTER 16

| R/W-0<br>R/W-0                         | R/W-0<br>R/W-0<br>W = Writable H<br>'1' = Bit is set<br>ted: Read as '0        |                                                                                                                                                                      | R/W-0<br>DTCMP5R<6:(<br>R/W-0<br>DTCMP4R<6:(<br>U = Unimplen<br>'0' = Bit is cle                        | R/W-0<br>)>                                                                                                                                                                                                   | R/W-0<br>R/W-0<br>d as '0'<br>x = Bit is unkr                                                                                                                                                                                                               | R/W-0<br>bit 8<br>R/W-0<br>bit 0                                                                                                                                                                                                                                          |

|----------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | R/W-0<br>DTCMP4R<6:(<br>U = Unimplen                                                                    | R/W-0<br>)>                                                                                                                                                                                                   | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                            | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                            | d as '0'                                                                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                     |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                            | d as '0'                                                                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                     |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | U = Unimplen                                                                                            | nented bit, rea                                                                                                                                                                                               |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |