Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XE

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm310-i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name                                    | Pin<br>Type | Buffer<br>Type         | PPS              | Description                                                                                                                                                                        |

|---------------------------------------------|-------------|------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN49                                    | Ι           | Analog                 | No               | Analog Input Channels 0-49.                                                                                                                                                        |

| CLKI                                        | I           | ST/<br>CMOS            | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                        | 0           | _                      | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                        | I           | ST/                    | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                        | I/O         | CMOS<br>—              | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| SOSCI                                       | I           | ST/<br>CMOS            | No               | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                     |

| SOSCO                                       | 0           | _                      | No               | 32.768 kHz low-power oscillator crystal output.                                                                                                                                    |

| IC1-IC8                                     | I           | ST                     | Yes              | Input Capture Inputs 1 through 8.                                                                                                                                                  |

| OCFA<br>OCFB<br>OC1-OC8                     | <br> <br>   | ST<br>ST               | Yes<br>No<br>Yes | Output Compare Fault A input (for compare channels).<br>Output Compare Fault B input (for compare channels).<br>Output Compare 1 through 8.                                        |

| INT0                                        |             | ST                     | No               | External Interrupt 0.                                                                                                                                                              |

| INT1                                        | l i         | ST                     | Yes              | External Interrupt 1.                                                                                                                                                              |

| INT2                                        | 1           | ST                     | Yes              | External Interrupt 2.                                                                                                                                                              |

| INT3                                        | I.          | ST                     | No               | External Interrupt 3.                                                                                                                                                              |

| INT4                                        | Ι           | ST                     | No               | External Interrupt 4.                                                                                                                                                              |

| RA0-RA4, RA7-RA12,<br>RA14-RA15             | I/O         | ST                     | Yes              | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                    | I/O         | ST                     | Yes              | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                              | I/O         | ST                     | Yes              | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD1-RD6, RD8,<br>RD12-RD15                  | I/O         | ST                     | Yes              | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE0-RE1, RE8-RE9,<br>RE12-RE15              | I/O         | ST                     | Yes              | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0-RF1, RF4-RF7,<br>RF9-RF10,<br>RF12-RF13 | I/O         | ST                     | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG0-RG3,<br>RG6-RG15                        | I/O         | ST                     | Yes              | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                        | Ι           | ST                     | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK                                        |             | ST                     | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T3CK                                        |             | ST                     | No               | Timer3 external clock input.                                                                                                                                                       |

| T4CK<br>T5CK                                |             | ST<br>ST               | No<br>No         | Timer4 external clock input.                                                                                                                                                       |

| T6CK                                        |             | ST                     | NO               | Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                       |

| T7CK                                        |             | ST                     | No               | Timer7 external clock input.                                                                                                                                                       |

| T8CK                                        | l i         | ST                     | No               | Timer8 external clock input.                                                                                                                                                       |

| T9CK                                        | i           | ST                     | No               | Timer9 external clock input.                                                                                                                                                       |

| Legend: CMOS = CM<br>ST = Schmit            | tt Trigg    | mpatible<br>er input v | vith CN          | or output Analog = Analog input P = Power<br>IOS levels O = Output I = Input                                                                                                       |

| PPS = Perip                                 |             |                        |                  | TTL = TTL input buffer<br>es. For more information. see the " <b>Pin Diagrams</b> " section for pin                                                                                |

Note 1: This pin is not available on all devices. For more information, see the "Pin Diagrams" section for pin availability.

2: AVDD must be connected at all times.

# dsPIC33EPXXXGM3XX/6XX/7XX

### TABLE 4-41: OP AMP/COMPARATOR REGISTER MAP

| SFR<br>Name      | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|------------------|-------|--------|--------|--------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| CMSTAT           | 0A80  | PSIDL  | _      | —      | C5EVT  | C4EVT    | C3EVT    | C2EVT    | C1EVT    | —        | _        | _        | C5OUT    | C4OUT    | C3OUT    | C2OUT    | C1OUT    | 0000          |

| CVR1CON          | 0A82  | _      | _      | _      | _      | CVRR1    | VREFSEL  | —        | _        | CVREN    | CVROE    | CVRR0    | CVRSS    | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

| CM1CON           | 0A84  | CON    | COE    | CPOL   | _      | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | —        | CREF     | _        | —        | CCH1     | CCH0     | 0000          |

| CM1MSKSRC        | 0A86  | -      | -      | _      |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM1MSKCON        | 0A88  | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM1FLTR          | 0A8A  | _      | _      | _      | _      | _        | _        | _        | —        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM2CON           | 0A8C  | CON    | COE    | CPOL   | _      | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | —        | CREF     | _        | —        | CCH1     | CCH0     | 0000          |

| CM2MSKSRC        | 0A8E  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM2MSKCON        | 0A90  | HLMS   | -      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM2FLTR          | 0A92  | -      | -      | _      |        | _        | _        | _        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM3CON           | 0A94  | CON    | COE    | CPOL   |        | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM3MSKSRC        | 0A96  | -      | -      | _      |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| <b>CM3MSKCON</b> | 0A98  | HLMS   | -      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM3FLTR          | 0A9A  | _      | _      | _      | _      | _        | _        | —        | _        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM4CON           | 0A9C  | CON    | COE    | CPOL   | _      | _        | _        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM4MSKSRC        | 0A9E  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM4MSKCON        | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM4FLTR          | 0AA2  | _      | _      | _      | _      | _        | _        | —        | _        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM5CON           | 0AA4  | CON    | COE    | CPOL   | _      | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM5MSKSRC        | 0AA6  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM5MSKCON        | 0AA8  | HLMS   |        | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM5FLTR          | 0AAA  | —      |        | _      | _      | _        |          | —        | _        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CVR2CON          | 0AB4  | —      | _      | _      | _      | CVRR1    | VREFSEL  | _        | _        | CVREN    | CVROE    | CVRR0    | CVRSS    | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGM3XX/6XX/7XX

| R/W-0        | R/W-0                                     | U-0                                         | U-0            | R/W-0                 | U-0              | R/W-0            | R/W-0        |

|--------------|-------------------------------------------|---------------------------------------------|----------------|-----------------------|------------------|------------------|--------------|

| TRAPR        | IOPUWR                                    | _                                           |                | VREGSF                | _                | CM               | VREGS        |

| bit 15       |                                           |                                             |                |                       |                  |                  | bit 8        |

|              |                                           |                                             |                |                       |                  |                  |              |

| R/W-0        | R/W-0                                     | R/W-0                                       | R/W-0          | R/W-0                 | R/W-0            | R/W-1            | R/W-1        |

| EXTR         | SWR                                       | SWDTEN <sup>(2)</sup>                       | WDTO           | SLEEP                 | IDLE             | BOR              | POR          |

| bit 7        |                                           |                                             |                |                       |                  |                  | bit          |

| Legend:      |                                           |                                             |                |                       |                  |                  |              |

| R = Readal   | ole bit                                   | W = Writable b                              | oit            | U = Unimplem          | nented bit, read | l as '0'         |              |

| -n = Value a | at POR                                    | '1' = Bit is set                            |                | '0' = Bit is clea     | ared             | x = Bit is unk   | nown         |

| hit 1E       |                                           | Deast Flag bit                              |                |                       |                  |                  |              |

| bit 15       | -                                         | Reset Flag bit<br>onflict Reset has         | occurred       |                       |                  |                  |              |

|              |                                           | onflict Reset has                           |                | d                     |                  |                  |              |

| bit 14       | IOPUWR: Ille                              | gal Opcode or l                             | Jninitialized  | W Access Rese         | et Flag bit      |                  |              |

|              | 1 = An illega                             | al opcode detec                             | tion, an illeg | gal address mo        | de or Uninitial  | ized W registe   | er used as a |

|              |                                           | Pointer caused                              |                | Dogistor Dogot k      | an not anourra   | d                |              |

| bit 13-12    | -                                         | l opcode or Unir                            |                | Register Reset r      | las not occurre  | u                |              |

| bit 11       | •                                         | i <b>ted:</b> Read as '0<br>ash Voltage Reg |                | by During Sloop       | , bit            |                  |              |

|              |                                           | Itage regulator i                           |                |                       | זומ מ            |                  |              |

|              |                                           | Itage regulator                             |                |                       | ing Sleep        |                  |              |

| bit 10       | Unimplemen                                | ted: Read as '0                             | ,              | -                     |                  |                  |              |

| bit 9        | CM: Configur                              | ation Mismatch                              | Flag bit       |                       |                  |                  |              |

|              | •                                         | uration Mismatcl                            |                |                       |                  |                  |              |

|              | •                                         | uration Mismatcl                            |                |                       |                  |                  |              |

| bit 8        |                                           | age Regulator S                             |                |                       |                  |                  |              |

|              |                                           | egulator is activ                           |                |                       |                  |                  |              |

| bit 7        | -                                         | nal Reset (MCLF                             | -              | node during Sie       | eb.              |                  |              |

|              |                                           | Clear (pin) Res                             | ,              | red                   |                  |                  |              |

|              |                                           | Clear (pin) Res                             |                |                       |                  |                  |              |

| bit 6        | SWR: Softwa                               | IRE RESET (Instru                           | uction) Flag   | bit                   |                  |                  |              |

|              |                                           | instruction has l                           |                |                       |                  |                  |              |

|              |                                           | instruction has i                           |                |                       |                  |                  |              |

| bit 5        |                                           | oftware Enable/[                            | Disable of W   | DT bit <sup>(2)</sup> |                  |                  |              |

|              | 1 = WDT is e<br>0 = WDT is d              |                                             |                |                       |                  |                  |              |

| bit 4        |                                           | hdog Timer Tim                              | e-out Elag bi  | it                    |                  |                  |              |

| with i       |                                           | e-out has occurr                            | -              |                       |                  |                  |              |

|              |                                           | e-out has not oc                            |                |                       |                  |                  |              |

|              | All of the Reset sta<br>cause a device Re |                                             | set or cleare  | d in software. S      | etting one of th | ese bits in soft | ware does no |

| <b>2:</b>    | f the FWDTEN Co                           | onfiguration bit is                         | s '1' (unprog  | rammed), the W        | /DT is always e  | nabled, regard   | lless of the |

### RCON: RESET CONTROL REGISTER<sup>(1)</sup> **REGISTER 6-1:**

e сy SWDTEN bit setting.

NOTES:

| R/W-0         | R/W-0       | R/W-0                                 | U-0          | U-0              | U-0             | U-0               | U-0    |

|---------------|-------------|---------------------------------------|--------------|------------------|-----------------|-------------------|--------|

| FRMEN         | SPIFSD      | FRMPOL                                | —            | _                | _               | —                 | —      |

| bit 15        |             |                                       |              |                  |                 |                   | bit 8  |

|               |             |                                       |              |                  |                 |                   |        |

| U-0           | U-0         | U-0                                   | U-0          | U-0              | U-0             | R/W-0             | R/W-0  |

|               | <u> </u>    | —                                     |              |                  | _               | FRMDLY            | SPIBEN |

| bit 7         |             |                                       |              |                  |                 |                   | bit 0  |

|               |             |                                       |              |                  |                 |                   |        |

| Legend:       |             |                                       |              |                  |                 |                   |        |

| R = Readable  | e bit       | W = Writable b                        | bit          | U = Unimpler     | nented bit, rea | ad as '0'         |        |

| -n = Value at | POR         | '1' = Bit is set                      |              | '0' = Bit is cle | ared            | x = Bit is unkr   | nown   |

|               |             |                                       |              |                  |                 |                   |        |

| bit 15        |             | med SPIx Suppo                        |              | _                |                 |                   |        |

|               |             |                                       | •            | cpin is used as  | the Frame Sy    | nc pulse input/or | utput) |

| 1.11.4.4      |             | SPIx support is o                     |              |                  |                 |                   |        |

| bit 14        |             | x Frame Sync F                        |              | on Control bit   |                 |                   |        |

|               |             | /nc pulse input (<br>/nc pulse output |              |                  |                 |                   |        |

| bit 13        | -           | ame Sync Pulse                        | . ,          |                  |                 |                   |        |

|               |             | /nc pulse is activ                    | ,            |                  |                 |                   |        |

|               |             | /nc pulse is activ                    | U U          |                  |                 |                   |        |

| bit 12-2      | Unimplemen  | ted: Read as '0                       | ,            |                  |                 |                   |        |

| bit 1         | FRMDLY: Fra | ame Sync Pulse                        | Edge Select  | t bit            |                 |                   |        |

|               |             | /nc pulse coinci                      |              |                  |                 |                   |        |

|               | -           | nc pulse preced                       |              |                  |                 |                   |        |

| bit 0         |             | x Enhanced Bu                         |              | bit              |                 |                   |        |

|               |             | d Buffer is enabl                     |              | d modo)          |                 |                   |        |

|               |             | d Buffer is disab                     | ieu (Standan | u moue)          |                 |                   |        |

### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                              |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                       |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                      |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                  |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>                                                   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                 |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                   |

|       | 0 = Framing error has not been detected                                                                                                                                                                                    |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets<br/>the receive buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                 |

|       | <ul><li>1 = Receive buffer has data, at least one more character can be read</li><li>0 = Receive buffer is empty</li></ul>                                                                                                 |

|       |                                                                                                                                                                                                                            |

Note 1: Refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) for information on enabling the UART module for transmit operation.

| U-0           | R/W-x                        | U-0                          | U-0             | U-0              | R/W-x            | R/W-x            | R/W-x   |

|---------------|------------------------------|------------------------------|-----------------|------------------|------------------|------------------|---------|

|               | WAKFIL                       | _                            | —               |                  | SEG2PH2          | SEG2PH1          | SEG2PH0 |

| bit 15        |                              |                              |                 |                  |                  |                  | bit 8   |

|               |                              |                              |                 |                  |                  |                  |         |

| R/W-x         | R/W-x                        | R/W-x                        | R/W-x           | R/W-x            | R/W-x            | R/W-x            | R/W-x   |

| SEG2PHTS      | S SAM                        | SEG1PH2                      | SEG1PH1         | SEG1PH0          | PRSEG2           | PRSEG1           | PRSEG0  |

| bit 7         |                              |                              |                 |                  |                  |                  | bit (   |

| Legend:       |                              |                              |                 |                  |                  |                  |         |

| R = Readabl   | e bit                        | W = Writable                 | bit             | U = Unimpler     | nented bit, read | d as '0'         |         |

| -n = Value at | POR                          | '1' = Bit is set             |                 | '0' = Bit is cle | ared             | x = Bit is unkr  | nown    |

|               |                              |                              |                 |                  |                  |                  |         |

| bit 15        | Unimplemer                   | nted: Read as '              | )'              |                  |                  |                  |         |

| bit 14        | WAKFIL: Se                   | lect CAN Bus L               | ne Filter for V | /ake-up bit      |                  |                  |         |

|               |                              | N bus line filter            |                 |                  |                  |                  |         |

|               |                              | line filter is not           |                 | e-up             |                  |                  |         |

| bit 13-11     | Unimplemer                   | nted: Read as '              | )'              |                  |                  |                  |         |

| bit 10-8      |                              | 0>: Phase Segr               | nent 2 bits     |                  |                  |                  |         |

|               | 111 = Length                 | h is 8 x Tq                  |                 |                  |                  | PRSEG1           |         |

|               | •                            |                              |                 |                  |                  |                  |         |

|               | •                            |                              |                 |                  |                  |                  |         |

|               | 000 <b>= Lengt</b> ł         | h is 1 x Tq                  |                 |                  |                  |                  |         |

| bit 7         |                              | Phase Segmer                 | nt 2 Time Sele  | ct bit           |                  |                  |         |

|               | 1 = Freely pr<br>0 = Maximun | ogrammable<br>n of SEG1PHx I | oits or Informa | tion Processin   | g Time (IPT), w  | /hichever is gre | ater    |

| bit 6         | SAM: Sampl                   | e of the CAN B               | us Line bit     |                  |                  |                  |         |

|               |                              | is sampled three             |                 |                  |                  |                  |         |

|               |                              | is sampled once              | -               | e point          |                  |                  |         |

| bit 5-3       |                              | 0>: Phase Segr               | nent 1 bits     |                  |                  |                  |         |

|               | 111 = Length<br>•            | IS 8 X IQ                    |                 |                  |                  |                  |         |

|               | •                            |                              |                 |                  |                  |                  |         |

|               | •                            |                              |                 |                  |                  |                  |         |

|               | 000 = Length                 |                              |                 |                  |                  |                  |         |

| bit 2-0       |                              | >: Propagation               | Time Segmen     | t bits           |                  |                  |         |

|               | 111 = Lengt                  | n IS 8 X I Q                 |                 |                  |                  |                  |         |

|               | •                            |                              |                 |                  |                  |                  |         |

|               | •                            |                              |                 |                  |                  |                  |         |

|               | •<br>•<br>•<br>000 = Lengtł  |                              |                 |                  |                  |                  |         |

### REGISTER 21-22: CxRXFUL1: CANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0 | R/C-0        | R/C-0             | R/C-0          | R/C-0            | R/C-0 | R/C-0 |

|---------|-------|--------------|-------------------|----------------|------------------|-------|-------|

|         |       |              | RXFUL             | <15:8>         |                  |       |       |

| bit 15  |       |              |                   |                |                  |       | bit 8 |

|         |       |              |                   |                |                  |       |       |

| R/C-0   | R/C-0 | R/C-0        | R/C-0             | R/C-0          | R/C-0            | R/C-0 | R/C-0 |

|         |       |              | RXFU              | L<7:0>         |                  |       |       |

| bit 7   |       |              |                   |                |                  |       | bit 0 |

|         |       |              |                   |                |                  |       | ,     |

| Legend: |       | C = Writable | oit, but only '0' | can be written | to clear the bit |       |       |

| Legend:           | C = Writable bit, but only '0' | can be written to clear the bit |                    |

|-------------------|--------------------------------|---------------------------------|--------------------|

| R = Readable bit  | W = Writable bit               | U = Unimplemented bit, read     | as '0'             |

| -n = Value at POR | '1' = Bit is set               | '0' = Bit is cleared            | x = Bit is unknown |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### REGISTER 21-23: CxRXFUL2: CANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0           | R/C-0 | R/C-0            | R/C-0           | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|-----------------|-------|------------------|-----------------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | RXFU            | _<31:24>          |                 |                 |       |

| bit 15          |       |                  |                 |                   |                 |                 | bit 8 |

|                 |       |                  |                 |                   |                 |                 |       |

| R/C-0           | R/C-0 | R/C-0            | R/C-0           | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|                 |       |                  | RXFU            | _<23:16>          |                 |                 |       |

| bit 7           |       |                  |                 |                   |                 |                 | bit 0 |

|                 |       |                  |                 |                   |                 |                 |       |

| Legend:         |       | C = Writable b   | it, but only '( | )' can be written | to clear the bi | it              |       |

| R = Readable    | bit   | W = Writable b   | oit             | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0

RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### 22.1 CTMU Control Registers

### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

| R/W-0                        | U-0                                                                                                              | R/W-0                                 | R/W-0        | R/W-0                | R/W-0                    | R/W-0                  | R/W-0  |  |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|----------------------|--------------------------|------------------------|--------|--|--|--|--|--|

| CTMUEN                       | _                                                                                                                | CTMUSIDL                              | TGEN         | EDGEN                | EDGSEQEN                 | IDISSEN <sup>(1)</sup> | CTTRIG |  |  |  |  |  |

| pit 15                       |                                                                                                                  |                                       |              |                      |                          | L                      | bit 8  |  |  |  |  |  |

|                              |                                                                                                                  |                                       |              |                      |                          |                        |        |  |  |  |  |  |

| U-0                          | U-0                                                                                                              | U-0                                   | U-0          | U-0                  | U-0                      | U-0                    | U-0    |  |  |  |  |  |

| —                            | —                                                                                                                | —                                     | —            | —                    | —                        | —                      | —      |  |  |  |  |  |

| pit 7                        |                                                                                                                  |                                       |              |                      |                          |                        | bit (  |  |  |  |  |  |

| o er o ro d i                |                                                                                                                  |                                       |              |                      |                          |                        |        |  |  |  |  |  |

| -egend:                      | , hit                                                                                                            | W - Writchlo h                        |              |                      | aantad hit raad          | aa '0'                 |        |  |  |  |  |  |

| R = Readable<br>n = Value at |                                                                                                                  | W = Writable b<br>'1' = Bit is set    | It           | 0 = Onimplen         | nented bit, read         | x = Bit is unkn        |        |  |  |  |  |  |

| n = value at                 | PUR                                                                                                              | I = DILIS SEL                         |              |                      | areu                     |                        | JWII   |  |  |  |  |  |

| oit 15                       |                                                                                                                  | TMI I Enable bit                      |              |                      |                          |                        |        |  |  |  |  |  |

|                              | CTMUEN: CTMU Enable bit<br>1 = Module is enabled                                                                 |                                       |              |                      |                          |                        |        |  |  |  |  |  |

|                              | 1 = Module is enabled<br>0 = Module is disabled                                                                  |                                       |              |                      |                          |                        |        |  |  |  |  |  |

| oit 14                       | Unimpleme                                                                                                        | nted: Read as '0'                     |              |                      |                          |                        |        |  |  |  |  |  |

| oit 13                       | CTMUSIDL:                                                                                                        | CTMU Stop in Id                       | le Mode bit  |                      |                          |                        |        |  |  |  |  |  |

|                              |                                                                                                                  | nues module ope                       |              | device enters lo     | lle mode                 |                        |        |  |  |  |  |  |

|                              | 0 = Continues module operation in Idle mode                                                                      |                                       |              |                      |                          |                        |        |  |  |  |  |  |

| pit 12                       | TGEN: Time Generation Enable bit                                                                                 |                                       |              |                      |                          |                        |        |  |  |  |  |  |

|                              |                                                                                                                  | edge delay gene<br>s edge delay gene  |              |                      |                          |                        |        |  |  |  |  |  |

| pit 11                       | EDGEN: Edge Enable bit                                                                                           |                                       |              |                      |                          |                        |        |  |  |  |  |  |

|                              | 1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)                                               |                                       |              |                      |                          |                        |        |  |  |  |  |  |

|                              | 0 = Software is used to trigger edges (manual set of EDGxSTAT)                                                   |                                       |              |                      |                          |                        |        |  |  |  |  |  |

| pit 10                       | EDGSEQEN                                                                                                         | : Edge Sequence                       | e Enable bit |                      |                          |                        |        |  |  |  |  |  |

|                              | 1 = Edge 1 event must occur before Edge 2 event can occur                                                        |                                       |              |                      |                          |                        |        |  |  |  |  |  |

|                              | 0 = No edge sequence is needed                                                                                   |                                       |              |                      |                          |                        |        |  |  |  |  |  |

| bit 9                        | <b>IDISSEN:</b> Analog Current Source Control bit <sup>(1)</sup><br>1 = Analog current source output is grounded |                                       |              |                      |                          |                        |        |  |  |  |  |  |

|                              | •                                                                                                                | current source ou                     |              |                      |                          |                        |        |  |  |  |  |  |

| oit 8                        | -                                                                                                                | Cx Trigger Contr                      |              | Janaca               |                          |                        |        |  |  |  |  |  |

|                              |                                                                                                                  | riggers ADCx sta                      |              | n                    |                          |                        |        |  |  |  |  |  |

|                              |                                                                                                                  | loes not trigger A                    |              |                      |                          |                        |        |  |  |  |  |  |

| oit 7-0                      |                                                                                                                  | nted: Read as '0'                     |              |                      |                          |                        |        |  |  |  |  |  |

|                              |                                                                                                                  |                                       |              | n n nito n i n n n t | the meetic all the state |                        |        |  |  |  |  |  |

|                              |                                                                                                                  | ile Sample-and-H<br>on cycles. Any sc |              |                      |                          |                        |        |  |  |  |  |  |

sample/conversion cycles. Any software using the ADCx as part of a capacitance measurement must discharge the ADCx capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADCx must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

### REGISTER 26-2: CMxCON: OP AMP/COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits <sup>(3)</sup>                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)                                                                                                                                           |

|         | 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator<br>output (while CEVT = 0)                                                                                                     |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                     |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                 |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator<br>output (while CEVT = 0)                                                                                                     |

|         | If CPOL = 1 (inverted polarity):                                                                                                                                                                                                         |

|         | High-to-low transition of the comparator output.                                                                                                                                                                                         |

|         | If CPOL = 0 (non-inverted polarity):                                                                                                                                                                                                     |

|         | Low-to-high transition of the comparator output.                                                                                                                                                                                         |

|         | 00 = Trigger/event/interrupt generation is disabled.                                                                                                                                                                                     |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                               |

| bit 4   | CREF: Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                        |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage</li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                   |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                               |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                           |

|         | <ul> <li>11 = Inverting input of op amp/comparator connects to CxIN4- pin</li> <li>10 = Inverting input of op amp/comparator connects to CxIN3- pin</li> <li>01 = Inverting input of op amp/comparator connects to CxIN2- pin</li> </ul> |

| Note 1: | 00 = Inverting input of op amp/comparator connects to CxIN1- pin                                                                                                                                                                         |

| NULE I. | I IIIVUIA ILIAI ALE AEIEVIEU ALU IIVI AVAIIAVIE WIIIVE IIEVIIVIVAA. AEE ILIE IE <b>III VIAVIAIIIS</b> I SECIIVII IVI AVAIIAVIE                                                                                                           |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPMODE bit only enables the op amp while the comparator is still functional.

- **3:** After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), **must be cleared** before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

| R/W-0                           | R/W-0                                          | R/W-0                                                         | R/W-0            | R/W-0        | R/W-0                      | R/W-0    | R/W-0  |  |  |

|---------------------------------|------------------------------------------------|---------------------------------------------------------------|------------------|--------------|----------------------------|----------|--------|--|--|

| PTEN15 PTEN14 PTEN<13:8>        |                                                |                                                               |                  |              |                            |          |        |  |  |

| bit 15                          |                                                |                                                               |                  |              |                            |          | bit 8  |  |  |

|                                 |                                                |                                                               |                  |              |                            |          |        |  |  |

| R/W-0                           | R/W-0                                          | R/W-0                                                         | R/W-0            | R/W-0        | R/W-0                      | R/W-0    | R/W-0  |  |  |

|                                 |                                                | PTEN                                                          | <7:2>            |              |                            | PTEN     | l<1:0> |  |  |

| bit 7                           |                                                |                                                               |                  |              |                            |          | bit 0  |  |  |

|                                 |                                                |                                                               |                  |              |                            |          |        |  |  |

| Legend:                         |                                                |                                                               |                  |              |                            |          |        |  |  |

| R = Readabl                     | e bit                                          | W = Writable bit                                              |                  | U = Unimplem | nented bit, read           | l as '0' |        |  |  |

| -n = Value at                   | t Reset                                        | '1' = Bit is set '0' = Bit is                                 |                  |              | cleared x = Bit is unknown |          |        |  |  |

|                                 |                                                |                                                               |                  |              |                            |          |        |  |  |

| bit 15                          | PTEN15: PMCS2 Strobe Enable bit                |                                                               |                  |              |                            |          |        |  |  |

|                                 | 1 = PMA15 functions as either PMA<15> or PMCS2 |                                                               |                  |              |                            |          |        |  |  |

|                                 | 0 = PMA15 ft                                   | unctions as por                                               | t I/O            |              |                            |          |        |  |  |

| bit 14                          | PTEN14: PM                                     | ICS1 Strobe En                                                | able bit         |              |                            |          |        |  |  |

|                                 |                                                | unctions as eith                                              | •••••••••••••••• | or PMCS1     |                            |          |        |  |  |

| 0 = PMA14 functions as port I/O |                                                |                                                               |                  |              |                            |          |        |  |  |

| bit 13-2                        | PTEN<13:2>: PMP Address Port Enable bits       |                                                               |                  |              |                            |          |        |  |  |

|                                 |                                                | <ul><li>2&gt; function as</li><li>2&gt; function as</li></ul> |                  | lines        |                            |          |        |  |  |

| bit 1-0                         | PTEN<1:0>:                                     | PMALH/PMALI                                                   | L Strobe Enab    | le bits      |                            |          |        |  |  |

|                                 |                                                |                                                               |                  |              |                            |          |        |  |  |

1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL

## REGISTER 28-4: PMAEN: PARALLEL MASTER PORT ADDRESS ENABLE REGISTER<sup>(1)</sup>

Note 1: This register is not available on 44-pin devices.

0 = PMA1 and PMA0 function as port I/Os

© 2013-2014 Microchip Technology Inc.

### 33.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EPXXXGM3XX/6XX/ 7XX AC characteristics and timing parameters.

### TABLE 33-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended<br>Operating voltage VDD range as described in <b>Section 33.1 "DC</b><br><b>Characteristics</b> ". |

|                    |                                                                                                                                                                                                 |

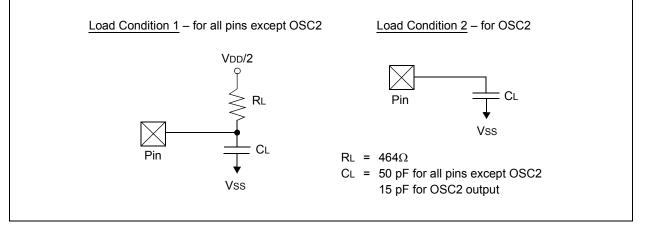

### FIGURE 33-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 33-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | —    | 400  | pF    | In I <sup>2</sup> C™ mode                                           |

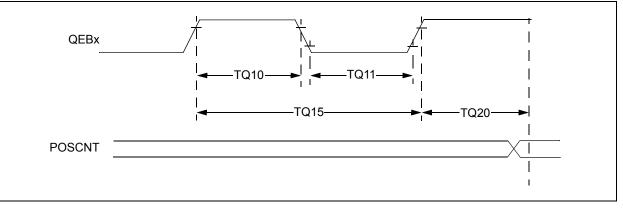

### FIGURE 33-12: TIMERQ (QEIX MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS

### TABLE 33-29: QEIX MODULE EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                              |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                  |  |

|--------------------|-----------|--------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                |                                | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions                       |  |

| TQ10               | TtQH      | TQCK High<br>Time                                            | Synchronous,<br>with Prescaler | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                       | —    | _    | ns    | Must also meet<br>Parameter TQ15 |  |

| TQ11               | TtQL      | TQCK Low<br>Time                                             | Synchronous,<br>with Prescaler | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                       | —    | _    | ns    | Must also meet<br>Parameter TQ15 |  |

| TQ15               | TtQP      | TQCP Input<br>Period                                         | Synchronous,<br>with Prescaler | Greater of:<br>25 + 50 or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                           | —    | _    | ns    |                                  |  |

| TQ20               | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                | _                                                                                                                                                                                                                                                                                     | 1    | Тсү  | —     |                                  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

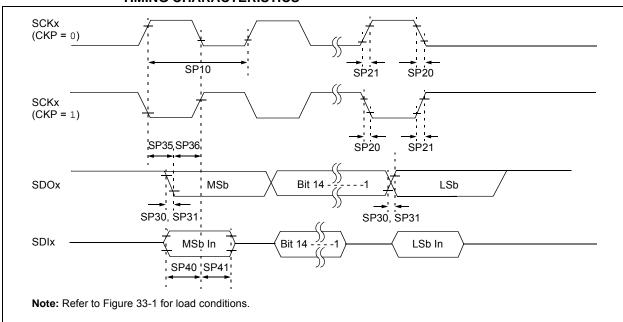

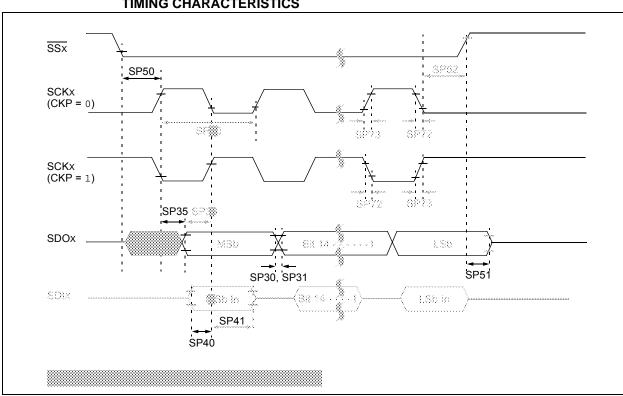

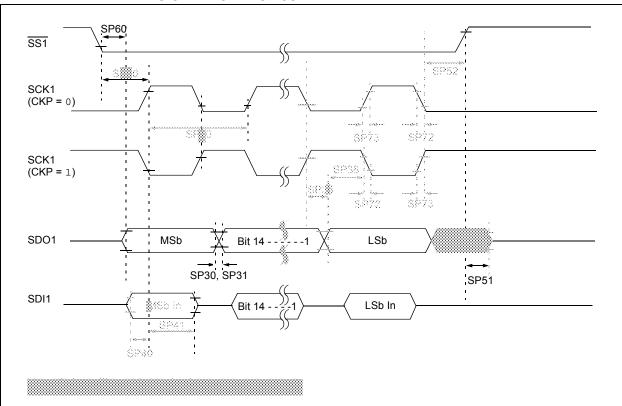

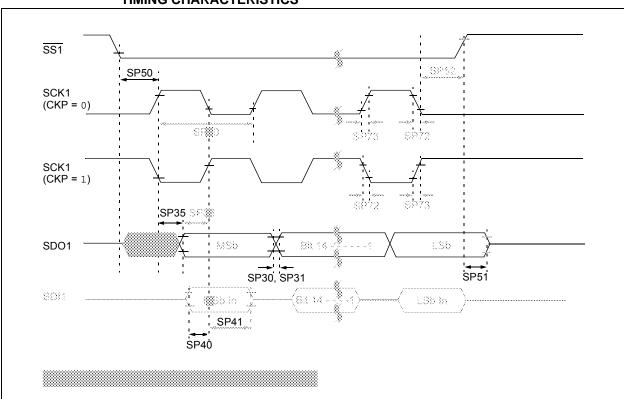

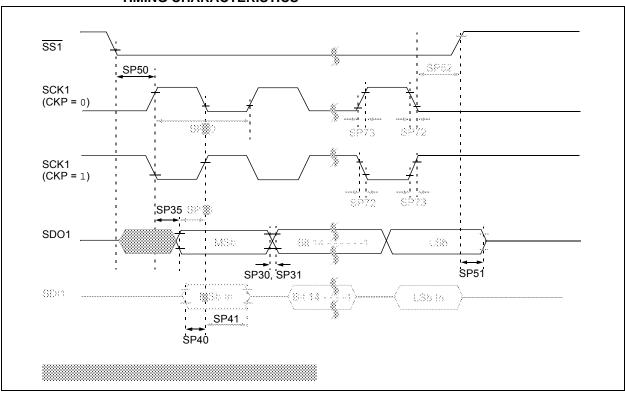

### FIGURE 33-18: SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 33-35:SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |    |     |                             |  |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-----|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min. Typ. <sup>(2)</sup> Max. Units Condition                                                                                                                                                                                                                                           |   |    |     |                             |  |

| SP10               | FscP                  | Maximum SCKx Frequency                        |                                                                                                                                                                                                                                                                                         | — | 9  | MHz | -40°C to +125°C<br>(Note 3) |  |

| SP20               | TscF                  | SCKx Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | — | _  | ns  | See Parameter DO32 (Note 4) |  |

| SP21               | TscR                  | SCKx Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | — | _  | ns  | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | — | _  | ns  | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | — | _  | ns  | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | _                                                                                                                                                                                                                                                                                       | 6 | 20 | ns  |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                                                                                                                                                                                                                                                      | — | _  | ns  |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                                                                                                                                                                                                                                                      | — | —  | ns  |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                                                                                                                                                                                                                                                                      | _ |    | ns  |                             |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.