Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm604-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

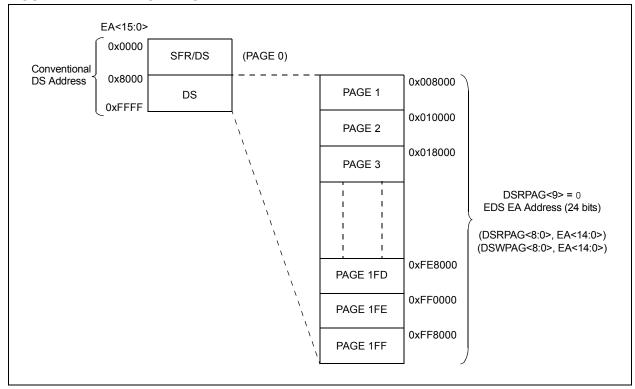

#### 4.2 Data Address Space

The dsPIC33EPXXXGM3XX/6XX/7XX CPU has a separate 16-bit wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-5 through Figure 4-7.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a Base Data Space address range of 64 Kbytes or 32K words.

The Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGM3XX/6XX/7XX devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all zero word or byte is returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

# 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC® MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGM3XX/6XX/7XX instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGM3XX/6XX/7XX core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

Note:

The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

| TARI F 4-49. | PORTR REGISTER MAP F | FOR dsPIC33EPXXXGM310/710 DEVICES |

|--------------|----------------------|-----------------------------------|

|              |                      |                                   |

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E10  |        |        |        |        |        |        |       | TRISB<15  | :0>   |       |       |       |       |       |       |       | DF9F          |

| PORTB       | 0E12  |        |        |        |        |        |        |       | RB<15:0   | >     |       |       |       |       |       |       |       | xxxx          |

| LATB        | 0E14  |        |        |        |        |        |        |       | LATB<15:  | 0>    |       |       |       |       |       |       |       | xxxx          |

| ODCB        | 0E16  |        |        |        |        |        |        |       | ODCB<15   | :0>   |       |       |       |       |       |       |       | 0000          |

| CNENB       | 0E18  |        |        |        |        |        |        |       | CNIEB<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1A  |        |        |        |        |        |        |       | CNPUB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPDB       | 0E1C  |        |        |        |        |        |        |       | CNPDB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| ANSELB      | 0E1E  | _      |        | _      | _      | -      | _      |       | ANSB<9:7> | •     | _     | _     | -     |       | ANSB  | <3:0> | •     | 010F          |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-50: PORTB REGISTER MAP FOR dsPIC33EPXXXGM306/706 DEVICES

|             |       | _      |        | _      | _      |        |        |       |           |       |       |       |       |       |       |        |       |               |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|--------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | AII<br>Resets |

| TRISB       | 0E10  |        |        |        |        |        |        |       | TRISB<15  | 0>    |       |       |       |       |       |        |       | DF9F          |

| PORTB       | 0E12  |        |        |        |        |        |        |       | RB<15:0   | >     |       |       |       |       |       |        |       | xxxx          |

| LATB        | 0E14  |        |        |        |        |        |        |       | LATB<15:  | )>    |       |       |       |       |       |        |       | xxxx          |

| ODCB        | 0E16  |        |        |        |        |        |        |       | ODCB<15   | 0>    |       |       |       |       |       |        |       | 0000          |

| CNENB       | 0E18  |        |        |        |        |        |        |       | CNIEB<15  | :0>   |       |       |       |       |       |        |       | 0000          |

| CNPUB       | 0E1A  |        |        |        |        |        |        |       | CNPUB<15  | :0>   |       |       |       |       |       |        |       | 0000          |

| CNPDB       | 0E1C  |        |        |        |        |        |        |       | CNPDB<15  | :0>   |       |       |       |       |       |        |       | 0000          |

| ANSELB      | 0E1E  | _      | _      | _      | _      | _      | _      |       | ANSB<9:7> |       | _     | _     | _     |       | ANSB  | 3<3:0> |       | 010F          |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-51: PORTB REGISTER MAP FOR dsPIC33EPXXXGM304/604 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|--------|-----------------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|--------|-------|---------------|

| TRISB       | 0E10  |        |                 |        |        |        |        |       | TRISB<15  | :0>   |       |       |       |       |       |        |       | FFFF          |

| PORTB       | 0E12  |        |                 |        |        |        |        |       | RB<15:0   | >     |       |       |       |       |       |        |       | xxxx          |

| LATB        | 0E14  |        | LATB<15:0> x    |        |        |        |        |       |           | xxxx  |       |       |       |       |       |        |       |               |

| ODCB        | 0E16  |        |                 |        |        |        |        |       | ODCB<15   | :0>   |       |       |       |       |       |        |       | 0000          |

| CNENB       | 0E18  |        |                 |        |        |        |        |       | CNIEB<15  | :0>   |       |       |       |       |       |        |       | 0000          |

| CNPUB       | 0E1A  |        |                 |        |        |        |        |       | CNPUB<15  | 5:0>  |       |       |       |       |       |        |       | 0000          |

| CNPDB       | 0E1C  |        | CNPDB<15:0> 000 |        |        |        |        |       |           |       | 0000  |       |       |       |       |        |       |               |

| ANSELB      | 0E1E  | 1      | _               | _      | _      | _      | _      |       | ANSB<9:7> | •     | _     | _     | _     |       | ANSB  | 3<3:0> |       | 010F          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

**2:** Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG register, in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-11.

For more information on the PSV page access, using Data Space Page registers, refer to the "Program Space Visibility from Data Space" section in "Program Memory" (DS70613) of the "dsPIC33/PIC24 Family Reference Manual".

#### FIGURE 4-11: EDS MEMORY MAP

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   |     | _   |     | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-0   | W-0         | W-0 | W-0 | W-0 | W-0 | W-0 | W-0   |  |  |  |  |  |

|-------|-------------|-----|-----|-----|-----|-----|-------|--|--|--|--|--|

|       | NVMKEY<7:0> |     |     |     |     |     |       |  |  |  |  |  |

| bit 7 |             |     |     |     |     |     | bit 0 |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **NVMKEY<7:0>:** NVM Key Register (write-only) bits

### REGISTER 5-5: NVMSRCADRH: NONVOLATILE DATA MEMORY UPPER ADDRESS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x | R/W-x | R/W-x | R/W-x    | R/W-x      | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|----------|------------|-------|-------|-------|

|       |       |       | NVMSRCAD | ORH<23:16> |       |       |       |

| bit 7 |       |       |          |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **NVMSRCADRH<23:16>:** Nonvolatile Data Memory Upper Address bits

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

bit 3

ADDRERR: Address Error Trap Status bit

1 = Address error trap has occurred

0 = Address error trap has not occurred

bit 2

STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred

0 = Stack error trap has not occurred

bit 1

OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

bit 0

Unimplemented: Read as '0'

#### PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup> **REGISTER 9-3:**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0     |

|--------|-----|-----|-----|-----|-----|-----|-----------|

| _      | _   | _   | _   | _   | _   | _   | PLLDIV<8> |

| bit 15 |     |     |     |     |     |     | bit 8     |

| R/W-0       | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| PLLDIV<7:0> |       |       |       |       |       |       |       |  |  |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 Unimplemented: Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

111111111 = 513

000110000 = 50 (default)

00000010 = 4

000000001 = 3

000000000 = 2

**Note 1:** This register is reset only on a Power-on Reset (POR).

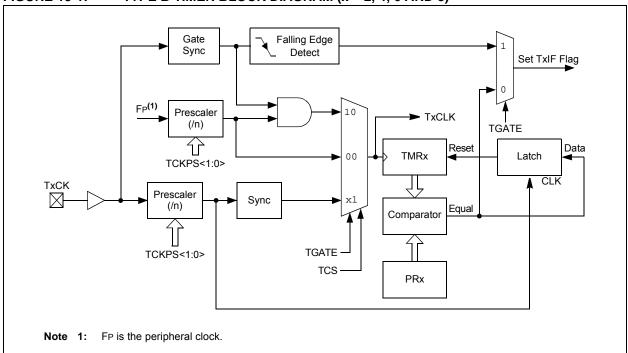

FIGURE 13-1: TYPE B TIMER BLOCK DIAGRAM (x = 2, 4, 6 AND 8)

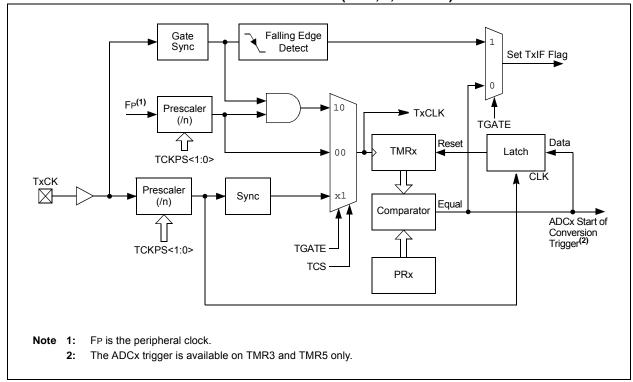

## FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3, 5, 7 AND 9)

## REGISTER 17-3: QEIXSTAT: QEIX STATUS REGISTER (CONTINUED)

bit 2 **HOMIEN:** Home Input Event Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 1 IDXIRQ: Status Flag for Index Event Status bit

1 = Index event has occurred0 = No index event has occurred

bit 0 IDXIEN: Index Input Event Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

**Note 1:** This status bit is only applicable to PIMOD<2:0> = 011 and 100 modes.

#### REGISTER 17-19: INTXHLDH: INTERVAL TIMERX HOLD HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|---------|-------|-------|-------|

|        |       |       | INTHLD | <31:24> |       |       |       |

| bit 15 |       |       |        |         |       |       | bit 8 |

| R/W-0 | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|---------------|-------|-------|-------|-------|-------|-------|--|--|

|       | INTHLD<23:16> |       |       |       |       |       |       |  |  |

| bit 7 |               |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 INTHLD<31:16>: Holding Register for Reading and Writing INTxTMRH bits

#### REGISTER 17-20: INTxHLDL: INTERVAL TIMERX HOLD LOW WORD REGISTER

| R/W-0  | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|

|        | INTHLD<15:8> |       |       |       |       |       |       |  |  |

| bit 15 |              |       |       |       |       |       | bit 8 |  |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| INTHLD<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 INTHLD<15:0>: Holding Register for Reading and Writing INTxTMRL bits

#### REGISTER 21-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F15BP3 | F15BP2 | F15BP1 | F15BP0 | F14BP3 | F14BP2 | F14BP1 | F14BP0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F13BP3 | F13BP2 | F13BP1 | F13BP0 | F12BP3 | F12BP2 | F12BP1 | F12BP0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F15BP<3:0>: RX Buffer Mask for Filter 15 bits

1111 = Filter hits received in RX FIFO buffer 1110 = Filter hits received in RX Buffer 14

•

.

0001 = Filter hits received in RX Buffer 1 0000 = Filter hits received in RX Buffer 0

bit 11-8 **F14BP<3:0>:** RX Buffer Mask for Filter 14 bits (same values as bits 15-12) bit 7-4 **F13BP<3:0>:** RX Buffer Mask for Filter 13 bits (same values as bits 15-12)

bit 3-0 F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12)

# REGISTER 25-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER<sup>(1,2)</sup>

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADCTS4 | ADCTS3 | ADCTS2 | ADCTS1 | IC4TSS | IC3TSS | IC2TSS | IC1TSS |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| OC4CS | OC3CS | OC2CS | OC1CS | OC4TSS | OC3TSS | OC2TSS | OC1TSS |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | ADCTS4: Sample Trigger PTGO15 for ADCx bit                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Generates trigger when the broadcast command is executed                                                                                                                                   |

|         | 0 = Does not generate trigger when the broadcast command is executed                                                                                                                           |

| bit 14  | ADCTS3: Sample Trigger PTGO14 for ADCx bit                                                                                                                                                     |

|         | 1 = Generates trigger when the broadcast command is executed                                                                                                                                   |

| 1.11.40 | 0 = Does not generate trigger when the broadcast command is executed                                                                                                                           |

| bit 13  | ADCTS2: Sample Trigger PTGO13 for ADCx bit                                                                                                                                                     |

|         | <ul><li>1 = Generates trigger when the broadcast command is executed</li><li>0 = Does not generate trigger when the broadcast command is executed</li></ul>                                    |

| bit 12  | ADCTS1: Sample Trigger PTGO12 for ADCx bit                                                                                                                                                     |

|         | <ul><li>1 = Generates trigger when the broadcast command is executed</li><li>0 = Does not generate trigger when the broadcast command is executed</li></ul>                                    |

| bit 11  | IC4TSS: Trigger/Synchronization Source for IC4 bit                                                                                                                                             |

|         | 1 = Generates trigger/synchronization when the broadcast command is executed 0 = Does not generate trigger/synchronization when the broadcast command is executed                              |

| bit 10  | IC3TSS: Trigger/Synchronization Source for IC3 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 9   | IC2TSS: Trigger/Synchronization Source for IC2 bit                                                                                                                                             |

|         | <ul><li>1 = Generates trigger/synchronization when the broadcast command is executed</li><li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li></ul>    |

| bit 8   | IC1TSS: Trigger/Synchronization Source for IC1 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 7   | OC4CS: Clock Source for OC4 bit                                                                                                                                                                |

|         | <ul><li>1 = Generates clock pulse when the broadcast command is executed</li><li>0 = Does not generate clock pulse when the broadcast command is executed</li></ul>                            |

| bit 6   | OC3CS: Clock Source for OC3 bit                                                                                                                                                                |

|         | <ul><li>1 = Generates clock pulse when the broadcast command is executed</li><li>0 = Does not generate clock pulse when the broadcast command is executed</li></ul>                            |

| bit 5   | OC2CS: Clock Source for OC2 bit                                                                                                                                                                |

|         | <ul><li>1 = Generates clock pulse when the broadcast command is executed</li><li>0 = Does not generate clock pulse when the broadcast command is executed</li></ul>                            |

|         |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

# REGISTER 27-9: ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| _      | _   | _   | _   | _   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits

Contains a value from 0 to 6.

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits

Contains a value from 0 to 2.

bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# REGISTER 28-3: PMADDR: PARALLEL MASTER PORT ADDRESS REGISTER (MASTER MODES ONLY)<sup>(1,2)</sup>

| R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|-------|--------|--------|--------|--------|-------|-------|

| CS2    | CS1   | ADDR13 | ADDR12 | ADDR11 | ADDR10 | ADDR9 | ADDR8 |

| bit 15 |       |        |        |        |        |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADDR7 | ADDR6 | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at Reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CS2: Chip Select 2 bit

If PMCON<7:6> = 10 or 01:

1 = Chip Select 2 is active

0 = Chip Select 2 is inactive

If PMCON<7:6> = 11 or 00:

Bit functions as ADDR15.

bit 14 CS1: Chip Select 1 bit

If PMCON<7:6> = 10:

1 = Chip Select 1 is active

0 = Chip Select 1 is inactive

If PMCON<7:6> = 11 or 0x:

Bit functions as ADDR14.

bit 13-0 ADDR<13:0>: Destination Address bits

Note 1: In Enhanced Slave mode, PMADDR functions as PMDOUT1, one of the two Data Buffer registers.

2: This register is not available on 44-pin devices.

# 29.2 Programmable CRC Control Registers

#### REGISTER 29-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0 | R-0    | R-0    | R-0    | R-0    | R-0    |

|--------|-----|-------|--------|--------|--------|--------|--------|

| CRCEN  | _   | CSIDL | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0 |

| bit 15 |     |       |        |        |        |        | bit 8  |

| R-0    | R-1    | R/W-0   | R/W-0 | R/W-0   | U-0 | U-0 | U-0   |

|--------|--------|---------|-------|---------|-----|-----|-------|

| CRCFUL | CRCMPT | CRCISEL | CRCGO | LENDIAN | _   | _   | _     |

| bit 7  |        |         |       |         |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CRCEN: CRC Enable bit

1 = CRC module is enabled

0 = CRC module is disabled; all state machines, pointers and CRCWDAT/CRCDAT are reset, other

SFRs are not reset

bit 14 Unimplemented: Read as '0'

bit 13 CSIDL: CRC Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-8 **VWORD<4:0>:** Valid Word Pointer Value bits

Indicates the number of valid words in the FIFO; has a maximum value of 8 when PLEN<4:0> > 7 or

16 when PLEN<4:0>  $\leq$  7

bit 7 CRCFUL: CRC FIFO Full bit

1 = FIFO is full 0 = FIFO is not full

bit 6 CRCMPT: CRC FIFO Empty Bit

1 = FIFO is empty

0 = FIFO is not empty

bit 5 CRCISEL: CRC Interrupt Selection bit

1 = Interrupt on FIFO empty; final word of data is still shifting through CRC

0 = Interrupt on shift complete and CRCWDAT results are ready

bit 4 CRCGO: CRC Start bit

1 = Start CRC serial shifter

0 = CRC serial shifter is turned off

bit 3 **LENDIAN:** Data Word Little-Endian Configuration bit

1 = Data word is shifted into the CRC starting with the LSb (little endian)

0 = Data word is shifted into the CRC starting with the MSb (big endian)

bit 2-0 **Unimplemented:** Read as '0'

TABLE 33-10: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CH        | ARACTER | RISTICS                                 | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |   |    |    |                                                                                                               |  |  |

|--------------|---------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|---------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol  | Characteristic                          | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                  |   |    |    |                                                                                                               |  |  |

|              | lıL     | Input Leakage Current <sup>(1,2)</sup>  |                                                                                                                                                                                                                                                  |   |    |    |                                                                                                               |  |  |

| DI50         |         | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                                                                                                                                                                                                               | _ | +1 | μΑ | Vss ≤ VPIN ≤ 5V,<br>Pin at high-impedance                                                                     |  |  |

| DI51         |         | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                               | _ | +1 | μΑ | $Vss \leq VPIN \leq VDD, \\ Pin at high-impedance, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C$                 |  |  |

| DI51a        |         | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                               | _ | +1 | μΑ | Analog pins shared with external reference pins, $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  |  |  |

| DI51b        |         | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                               | _ | +1 | μΑ | $Vss \leq VPIN \leq VDD, \\ Pin at high-impedance, \\ -40^{\circ}C \leq TA \leq +125^{\circ}C$                |  |  |

| DI51c        |         | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                               | _ | +1 | μΑ | Analog pins shared with external reference pins, $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ |  |  |

| DI55         |         | MCLR                                    | -5                                                                                                                                                                                                                                               | _ | +5 | μΑ | $Vss \le VPIN \le VDD$                                                                                        |  |  |

| DI56         |         | OSC1                                    | -5                                                                                                                                                                                                                                               | _ | +5 | μΑ | $Vss \leq VPIN \leq VDD, \\ XT \ and \ HS \ modes$                                                            |  |  |

- Note 1: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- 5: Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- **8:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

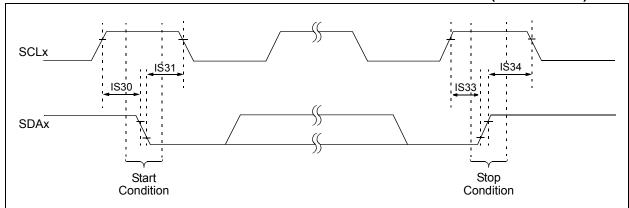

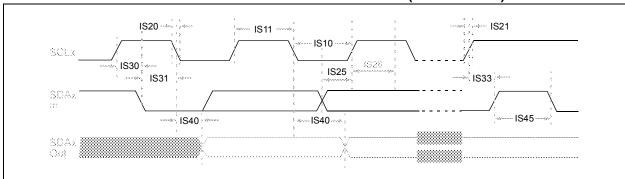

## FIGURE 33-34: I2Cx BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

TABLE 33-52: OP AMP/COMPARATOR SPECIFICATIONS

| DC CH                         | ARACTERIS        | STICS                                     | Standard Operating Conditions (see Note 3): 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ for Extended |                     |              |        |                                                    |  |  |

|-------------------------------|------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|--------|----------------------------------------------------|--|--|

| Param<br>No.                  | Symbol           | Characteristic                            | Min.                                                                                                                                                                                                                                                              | Typ. <sup>(1)</sup> | Max.         | Units  | Conditions                                         |  |  |

| Comparator AC Characteristics |                  |                                           |                                                                                                                                                                                                                                                                   |                     |              |        |                                                    |  |  |

| CM10                          | TRESP            | Response Time                             | _                                                                                                                                                                                                                                                                 | 19                  | _            | ns     | V+ input step of 100 mV,<br>V- input held at VDD/2 |  |  |

| CM11                          | TMC2OV           | Comparator Mode<br>Change to Output Valid | _                                                                                                                                                                                                                                                                 | _                   | 10           | μs     |                                                    |  |  |

| Compa                         | rator DC Ch      | naracteristics                            |                                                                                                                                                                                                                                                                   |                     |              |        |                                                    |  |  |

| CM30                          | Voffset          | Comparator Offset Voltage                 | _                                                                                                                                                                                                                                                                 | ±20                 | ±75          | mV     |                                                    |  |  |

| CM31                          | VHYST            | Input Hysteresis Voltage                  | _                                                                                                                                                                                                                                                                 | 30                  | _            | mV     |                                                    |  |  |

| CM32                          | TRISE/<br>TFALL  | Comparator Output<br>Rise/Fall Time       | _                                                                                                                                                                                                                                                                 | 20                  | _            | ns     | 1 pF load capacitance on input                     |  |  |

| CM33                          | VGAIN            | Open-Loop Voltage Gain                    | _                                                                                                                                                                                                                                                                 | 90                  | _            | db     |                                                    |  |  |

| CM34                          | VICM             | Input Common-Mode<br>Voltage              | AVss                                                                                                                                                                                                                                                              | _                   | AVDD         | V      |                                                    |  |  |

| Op Am                         | p AC Chara       | cteristics                                |                                                                                                                                                                                                                                                                   | •                   |              |        |                                                    |  |  |

| CM20                          | SR               | Slew Rate                                 | _                                                                                                                                                                                                                                                                 | 9                   | _            | V/µs   | 10 pF load                                         |  |  |

| CM21a                         | Рм               | Phase Margin                              | _                                                                                                                                                                                                                                                                 | 68                  | _            | Degree | G = 100V/V; 10 pF load                             |  |  |

| CM22                          | Gм               | Gain Margin                               | _                                                                                                                                                                                                                                                                 | 20                  | _            | db     | G = 100V/V; 10 pF load                             |  |  |

| CM23a                         | G <sub>B</sub> w | Gain Bandwidth                            | _                                                                                                                                                                                                                                                                 | 10                  | _            | MHz    | 10 pF load                                         |  |  |

| Op Am                         | p DC Chara       | cteristics                                |                                                                                                                                                                                                                                                                   |                     |              |        |                                                    |  |  |

| CM40                          | VCMR             | Common-Mode Input<br>Voltage Range        | AVss                                                                                                                                                                                                                                                              | _                   | AVDD         | V      |                                                    |  |  |

| CM41                          | CMRR             | Common-Mode<br>Rejection Ratio            | _                                                                                                                                                                                                                                                                 | 40                  | _            | db     | VCM = AVDD/2                                       |  |  |

| CM42                          | VOFFSET          | Op Amp Offset Voltage                     | _                                                                                                                                                                                                                                                                 | ±20                 | ±70          | mV     |                                                    |  |  |

| CM43                          | VGAIN            | Open-Loop Voltage Gain                    | _                                                                                                                                                                                                                                                                 | 90                  | _            | db     |                                                    |  |  |

| CM44                          | los              | Input Offset Current                      | _                                                                                                                                                                                                                                                                 | _                   | _            | _      | See pad leakage<br>currents in Table 33-10         |  |  |

| CM45                          | lB               | Input Bias Current                        | _                                                                                                                                                                                                                                                                 | _                   | _            | _      | See pad leakage<br>currents in Table 33-10         |  |  |

| CM46                          | lout             | Output Current                            | _                                                                                                                                                                                                                                                                 | _                   | 420          | μΑ     | With minimum value of RFEEDBACK (CM48)             |  |  |

| CM48                          | RFEEDBACK        | Feedback Resistance<br>Value              | 8                                                                                                                                                                                                                                                                 | _                   | _            | kΩ     | (Note 2)                                           |  |  |

| CM49a                         | Vout             | Output Voltage                            | AVss + 0.075                                                                                                                                                                                                                                                      | _                   | AVDD - 0.075 | V      | ΙΟυτ = 420 μΑ                                      |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

<sup>2:</sup> Resistances can vary by ±10% between op amps.

**<sup>3:</sup>** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

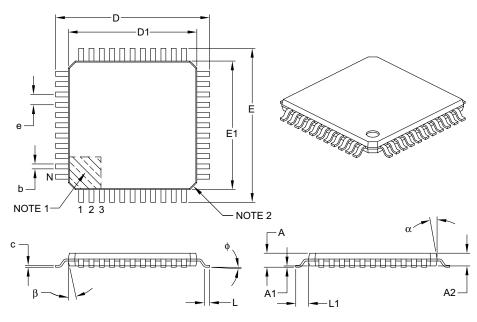

### 35.2 Package Details

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |             |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|-------------|----------|-------------|--|--|--|

| Dimer                    | Dimension Limits |             |          | MAX         |  |  |  |

| Number of Leads          | N                |             | 44       |             |  |  |  |

| Lead Pitch               | е                |             | 0.80 BSC |             |  |  |  |

| Overall Height           | Α                | -           | -        | 1.20        |  |  |  |

| Molded Package Thickness | A2               | 0.95        | 1.00     | 1.05        |  |  |  |

| Standoff                 | A1               | 0.05        | _        | 0.15        |  |  |  |

| Foot Length              | L                | 0.45        | 0.60     | 0.75        |  |  |  |

| Footprint                | L1               | 1.00 REF    |          |             |  |  |  |

| Foot Angle               | ф                | 0° 3.5° 7°  |          |             |  |  |  |

| Overall Width            | Е                | 12.00 BSC   |          |             |  |  |  |

| Overall Length           | D                | 12.00 BSC   |          |             |  |  |  |

| Molded Package Width     | E1               | 10.00 BSC   |          |             |  |  |  |

| Molded Package Length    | D1               | 10.00 BSC   |          |             |  |  |  |

| Lead Thickness           | С                | 0.09 – 0.20 |          |             |  |  |  |

| Lead Width               | b                | 0.30        | 0.37     | 0.45        |  |  |  |

| Mold Draft Angle Top     | α                | 11° 12° 13° |          |             |  |  |  |

| Mold Draft Angle Bottom  | β                | 11° 12° 13° |          |             |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

## 64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

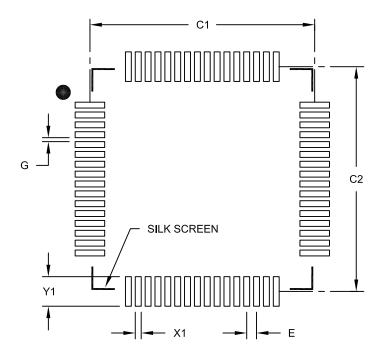

**RECOMMENDED LAND PATTERN**

|                          | MILLIMETERS |          |       |      |

|--------------------------|-------------|----------|-------|------|

| Dimension                | MIN         | NOM      | MAX   |      |

| Contact Pitch            | E           | 0.50 BSC |       |      |

| Contact Pad Spacing      | C1          |          | 11.40 |      |

| Contact Pad Spacing      | C2          |          | 11.40 |      |

| Contact Pad Width (X64)  | X1          |          |       | 0.30 |

| Contact Pad Length (X64) | Y1          |          |       | 1.50 |

| Distance Between Pads    | G           | 0.20     |       |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

| PMP Pinout and Connections to             |

|-------------------------------------------|

| External Devices                          |

| Programmer's Model30                      |

| PTG Module350                             |

| QEIx Module258                            |

| Recommended Minimum Connection22          |

| Remappable Input for U1RX166              |

| Reset System111                           |

| RTCC Module384                            |

| Shared Port Structure                     |

| Single-Phase Synchronous Buck Converter25 |

| SPIx Module                               |

| Suggested Oscillator Circuit Placement    |

| Type B Timer (Timer2/4/6/8)               |

| Type B/Type C Timer Pair (32-Bit Timer)   |

| Type C Timer (Timer3/5/7/9)               |

| UARTx Module                              |

| User-Programmable Blanking Function       |

| Watchdog Timer (WDT)417                   |

| Brown-out Reset (BOR)416                  |

| C                                         |

| C Compilers                               |

| MPLAB XC Compilers430                     |

| CAN Module                                |

| Control Registers297                      |

| Message Buffers                           |

| <u> </u>                                  |

| Word 0                                    |

| Word 2                                    |

| Word 3                                    |

| Word 4                                    |

| Word 5                                    |

| Word 6                                    |

| Word 7                                    |

| Modes of Operation                        |

| Overview                                  |

| CAN Module (CAN)                          |

| Charge Time Measurement Unit (CTMU)       |

| Code Examples                             |

| IC1 Connection to HOME1 QEI1 Digital      |

| Filter Input on Pin 43166                 |

| PORTB Write/Read                          |

| PWM1 Write-Protected Register             |

| Unlock Sequence                           |

| PWRSAV Instruction Syntax                 |

| Code Protection411, 418                   |

| CodeGuard Security411, 418                |

| Configuration Bits411                     |

| Description413                            |

| CPU27                                     |

| Addressing Modes27                        |

| Arithmetic Logic Unit (ALU)35             |

| Control Registers31                       |

| Data Space Addressing27                   |

| DSP Engine35                              |

| Instruction Set27                         |

| Programmer's Model29                      |

| Register Descriptions29                   |

| CTMU                                      |

| Control Registers                         |

| Customer Change Notification Service536   |

| Customer Notification Service536          |

| Customer Support536                       |

| D                                      |          |

|----------------------------------------|----------|

| Data Address Space                     | 41       |

| Memory Map for 128-Kbyte Devices       |          |

| Memory Map for 256-Kbyte Devices       |          |

| Memory Map for 512-Kbyte Devices       |          |

| Near Data Space                        |          |

| Organization and Alignment             |          |

| SFR Space                              |          |

| Width                                  |          |

| Data Converter Interface (DCI) Module  | 343      |

| Data Memory                            |          |

| Arbitration and Bus Master Priority    | 95       |

| DC Characteristics                     | 434      |

| Brown-out Reset (BOR)                  | 443      |

| CTMU Current Source                    | 490      |

| Doze Current (IDOZE)                   | 439, 501 |

| Filter Capacitor (CEFC) Specifications | 435      |

| High Temperature                       | 500      |

| I/O Pin Input Specifications           | 440      |

| I/O Pin Output Specifications          |          |

| Idle Current (IIDLE)                   | 437, 501 |

| Op Amp/Comparator Specifications       | 488      |

| Op Amp/Comparator Voltage              |          |

| Reference Specifications               | 489      |

| Operating Current (IDD)                |          |

| Operating MIPS vs. Voltage             | 434, 500 |

| Power-Down Current (IPD)               |          |

| Program Memory                         | 444, 502 |

| Temperature and Voltage                |          |

| Temperature and Voltage Specifications |          |

| Thermal Operating Conditions           | 434, 500 |

| Thermal Packaging Characteristics      | 434      |

| DCI                                    |          |

| Control Registers                      |          |

| Introduction                           | 343      |

| Demo/Development Boards, Evaluation    |          |

| and Starter Kits                       |          |

| Development Support                    |          |

| Third-Party Tools                      | 432      |

| DMA Controller                         |          |

| Channel to Peripheral Associations     | 130      |

| Control Registers                      |          |

| DMAxCNT                                |          |

| DMAxCON                                |          |

| DMAxPAD                                |          |

| DMAxREQ                                |          |

| DMAxSTAL/H                             |          |

| DMAxSTBL/H                             |          |

| Supported Peripherals                  |          |

| Doze Mode                              | 155      |

| E                                      |          |

|                                        | 400      |

| Electrical Characteristics             |          |

| AC                                     | 445, 503 |

| Equations  Device Operating Frequency  | 4 4 4    |

| Device Operating Frequency             |          |

| Fosc Calculation                       |          |

| Fvco Calculation                       |          |

| Litaid                                 |          |