Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      |                                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | -                                                                                |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm604-h-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

# 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

- Dual motor control

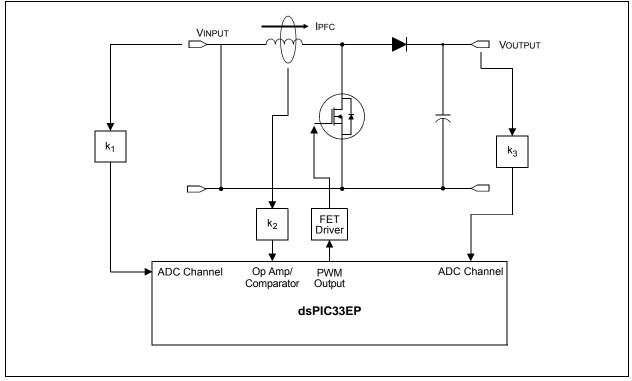

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

## FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

| IABLE 4         | +-/.   | PIG REGISTER MAP           |                       |         |         |         |         |         |         |             |         |         |         |        |           |         |         |               |

|-----------------|--------|----------------------------|-----------------------|---------|---------|---------|---------|---------|---------|-------------|---------|---------|---------|--------|-----------|---------|---------|---------------|

| SFR<br>Name     | Addr.  | Bit 15                     | Bit 14                | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7       | Bit 6   | Bit 5   | Bit 4   | Bit 3  | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

| PTGCST          | 0AC0   | PTGEN                      | _                     | PTGSIDL | PTGTOGL | _       | PTGSWT  | PTGSSEN | PTGIVIS | PTGSTRT     | PTGWDTO | _       | —       | —      | —         | PTGITM1 | PTGITM0 | 0000          |

| PTGCON          | 0AC2   | PTGCLK2                    | PTGCLK1               | PTGCLK0 | PTGDIV4 | PTGDIV3 | PTGDIV2 | PTGDIV1 | PTGDIV0 | PTGPWD3     | PTGPWD2 | PTGPWD1 | PTGPWD0 | _      | PTGWDT2   | PTGWDT1 | PTGWDT0 | 0000          |

| PTGBTE          | 0AC4   | ADCTS4                     | ADCTS3                | ADCTS2  | ADCTS1  | IC4TSS  | IC3TSS  | IC2TSS  | IC1TSS  | OC4CS       | OC3CS   | OC2CS   | OC1CS   | OC4TSS | OC3TSS    | OC2TSS  | OC1TSS  | 0000          |

| PTGHOLD         | 0AC6   |                            |                       |         | •       |         |         | •       | PTGł    | HOLD<15:0>  |         | •       |         | •      | •         |         |         | 0000          |

| PTGT0LIM        | 0AC8   |                            |                       |         |         |         |         |         | PTG     | OLIM<15:0>  |         |         |         |        |           |         |         | 0000          |

| PTGT1LIM        | 0ACA   |                            |                       |         |         |         |         |         | PTG     | TLIM<15:0>  |         |         |         |        |           |         |         | 0000          |

| PTGSDLIM        | 0ACC   |                            |                       |         |         |         |         |         | PTGS    | SDLIM<15:0> |         |         |         |        |           |         |         | 0000          |

| <b>PTGC0LIM</b> | 0ACE   |                            |                       |         |         |         |         |         | PTGC    | COLIM<15:0> |         |         |         |        |           |         |         | 0000          |

| PTGC1LIM        | 0AD0   |                            |                       |         |         |         |         |         | PTGC    | C1LIM<15:0> |         |         |         |        |           |         |         | 0000          |

| PTGADJ          | 0AD2   |                            |                       |         |         |         |         |         | PTG     | ADJ<15:0>   |         |         |         |        |           |         |         | 0000          |

| PTGL0           | 0AD4   |                            |                       |         |         |         |         |         | PT      | GL0<15:0>   |         |         |         |        |           |         |         | 0000          |

| PTGQPTR         | 0AD6   |                            |                       | _       | —       |         |         | _       | —       | —           | —       | —       |         | F      | PTGQPTR<4 | :0>     |         | 0000          |

| PTGQUE0         | 0AD8   |                            | STEP1<7:0> STEP0<7:0> |         |         |         |         |         |         | 0000        |         |         |         |        |           |         |         |               |

| PTGQUE1         | 0ADA   |                            |                       |         | STEP3   | <7:0>   |         |         |         |             |         |         | STEP2   | <7:0>  |           |         |         | 0000          |

| PTGQUE2         | 0ADC   |                            |                       |         | STEP5   | <7:0>   |         |         |         |             |         |         | STEP4   | <7:0>  |           |         |         | 0000          |

| PTGQUE3         | 0ADE   |                            |                       |         | STEP7   | <7:0>   |         |         |         |             |         |         | STEP6   | <7:0>  |           |         |         | 0000          |

| PTGQUE4         | 0AE0   |                            |                       |         | STEP9   | <7:0>   |         |         |         |             |         |         | STEP8   | <7:0>  |           |         |         | 0000          |

| PTGQUE5         | 0AE2   |                            |                       |         | STEP11  | <7:0>   |         |         |         |             |         |         | STEP10  | <7:0>  |           |         |         | 0000          |

| PTGQUE6         | 0AE4   |                            |                       |         | STEP13  | <7:0>   |         |         |         |             |         |         | STEP12  | 2<7:0> |           |         |         | 0000          |

| PTGQUE7         | 0AE6   |                            |                       |         | STEP15  | i<7:0>  |         |         |         |             |         |         | STEP14  | <7:0>  |           |         |         | 0000          |

| PTGQUE8         | 0x0AE8 |                            |                       |         | STEP17  | <7:0>   |         |         |         |             |         |         | STEP16  | 6<7:0> |           |         |         | 0000          |

| PTGQUE9         | 0x0AEA |                            |                       |         | STEP19  | <7:0>   |         |         |         |             |         |         | STEP18  | <7:0>  |           |         |         | 0000          |

| PTGQUE10        | 0x0AEC |                            |                       |         | STEP21  | <7:0>   |         |         |         |             |         |         | STEP20  | <7:0>  |           |         |         | 0000          |

| PTGQUE11        | 0x0AEE |                            |                       |         | STEP23  | <7:0>   |         |         |         |             |         |         | STEP22  | 2<7:0> |           |         |         | 0000          |

| PTGQUE12        | 0x0AF0 |                            |                       |         | STEP25  | <7:0>   |         |         |         |             |         |         | STEP24  | <7:0>  |           |         |         | 0000          |

| PTGQUE13        | 0x0AF2 | STEP27<7:0> STEP26<7:0> 00 |                       |         |         |         |         |         |         | 0000        |         |         |         |        |           |         |         |               |

| PTGQUE14        | 0x0AF4 |                            |                       |         | STEP29  | <7:0>   |         |         |         |             |         |         | STEP28  | <7:0>  |           |         |         | 0000          |

| PTGQUE15        | 0x0AF6 |                            |                       |         | STEP31  | <7:0>   |         |         |         |             |         |         | STEP30  | <7:0>  |           |         |         | 0000          |

#### TABLE 4-7: PTG REGISTER MAP

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-8: PWM REGISTER MAP**

| SFR<br>Name Add | ddr.  | Bit 15               | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit<br>10 | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1       | Bit 0    | All<br>Resets |

|-----------------|-------|----------------------|--------|--------|--------|--------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|-------------|----------|---------------|

| PTCON 0C        | C00   | PTEN                 | —      | PTSIDL | SESTAT | SEIEN  | EIPU      | SYNCPOL  | SYNCOEN  | SYNCEN   | SYNCSRC2 | SYNCSRC1 | SYNCSRC0 | SEVTPS3  | SEVTPS2  | SEVTPS1     | SEVTPS0  | 0000          |

| PTCON2 0C       | C02   | PCLKDIV<2:0>         |        |        |        |        |           |          |          |          |          |          |          | 0000     |          |             |          |               |

| PTPER 0C        | C04   | PTPER<15:0>          |        |        |        |        |           |          |          |          |          |          | 00F8     |          |          |             |          |               |

| SEVTCMP 0C      | C06   |                      |        |        |        |        |           |          |          | SEVTCM   | 1P<15:0> |          |          |          |          |             |          | 0000          |

| MDC 0C          | C0A   |                      |        |        |        |        |           |          |          | MDC<     | :15:0>   |          |          |          |          |             |          | 0000          |

| STCON 0C        | C0E   | —                    | —      | Ι      | SESTAT | SEIEN  | EIPU      | SYNCPOL  | SYNCOEN  | SYNCEN   | SYNCSRC2 | SYNCSRC1 | SYNCSRC0 | SEVTPS3  | SEVTPS2  | SEVTPS1     | SEVTPS0  | 0000          |

| STCON2 0C       | C10   | —                    | —      | _      | _      | —      | —         | _        | _        |          |          | —        | —        | _        | F        | PCLKDIV<2:0 | >        | 0000          |

| STPER 0C        | C12   |                      |        |        |        |        |           |          |          | STPER    | <15:0>   |          |          |          |          |             |          | 0000          |

| SSEVTCMP 0C     | C14   |                      |        |        |        |        |           |          |          | SSEVTCI  | MP<15:0> |          |          |          |          |             |          | 0000          |

| CHOP 0C         | C1A C | CHPCLKEN             | —      | _      | _      | _      | —         | CHOPCLK9 | CHOPCLK8 | CHOPCLK7 | CHOPCLK6 | CHOPCLK5 | CHOPCLK4 | CHOPCLK3 | CHOPCLK2 | CHOPCLK1    | CHOPCLK0 | 0000          |

| PWMKEY 0C       | C1E   | 1E PWMKEY<15:0> 0000 |        |        |        |        |           |          |          |          |          |          | 0000     |          |          |             |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-9: **PWM GENERATOR 1 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15     | Bit 14      | Bit 13       | Bit 12     | Bit 11        | Bit 10    | Bit 9     | Bit 8     | Bit 7     | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|------------|-------------|--------------|------------|---------------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON1     | 0C20  | FLTSTAT    | CLSTAT      | TRGSTAT      | FLTIEN     | CLIEN         | TRGIEN    | ITB       | MDCS      | DTC1      | DTC0     | DTCP     | -        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON1      | 0C22  | PENH       | PENL        | POLH         | POLL       | PMOD1         | PMOD0     | OVRENH    | OVRENL    | OVRDAT1   | OVRDAT0  | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON1     | 0C24  | IFLTMOD    | CLSRC4      | CLSRC3       | CLSRC2     | CLSRC1        | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4   | FLTSRC3  | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC1        | 0C26  |            |             |              |            |               |           |           | PDC       | :1<15:0>  |          |          |          |          |          |          |          | FFF8          |

| PHASE1      | 0C28  |            |             |              |            |               |           |           | PHAS      | E1<15:0>  |          |          |          |          |          |          |          | 0000          |

| DTR1        | 0C2A  | _          | _           |              |            |               |           |           |           | DTR1      | l<13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR1     | 0C2C  | _          | _           |              |            |               |           |           |           | ALTDT     | R1<13:0> |          |          |          |          |          |          | 0000          |

| SDC1        | 0C2E  |            |             |              |            |               |           |           | SDC       | :1<15:0>  |          |          |          |          |          |          |          | 0000          |

| SPHASE1     | 0C30  |            |             |              |            |               |           |           | SPHAS     | SE1<15:0> |          |          |          |          |          |          |          | 0000          |

| TRIG1       | 0C32  |            |             |              |            |               |           |           | TRGC      | MP<15:0>  |          |          |          |          |          |          |          | 0000          |

| TRGCON1     | 0C34  | TRGDIV3    | TRGDIV2     | TRGDIV1      | TRGDIV0    | —             | —         | —         | _         | —         | —        | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP1     | 0C38  |            |             |              |            |               |           |           | PWMC      | AP1<15:0> |          |          |          |          |          |          |          | 0000          |

| LEBCON1     | 0C3A  | PHR        | PHF         | PLR          | PLF        | FLTLEBEN      | CLLEBEN   | —         | _         | —         | —        | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY1     | 0C3C  | _          | _           | _            | -          |               | •         | •         |           |           | LEB<     | <11:0>   |          |          | •        | •        | •        | 0000          |

| AUXCON1     | 0C3E  | _          | _           | _            | _          | BLANKSEL3     | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | —         | —        | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

| Legend:     | = u   | nimplement | ed, read as | s '0'. Reset | values are | shown in hexa | decimal.  | •         | •         |           | •        |          |          |          |          |          |          | <u> </u>      |

DS70000689D-page 57

| R/W-1        | R/W-0           | R/W-0                               | U-0        | U-0              | U-0              | U-0             | U-0    |

|--------------|-----------------|-------------------------------------|------------|------------------|------------------|-----------------|--------|

| GIE          | DISI            | SWTRAP                              |            | —                |                  | —               |        |

| bit 15       |                 |                                     |            |                  |                  |                 | bit 8  |

|              |                 |                                     |            |                  |                  |                 |        |

| U-0          | U-0             | U-0                                 | U-0        | U-0              | R/W-0            | R/W-0           | R/W-0  |

|              | —               | —                                   | —          | —                | INT2EP           | INT1EP          | INT0EP |

| bit 7        |                 |                                     |            |                  |                  |                 | bit 0  |

| 1            |                 |                                     |            |                  |                  |                 |        |

| Legend:      | 1- 1-14         |                                     | - :4       |                  |                  | (0)             |        |

| R = Readab   |                 | W = Writable I                      | JIC        | -                | mented bit, read |                 |        |

| -n = Value a | t POR           | '1' = Bit is set                    |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15       |                 | ntorrunt Enchla                     | hit        |                  |                  |                 |        |

| DIC 15       |                 | nterrupt Enable<br>and associate    |            | re enabled       |                  |                 |        |

|              |                 | are disabled, t                     |            |                  |                  |                 |        |

| bit 14       | DISI: DISI In   | struction Statu                     | s bit      |                  |                  |                 |        |

|              |                 | truction is active                  |            |                  |                  |                 |        |

|              |                 | truction is not a                   |            |                  |                  |                 |        |

| bit 13       |                 | oftware Trap Sta                    |            |                  |                  |                 |        |

|              |                 | trap is enabled<br>trap is disabled |            |                  |                  |                 |        |

| bit 12-3     |                 | ted: Read as '                      |            |                  |                  |                 |        |

| bit 2        | -               |                                     |            | t Polarity Selec | t bit            |                 |        |

|              |                 | on negative edg                     | •          | ,                |                  |                 |        |

|              | 0 = Interrupt o | on positive edg                     | e          |                  |                  |                 |        |

| bit 1        | INT1EP: Exte    | ernal Interrupt 1                   | Edge Detec | t Polarity Selec | t bit            |                 |        |

|              |                 | on negative edg                     |            |                  |                  |                 |        |

| bit 0        | INTOEP: Exte    | ernal Interrupt 0                   | Edge Detec | t Polarity Selec | t bit            |                 |        |

|              |                 | on negative edg                     |            |                  |                  |                 |        |

|              | 0 = Interrupt o | on positive edg                     | e          |                  |                  |                 |        |

|              |                 |                                     |            |                  |                  |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0           | R/W-0                                                         | R/W-0                               | R/W-0    | R/W-0             | R/W-0                        | R/W-0               | R/W-0        |  |  |  |  |  |

|-----------------|---------------------------------------------------------------|-------------------------------------|----------|-------------------|------------------------------|---------------------|--------------|--|--|--|--|--|

| T5MD            | T4MD                                                          | T3MD                                | T2MD     | T1MD              | QEI1MD                       | PWMMD               | DCIMD        |  |  |  |  |  |

| bit 15          |                                                               |                                     |          |                   |                              |                     | bit          |  |  |  |  |  |

| R/W-0           | R/W-0                                                         |                                     | R/W-0    | R/W-0             |                              | R/W-0               | R/W-0        |  |  |  |  |  |

|                 | -                                                             | R/W-0                               | -        | -                 | R/W-0<br>C2MD <sup>(1)</sup> | C1MD <sup>(1)</sup> | -            |  |  |  |  |  |

| l2C1MD<br>bit 7 | U2MD                                                          | U1MD                                | SPI2MD   | SPI1MD            | CZIVID                       | CIMDO               | AD1MD<br>bit |  |  |  |  |  |

|                 |                                                               |                                     |          |                   |                              |                     |              |  |  |  |  |  |

| Legend:         |                                                               |                                     |          |                   |                              |                     |              |  |  |  |  |  |

| R = Readabl     | e bit                                                         | W = Writable                        | bit      | U = Unimplen      | nented bit, rea              | d as '0'            |              |  |  |  |  |  |

| -n = Value at   | POR                                                           | '1' = Bit is set                    |          | '0' = Bit is clea | ared                         | x = Bit is unkn     | own          |  |  |  |  |  |

| bit 15          | TEMD. Timor                                                   | 5 Module Disal                      | alo hit  |                   |                              |                     |              |  |  |  |  |  |

| DIC 15          |                                                               | odule is disable                    |          |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | odule is enable                     |          |                   |                              |                     |              |  |  |  |  |  |

| bit 14          | T4MD: Timer                                                   | 4 Module Disal                      | ole bit  |                   |                              |                     |              |  |  |  |  |  |

|                 | 1 = Timer4 m                                                  | odule is disable                    | ed       |                   |                              |                     |              |  |  |  |  |  |

|                 | 0 = Timer4 m                                                  | odule is enable                     | ed       |                   |                              |                     |              |  |  |  |  |  |

| bit 13          | T3MD: Timer                                                   | 3 Module Disal                      | ole bit  |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | odule is disabl                     |          |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | odule is enable                     |          |                   |                              |                     |              |  |  |  |  |  |

| bit 12          | T2MD: Timer2 Module Disable bit                               |                                     |          |                   |                              |                     |              |  |  |  |  |  |

|                 | 1 = Timer2 module is disabled<br>0 = Timer2 module is enabled |                                     |          |                   |                              |                     |              |  |  |  |  |  |

| L:1 44          |                                                               |                                     |          |                   |                              |                     |              |  |  |  |  |  |

| bit 11          | _                                                             | 1 Module Disal                      |          |                   |                              |                     |              |  |  |  |  |  |

|                 | -                                                             | odule is disable<br>odule is enable |          |                   |                              |                     |              |  |  |  |  |  |

| bit 10          |                                                               | 11 Module Disa                      |          |                   |                              |                     |              |  |  |  |  |  |

| Sit 10          |                                                               | dule is disabled                    |          |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | dule is enabled                     |          |                   |                              |                     |              |  |  |  |  |  |

| bit 9           | PWMMD: PW                                                     | /M Module Dis                       | able bit |                   |                              |                     |              |  |  |  |  |  |

|                 | 1 = PWM mo                                                    | dule is disable                     | t        |                   |                              |                     |              |  |  |  |  |  |

|                 | 0 = PWM mo                                                    | dule is enabled                     | l        |                   |                              |                     |              |  |  |  |  |  |

| bit 8           | DCIMD: DCI                                                    | Module Disable                      | e bit    |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | ule is disabled                     |          |                   |                              |                     |              |  |  |  |  |  |

| bit 7           |                                                               | 1 Module Disal                      | ale hit  |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | lule is disabled                    |          |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | lule is enabled                     |          |                   |                              |                     |              |  |  |  |  |  |

| bit 6           | U2MD: UART                                                    | 2 Module Disa                       | ble bit  |                   |                              |                     |              |  |  |  |  |  |

|                 |                                                               | nodule is disabl                    |          |                   |                              |                     |              |  |  |  |  |  |

|                 | -                                                             | nodule is enable                    |          |                   |                              |                     |              |  |  |  |  |  |

| bit 5           | U1MD: UART                                                    | 1 Module Disa                       | ble bit  |                   |                              |                     |              |  |  |  |  |  |

|                 | 1 = UART1 m                                                   | nodule is disabl                    | ed       |                   |                              |                     |              |  |  |  |  |  |

|                 | 0 = UART1 m                                                   | odule is enabl                      | ed       |                   |                              |                     |              |  |  |  |  |  |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: These bits are available on dsPIC33EPXXXGM6XX/7XX devices only.

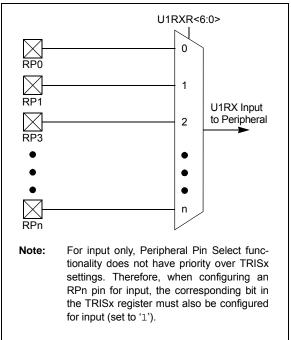

### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-29). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 26-1 in Section 26.0 "Op Amp/Comparator Module") and the PTG module (see Section 25.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual connections to the filtered QEIx module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module").

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEIx module allows peripherals to be connected to the QEIx digital filter input. To utilize this filter, the QEIx module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEIx digital filter.

## EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43

| RPINR15 = 0x2500;<br>RPINR7 = 0x009; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */ /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| QEI1IOC = 0x4000;                    | /* Enable the QEI digital filter */                                                                                       |

| QEI1CON = 0x8000;                    | /* Enable the QEI module */                                                                                               |

| U-0          | R/W-0                                      | R/W-0                                                                        | R/W-0     | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------------------------------------|------------------------------------------------------------------------------|-----------|-------------------|-----------------|-----------------|-------|

|              |                                            |                                                                              |           | C2RXR<6:0>        |                 |                 |       |

| bit 15       |                                            |                                                                              |           |                   |                 |                 | bit 8 |

|              |                                            |                                                                              |           |                   |                 |                 |       |

| U-0          | R/W-0                                      | R/W-0                                                                        | R/W-0     | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                                            |                                                                              |           | C1RXR<6:0>        |                 |                 |       |

| bit 7        |                                            |                                                                              |           |                   |                 |                 | bit ( |

|              |                                            |                                                                              |           |                   |                 |                 |       |

| Legend:      |                                            |                                                                              |           |                   |                 |                 |       |

| R = Readat   | ole bit                                    | W = Writable                                                                 | bit       | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR                                     | '1' = Bit is set                                                             |           | '0' = Bit is clea | ared            | x = Bit is unkr | iown  |

|              | 11111100 =  <br>•<br>•<br>•<br>•<br>•<br>• | 1-2 for input pin<br>nput tied to RPI<br>nput tied to CM<br>nput tied to Vss | 124<br>P1 | ,                 |                 |                 |       |

| bit 7        |                                            | nted: Read as '                                                              |           |                   |                 |                 |       |

| bit 6-0      | C10VD-6.0                                  | >: Assign CAN1                                                               |           |                   |                 | Do Dio hito     |       |

# REGISTER 11-20: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26<sup>(1)</sup>

Note 1: This register is not available on dsPIC33EPXXXGM3XX devices.

# dsPIC33EPXXXGM3XX/6XX/7XX

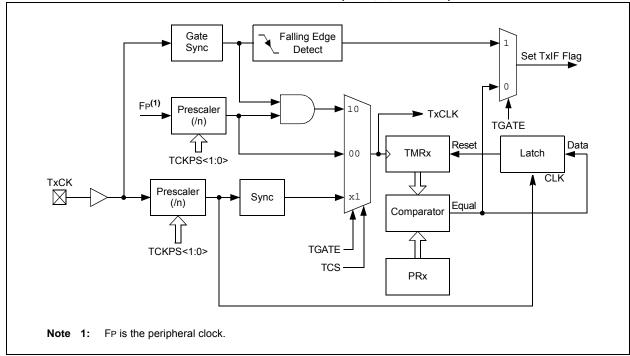

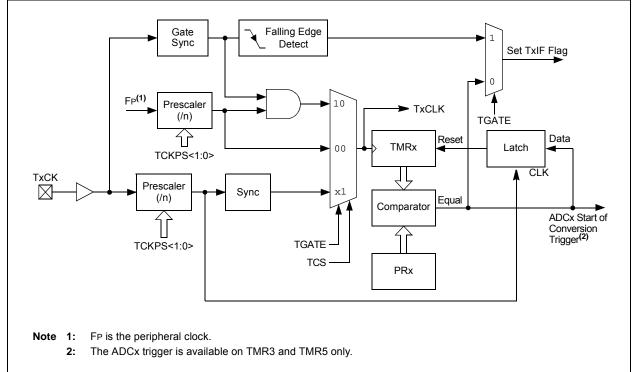

#### FIGURE 13-1: TYPE B TIMER BLOCK DIAGRAM (x = 2, 4, 6 AND 8)

#### U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 \_\_\_\_ \_\_\_\_ **BLANKSEL3 BLANKSEL2** BLANKSEL1 **BLANKSEL0** \_\_\_\_ \_\_\_\_ bit 15 bit 8 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 CHOPSEL2 CHOPSEL1 CHOPHEN CHOPSEL3 CHOPSEL0 CHOPLEN \_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15-12 Unimplemented: Read as '0' bit 11-8 BLANKSEL<3:0>: PWMx State Blank Source Select bits The selected state blank signal will block the current-limit and/or Fault input signals (if enabled via the BCH and BCL bits in the LEBCONx register). 1001 = Reserved 0110 = PWM6H is selected as state blank source 0101 = PWM5H is selected as state blank source 0100 = PWM4H is selected as state blank source 0011 = PWM3H is selected as state blank source 0010 = PWM2H is selected as state blank source 0001 = PWM1H is selected as state blank source 0000 = No state blanking bit 7-6 Unimplemented: Read as '0' bit 5-2 CHOPSEL<3:0>: PWMx Chop Clock Source Select bits The selected signal will enable and disable (CHOP) the selected PWMx outputs. 1001 = Reserved 0110 = PWM6H is selected as state blank source 0101 = PWM5H is selected as state blank source 0100 = PWM4H is selected as state blank source 0011 = PWM3H is selected as CHOP clock source 0010 = PWM2H is selected as CHOP clock source 0001 = PWM1H is selected as CHOP clock source 0000 = Chop clock generator is selected as CHOP clock source bit 1 CHOPHEN: PWMxH Output Chopping Enable bit 1 = PWMxH chopping function is enabled 0 = PWMxH chopping function is disabled bit 0 CHOPLEN: PWMxL Output Chopping Enable bit 1 = PWMxL chopping function is enabled 0 = PWMxL chopping function is disabled

#### REGISTER 16-24: AUXCONx: PWMx AUXILIARY CONTROL REGISTER

# REGISTER 17-10: INDXxHLD: INDEX COUNTER x HOLD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | INDXH | LD<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | INDXH | ILD<7:0>          |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 INDXHLD<15:0>: Holding Register for Reading and Writing INDXxCNT bits

# REGISTER 17-11: QEIXICH: QEIX INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-----------------|-----------|-------|--|--|

|                 |       |                  | QEIIC | <31:24>                                 |                 |           |       |  |  |

| bit 15          |       |                  |       |                                         |                 |           | bit 8 |  |  |

|                 |       |                  |       |                                         |                 |           |       |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0     | R/W-0 |  |  |

|                 |       |                  | QEIIC | 23:16>                                  |                 |           |       |  |  |

| bit 7           |       |                  |       |                                         |                 |           | bit C |  |  |

|                 |       |                  |       |                                         |                 |           |       |  |  |

| Legend:         |       |                  |       |                                         |                 |           |       |  |  |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen                            | nented bit, rea | ad as '0' |       |  |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |  |

bit 15-0 QEIIC<31:16>: High Word Used to Form 32-Bit Initialization/Capture Register (QEIxIC) bits

#### REGISTER 17-12: QEIxICL: QEIx INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | QEIIC | C<15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | QEII  | C<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| L               |       |                  |       |                   |                 |                 |       |

bit 15-0 QEIIC<15:0>: Low Word Used to Form 32-Bit Initialization/Capture Register (QEIxIC) bits

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> 111 = Secondary prescale 1:1

- 110 = Secondary prescale 2:1

- 000 = Secondary prescale 8:1

- bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)<sup>(3)</sup>

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

x = Bit is unknown

# REGISTER 25-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------|-------|-----------------|-------|--------------|------------------|----------|-------|

|                |       |                 | PTGA  | DJ<15:8>     |                  |          |       |

| bit 15         |       |                 |       |              |                  |          | bit 8 |

|                |       |                 |       |              |                  |          |       |

| R/W-0          | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                |       |                 | PTGA  | DJ<7:0>      |                  |          |       |

| bit 7          |       |                 |       |              |                  |          | bit 0 |

|                |       |                 |       |              |                  |          |       |

| Legend:        |       |                 |       |              |                  |          |       |

| R = Readable I | bit   | W = Writable bi | t     | U = Unimpler | mented bit, reac | l as '0' |       |

|                |       |                 |       |              |                  |          |       |

'0' = Bit is cleared

# REGISTER 25-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

'1' = Bit is set

-n = Value at POR

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PTGL0 | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGL  | 0<7:0> |       |       |       |

| bit 7  |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 **PTGL0<15:0>:** PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 register with the PTGADD command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

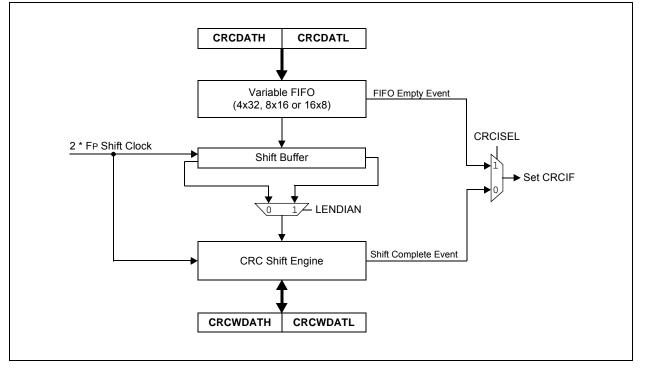

# 29.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS70346), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-Programmable (up to 32nd order) polynomial CRC equation

- Interrupt Output

- Data FIFO

The programmable CRC generator provides a hardware-implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 29-1. A simple version of the CRC shift engine is shown in Figure 29-2.

#### FIGURE 29-1: CRC BLOCK DIAGRAM

| Field                                                                                                                                          | Description                                                                                                                                                                                                                                                          |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Wm*Wm                                                                                                                                          | Multiplicand and Multiplier Working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |  |  |  |

| Wm*Wn       Multiplicand and Multiplier Working register pair for DSP instructions ∈         {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7} |                                                                                                                                                                                                                                                                      |  |  |  |

| Wn                                                                                                                                             | One of 16 Working registers ∈ {W0W15}                                                                                                                                                                                                                                |  |  |  |

| Wnd                                                                                                                                            | One of 16 Destination Working registers ∈ {W0W15}                                                                                                                                                                                                                    |  |  |  |

| Wns                                                                                                                                            | One of 16 Source Working registers ∈ {W0W15}                                                                                                                                                                                                                         |  |  |  |

| WREG                                                                                                                                           | W0 (Working register used in File register instructions)                                                                                                                                                                                                             |  |  |  |

| Ws                                                                                                                                             | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |  |  |  |

| Wso                                                                                                                                            | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |  |  |  |

| Wx                                                                                                                                             | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |  |  |  |

| Wxd                                                                                                                                            | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |  |  |  |

| Wy                                                                                                                                             | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |  |  |  |

| Wyd                                                                                                                                            | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |  |  |  |

#### TABLE 33-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT                   | ERISTICS            |      | (unless oth | the observation of the conditions: 3.0V to 3.6V to 3.6V otherwise stated)<br>of the temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |       |                                              |  |  |

|------------------------------|---------------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------|--|--|

| Parameter<br>No.             | Тур. <sup>(2)</sup> | Max. | Units       | Conditions                                                                                                                                                                                                 |       |                                              |  |  |

| Power-Down Current (IPD) (1) |                     |      |             |                                                                                                                                                                                                            |       |                                              |  |  |

| DC60d                        | 35                  | 100  | μA          | -40°C                                                                                                                                                                                                      |       | Base Power-Down Current                      |  |  |

| DC60c                        | 40                  | 200  | μA          | +25°C                                                                                                                                                                                                      | 3.3V  |                                              |  |  |

| DC60b                        | 250                 | 500  | μA          | +85°C                                                                                                                                                                                                      | 3.3V  |                                              |  |  |

| DC60c                        | 1000                | 2500 | μA          | +125°C                                                                                                                                                                                                     |       |                                              |  |  |

| DC61d                        | 8                   | 10   | μA          | -40°C                                                                                                                                                                                                      |       |                                              |  |  |

| DC61c                        | 10                  | 15   | μA          | +25°C                                                                                                                                                                                                      | 2 2)/ | Watchdog Timer Current: ΔIwDT <sup>(3)</sup> |  |  |

| DC61b                        | 12                  | 20   | μA          | +85°C                                                                                                                                                                                                      | 3.3V  |                                              |  |  |

| DC61c                        | 13                  | 25   | μA          | +125°C                                                                                                                                                                                                     |       |                                              |  |  |

Note 1: IPD (Sleep) current is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with

external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

ITAC is disabled

- JTAG is disabled

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise specified.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

# TABLE 33-21:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |    |                                                                                                             |  |  |

|--------------------|-----------|----------------------------------------------------------------|------|-------------------------------------------------------|------------|----|-------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min. | Тур. <sup>(2)</sup>                                   | Max. Units |    | Conditions                                                                                                  |  |  |

| SY00               | Τρυ       | Power-up Period                                                | _    | 400                                                   | 600        | μs |                                                                                                             |  |  |

| SY10               | Tost      | Oscillator Start-up Time                                       |      | 1024 Tosc                                             |            | _  | Tosc = OSC1 period                                                                                          |  |  |

| SY12               | Тwdt      | Watchdog Timer<br>Time-out Period                              | 0.85 | _                                                     | 1.15       | ms | WDTPRE = 0,<br>WDTPOST<3:0> = 0000,<br>Using LPRC tolerances indicated<br>in F21 (see Table 33-19) at +85°C |  |  |

|                    |           |                                                                | 3.4  | _                                                     | 4.6        | ms | WDTPRE = 1,<br>WDTPOST<3:0> = 0000,<br>Using LPRC tolerances indicated<br>in F21 (see Table 33-19) at +85°C |  |  |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | 0.68 | 0.72                                                  | 1.2        | μs |                                                                                                             |  |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2    | —                                                     | _          | μs |                                                                                                             |  |  |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1    | _                                                     |            | μs |                                                                                                             |  |  |

| SY35               | TFSCM     | Fail-Safe Clock Monitor<br>Delay                               | _    | 500                                                   | 900        | μs | -40°C to +85°C                                                                                              |  |  |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active Mode<br>Transition Time |      | —                                                     | 30         | μs |                                                                                                             |  |  |

| SY37               | TOSCDFRC  | FRC Oscillator Start-up<br>Delay                               | _    | —                                                     | 29         | μs |                                                                                                             |  |  |

| SY38               | TOSCDLPRC | LPRC Oscillator Start-up<br>Delay                              |      | —                                                     | 70         | μs |                                                                                                             |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

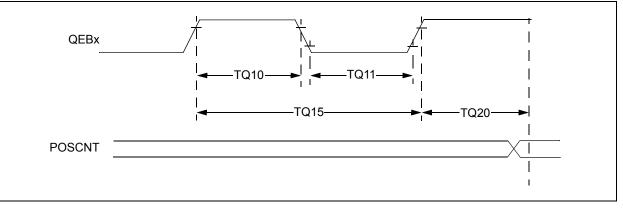

### FIGURE 33-12: TIMERQ (QEIX MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS

#### TABLE 33-29: QEIX MODULE EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СН/       | ARACTERIS | STICS                                                        | S Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extend |                                                 |      |      |       |                                  |

|--------------|-----------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|------|-------|----------------------------------|

| Param<br>No. | Symbol    | Characteristic <sup>(1)</sup>                                |                                                                                                                                                                                                                | Min.                                            | Тур. | Max. | Units | Conditions                       |

| TQ10         | TtQH      | TQCK High<br>Time                                            | Synchronous,<br>with Prescaler                                                                                                                                                                                 | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 | —    | _    | ns    | Must also meet<br>Parameter TQ15 |

| TQ11         | TtQL      | TQCK Low<br>Time                                             | Synchronous,<br>with Prescaler                                                                                                                                                                                 | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 | —    | _    | ns    | Must also meet<br>Parameter TQ15 |

| TQ15         | TtQP      | TQCP Input<br>Period                                         | Synchronous,<br>with Prescaler                                                                                                                                                                                 | Greater of:<br>25 + 50 or<br>(1 Tcy/N) + 50     | —    | _    | ns    |                                  |

| TQ20         | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                                                                | _                                               | 1    | Тсү  | —     |                                  |

Note 1: These parameters are characterized but not tested in manufacturing.

| TABLE 33-40: SPIT MAXIMUM DATA/CLOCK RATE SUMMARY | TABLE 33-40: | SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY |

|---------------------------------------------------|--------------|--------------------------------------|

|---------------------------------------------------|--------------|--------------------------------------|

| AC CHARA             | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                            | CKE | СКР | SMP |  |

| 25 MHz               | Table 33-41                              |                                             | _                                                                                                                                                                                                                                                                                     | 0,1 | 0,1 | 0,1 |  |

| 25 MHz               | —                                        | Table 33-42                                 | —                                                                                                                                                                                                                                                                                     | 1   | 0,1 | 1   |  |

| 25 MHz               | —                                        | Table 33-43                                 | —                                                                                                                                                                                                                                                                                     | 0   | 0,1 | 1   |  |

| 25 MHz               | —                                        | —                                           | Table 33-44                                                                                                                                                                                                                                                                           | 1   | 0   | 0   |  |

| 25 MHz               | —                                        | —                                           | Table 33-45                                                                                                                                                                                                                                                                           | 1   | 1   | 0   |  |

| 25 MHz               | _                                        | _                                           | Table 33-46                                                                                                                                                                                                                                                                           | 0   | 1   | 0   |  |

| 25 MHz               | _                                        | _                                           | Table 33-47                                                                                                                                                                                                                                                                           | 0   | 0   | 0   |  |

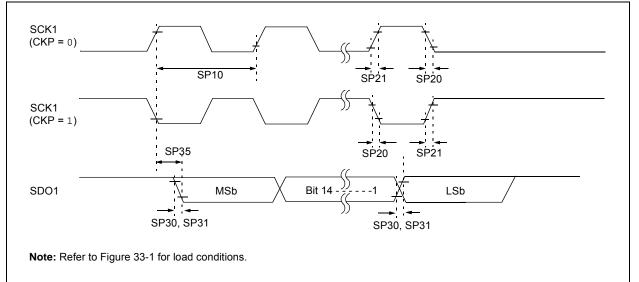

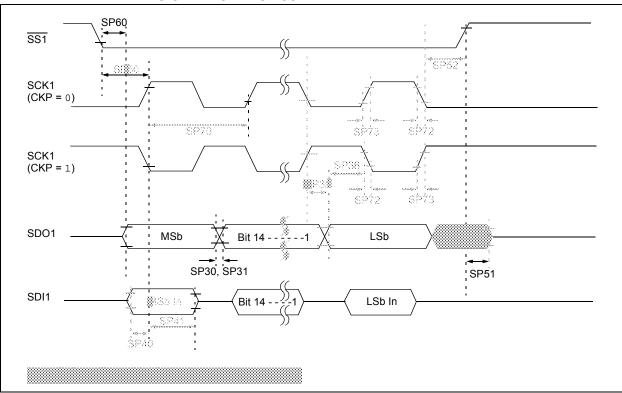

## FIGURE 33-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

#### FIGURE 33-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS |        |                                                             |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |      |       |                                            |  |

|--------------------|--------|-------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|

| Param.             | Symbol | Characteristic                                              | Min. | Тур.                                                                                                                                   | Max. | Units | Conditions                                 |  |

| HDO10              | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>    |      | —                                                                                                                                      | 0.4  | V     | IOL ≤ 5 mA, VDD = 3.3V<br>(Note 1)         |  |